2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

日本工業規格 JIS

C 5610-1996

集積回路用語

Glossary of terms used in integrated circuits

1. 適用範囲 この規格は,集積回路に用いる主な用語の定義について規定する。

2. 用語の分類 集積回路に関する用語の分類は,次による。

(1) 基本関連

(2) デバイス関連

(3) プロセス関連

(4) 組立,実装関連

(5) 信頼性関連

(6) 設計,回路関連

3. 参考規格 この規格の参考規格を,次に示す。

備考 角括弧“[ ]”は,対応する国際規格を示す。

JIS B 0153-1985 機械振動・衝撃用語 [ISO 1925, 2041]

JIS B 0155-1986 工業プロセス計測制御用語

JIS B 3000-1990 FA用語

JIS C 5600-1977 電子通信用語(基礎編)

JIS C 5603-1993 プリント回路用語 [ISO 194]

JIS C 7102-1973 電子管用語 [IEC 134]

JIS C 8500-1996 一次電池通則 [IEC 86-1]

JIS D 0103-1982 自動車用電装部品の名称に関する用語

JIS K 6900-1994 プラスチック−用語 [ISO 472]

JIS X 0011-1989 情報処理用語(処理装置) [ISO 2382-11]

JIS X 0012-1990 情報処理用語(データ媒体,記憶装置及び関連装置) [ISO 2382-12]

JIS X 3001-1994 プログラム言語Fortran [ISO/IEC 1539]

JIS X 6261-1991 130mm追記形光ディスクカートリッジ [ISO/IEC 9171-1〜2]

JIS Z 2500-1987 粉末や(冶)金用語 [ISO 3252]

JIS Z 6000-1996 マイクログラフィックス用語 [ISO 6196-1〜5, 6196-7]

JIS Z 8113-1988 照明用語 [IEC 50 (845)]

JIS Z 8120-1986 光学用語

JIS Z 8141-1983 生産管理用語(基本)

IEC 748-1 : 1984 Semiconductor devices Integrated circuits Part 1 : General

2

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4. 集積回路用語 主な用語について,次のように定める。

備考 定義の表記方法は,次による。

なお,読み方及び対応英語は参考とする。

1. 番号に関する表記方法

(1) 番号は4けたの数字によって表す。

(2) 最初の2けたの数字は,この規格における用語の分類の番号を表し,次の2けたの数字は,

この分類の同一区分での一連番号である。

2. 用語及び読み方に関する表記方法は,次による。

(1) 同一の意味を表す用語が二つ以上ある場合は,その順序に従って優先使用する。

(2) 一つの用語が2行にわたる場合は,2行目を1文字下げる。

(3) 定義での丸括弧“( )”は説明などに使用する。

(4) 省略してもよいものは,角括弧“[ ]”の中に記述する。

(5) 説明用の文は,用語の後のゴシック体角括弧“【 】”の中に記述する。

(6) 定義は,その用語が他の日本工業規格に規定されている場合は,参考として規格番号を示

す。

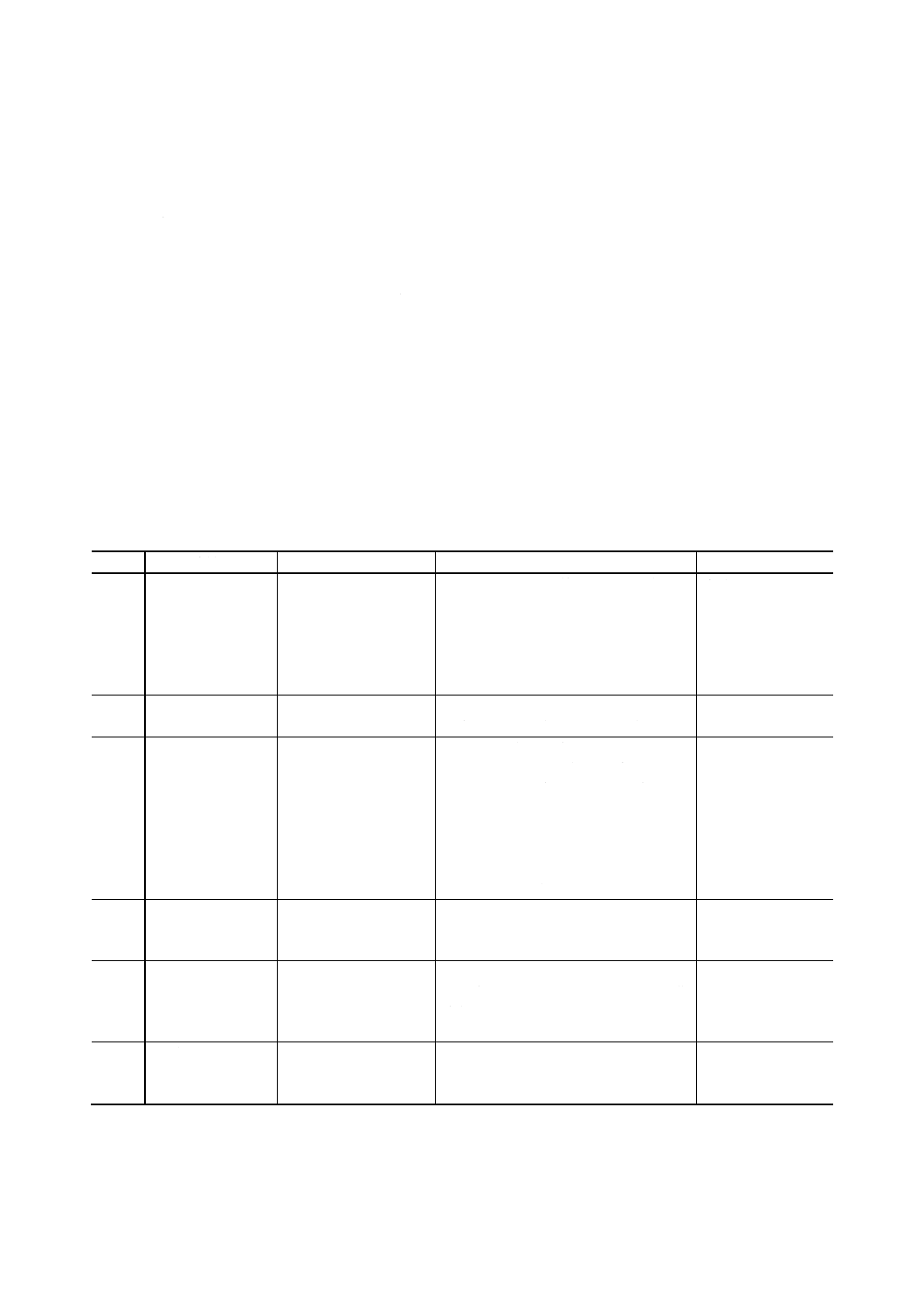

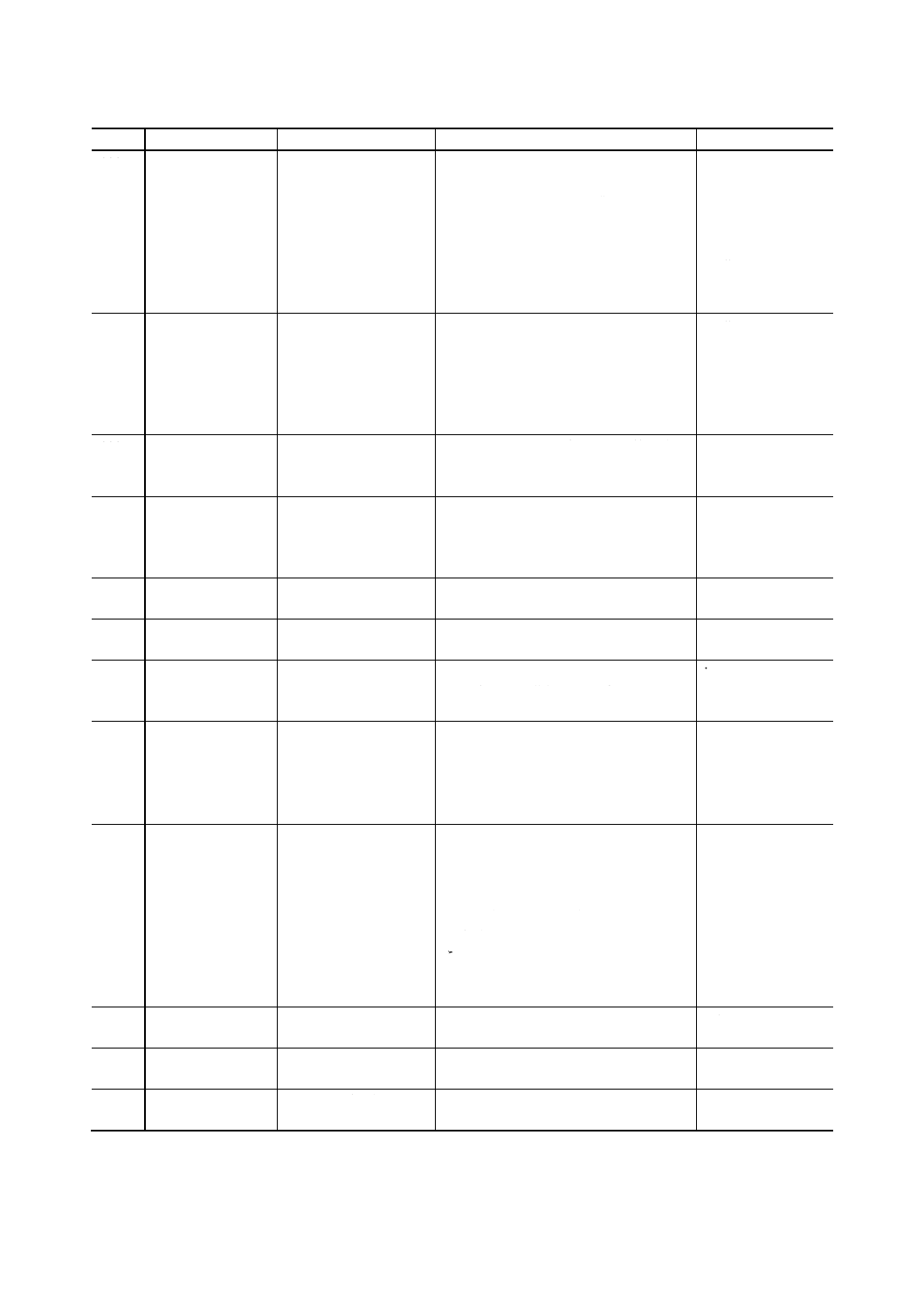

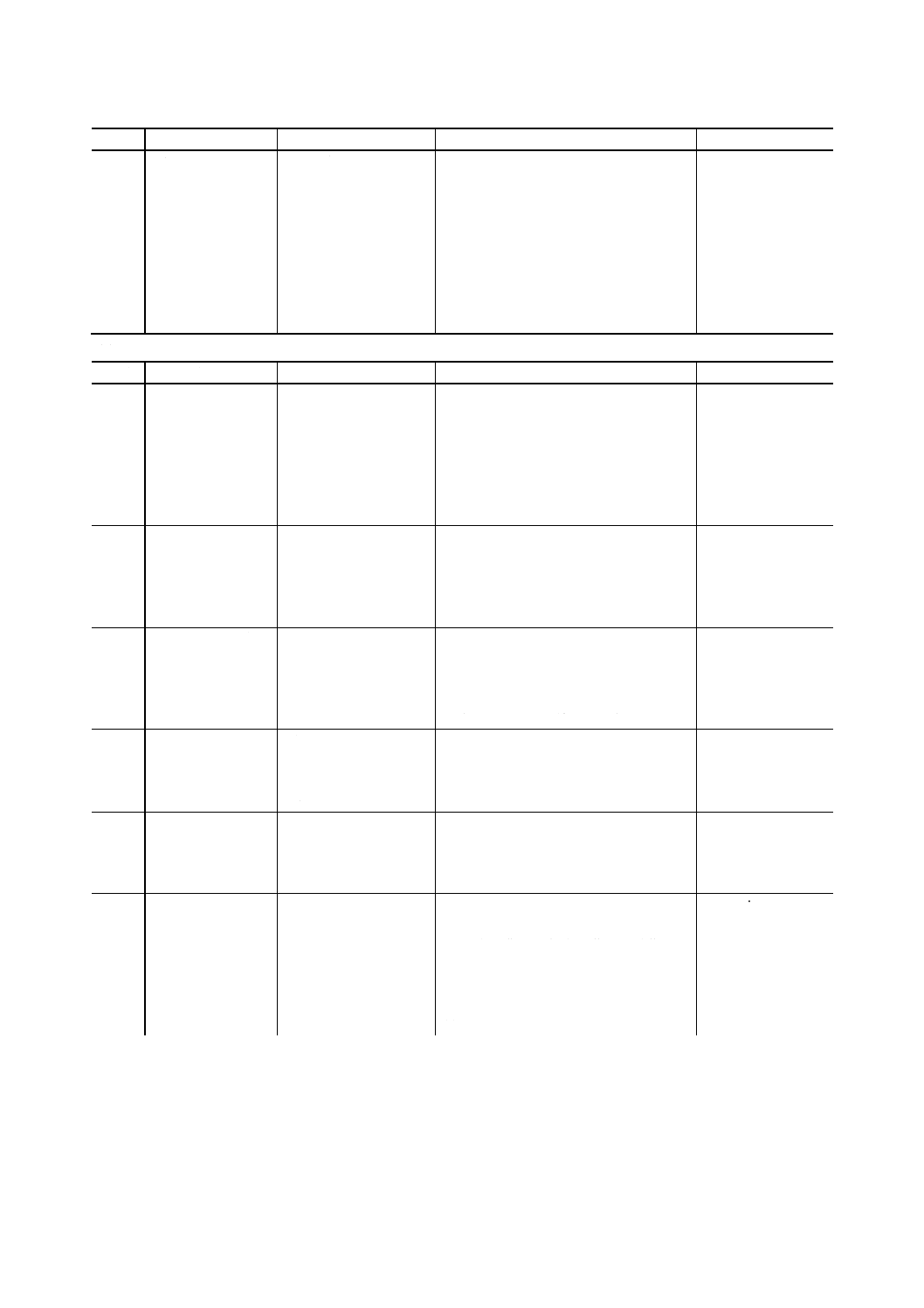

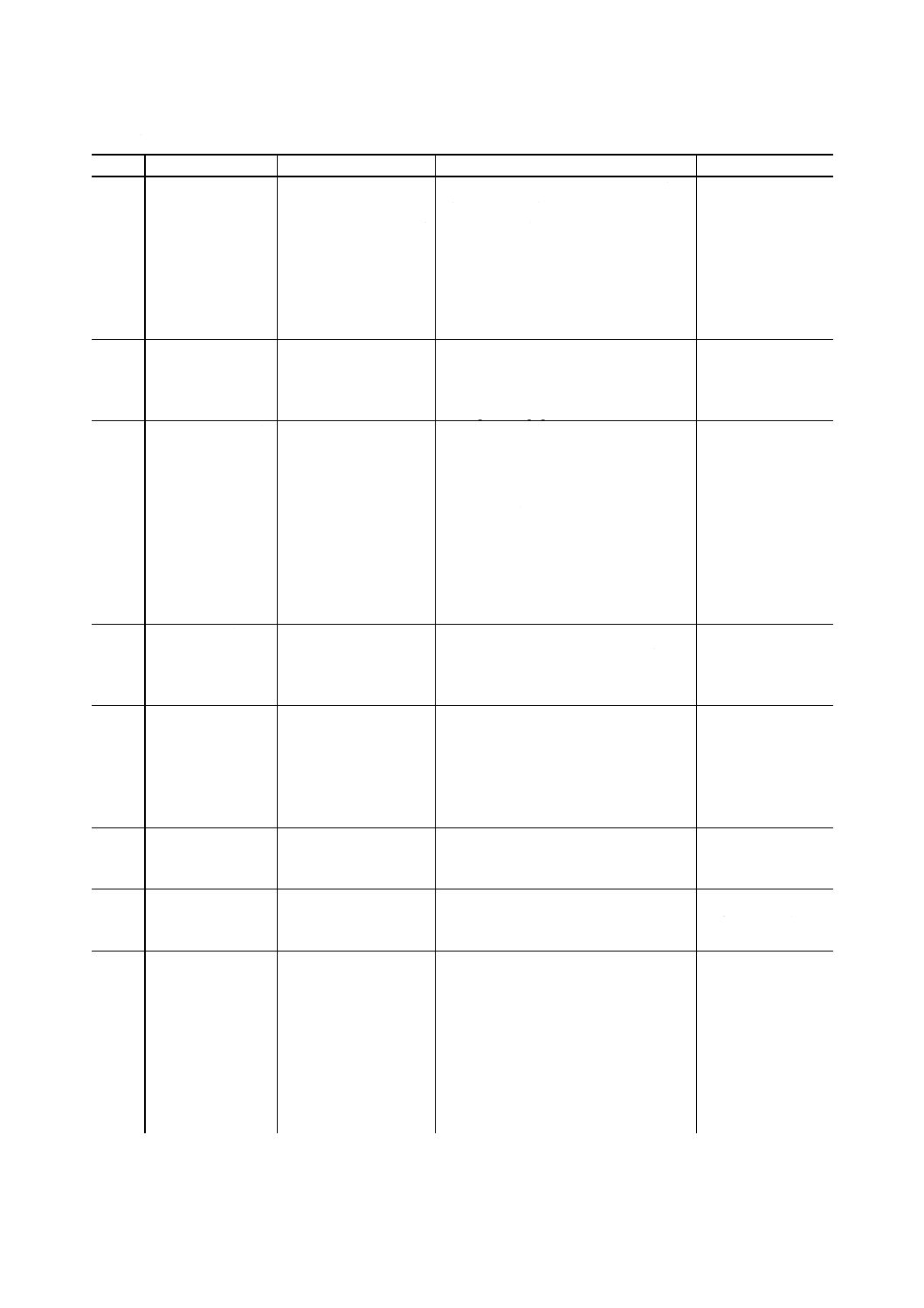

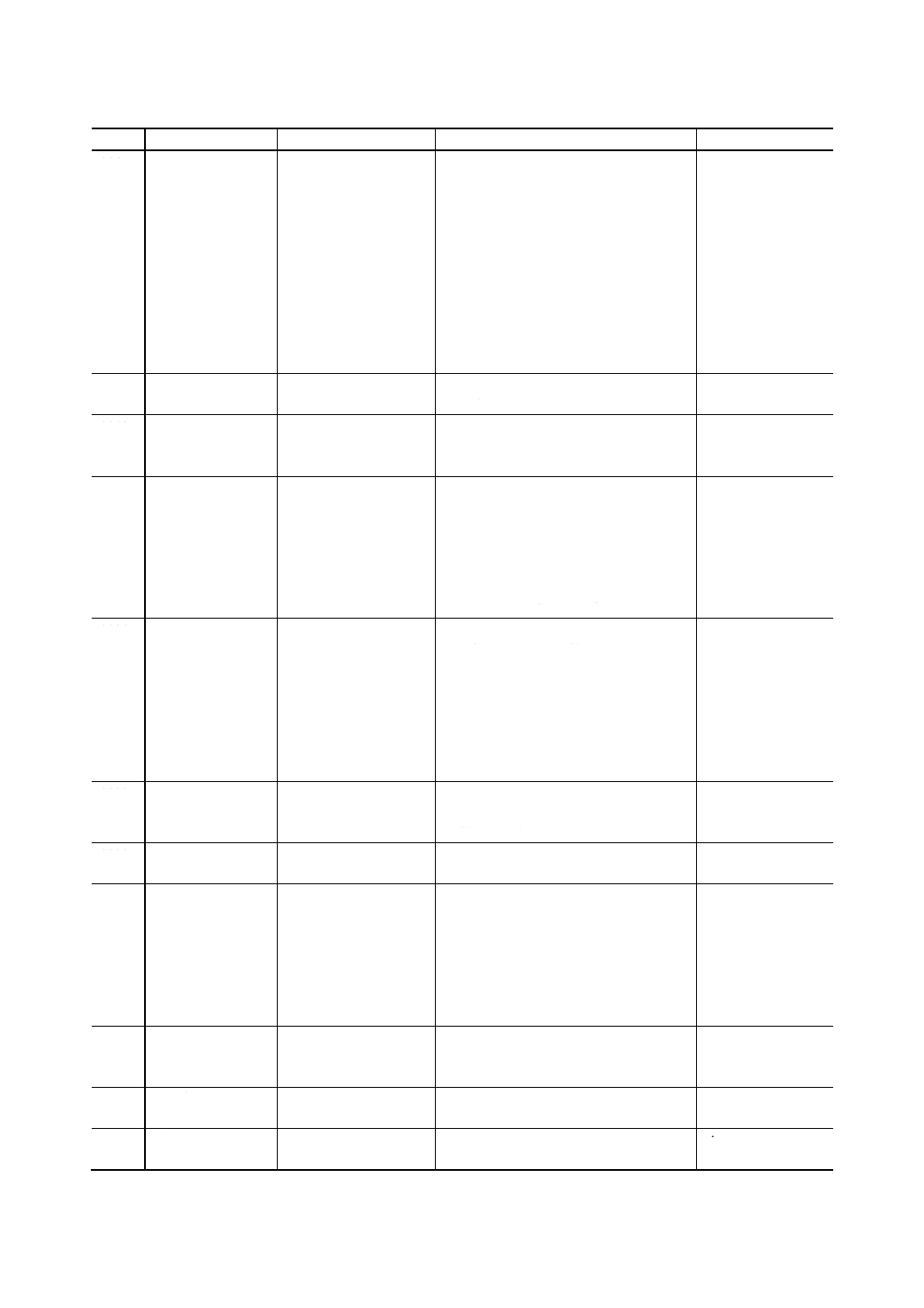

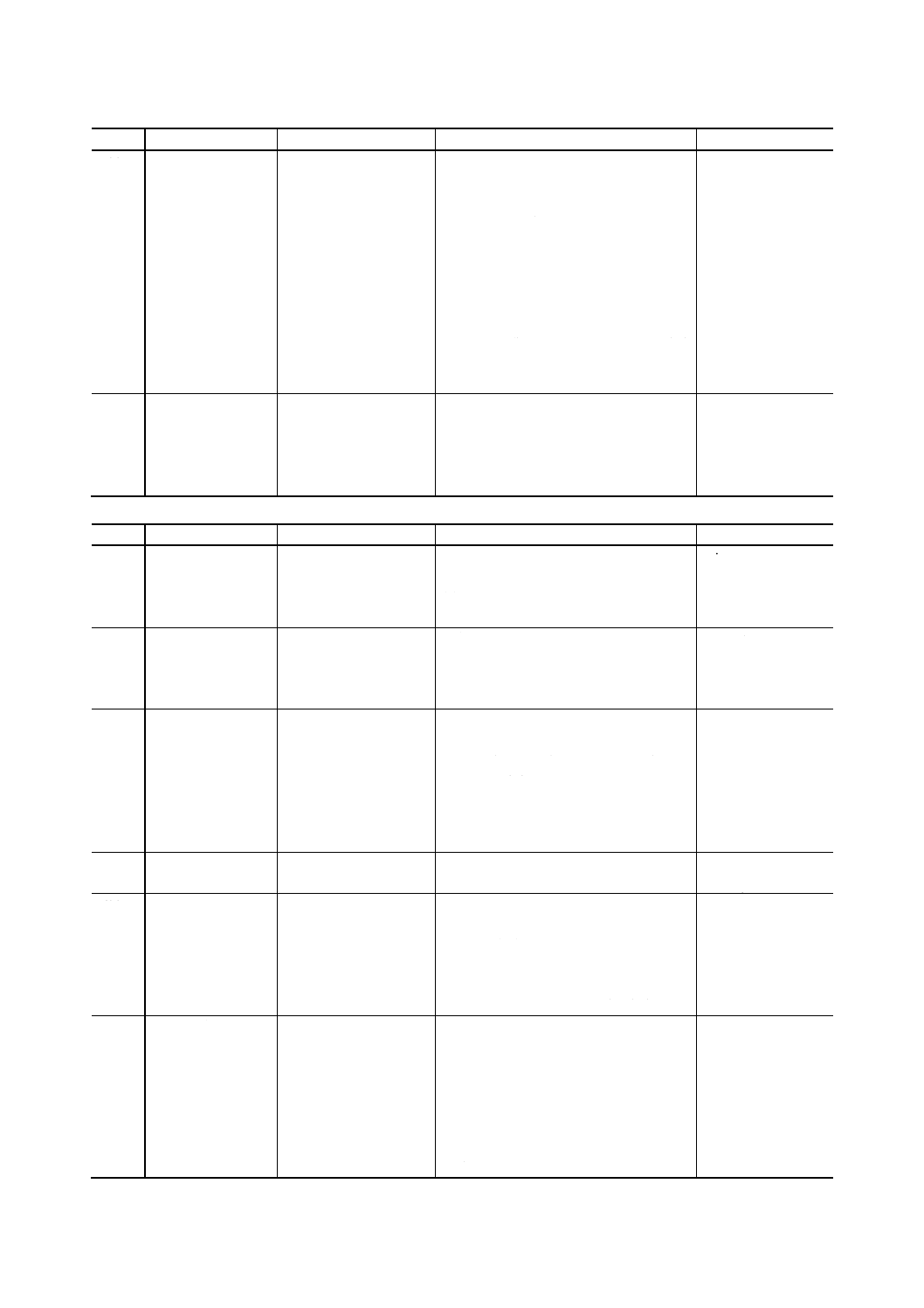

(1) 基本関連用語

番号

用語

読み方(参考)

定義

対応英語(参考)

1001

デバイス

能動的機能,非直線的機能,変換機能

などのような特殊な機能をもつ部品又

は装置。

参考 例えば,トランジスタ,ダイ

オード,メモリデバイスなど

をいう。

device

1002

素子

そし

部品又は装置を一つの機能としてみた

場合,その機能体を構成する単位。

element

1003

部品

ぶひん

一つの機能体を構成する部分。

備考 特に機能体の構成部分とい

う意味を強く表す場合に“構

成部品”という用語が用いら

れる。

参考 例えば,トランジスタ,コン

デンサ,スイッチ,ねじなど

をいう。

part

component

1004

回路

かいろ

素子の機能を結合して所要の信号及び

(又は)エネルギー処理機能をもたせ

たもの。

circuit

1005

システム

幾つかの回路,デバイス,部品などを

組み合わせ,必要な機能を実現した集

合体で,これを機能面からみたときの

呼称。

system

1006

サブシステム

システムの一部で,その部分的機能を

もっているもの。

参考 JIS B 0155参照。

subsystem

3

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

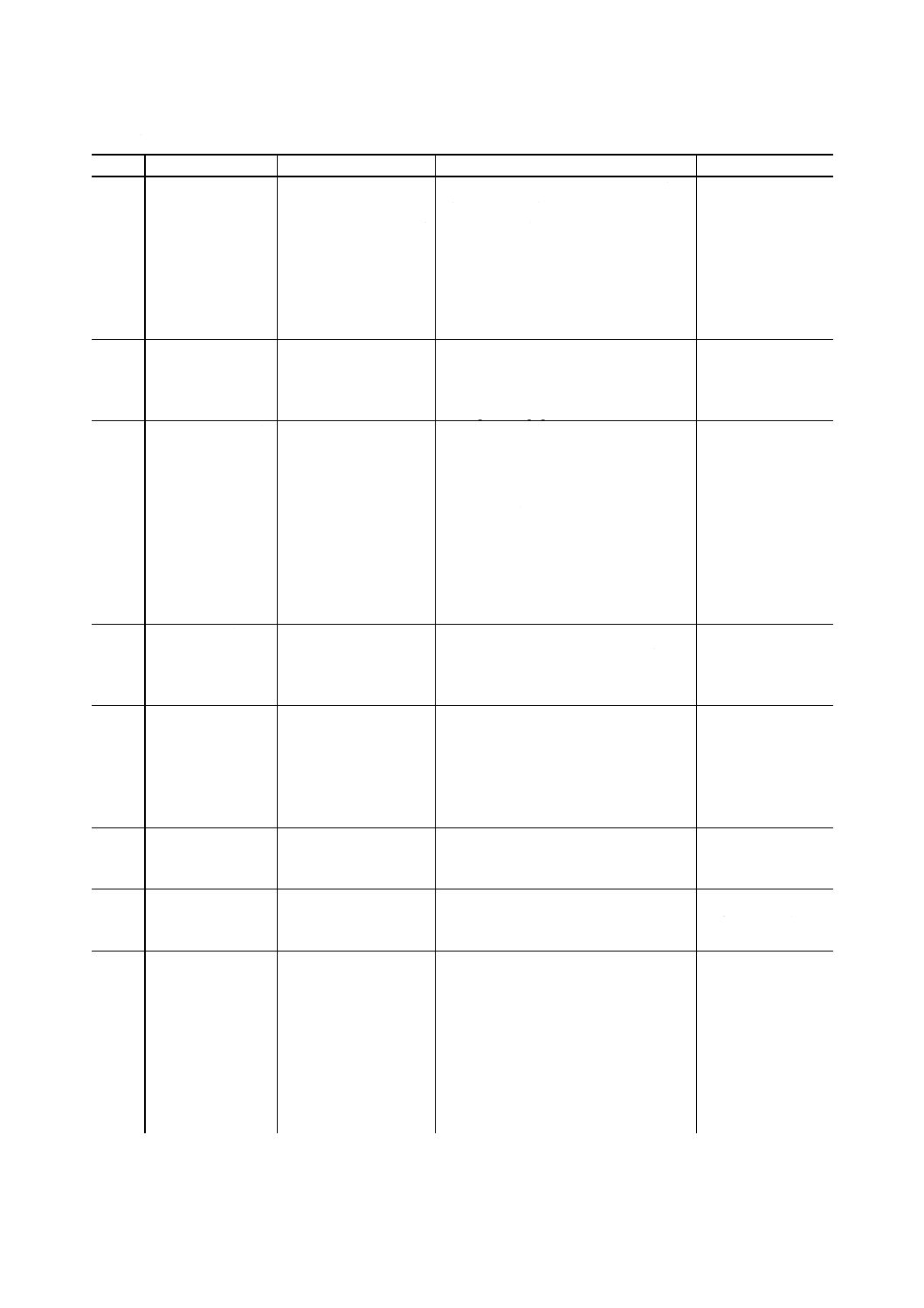

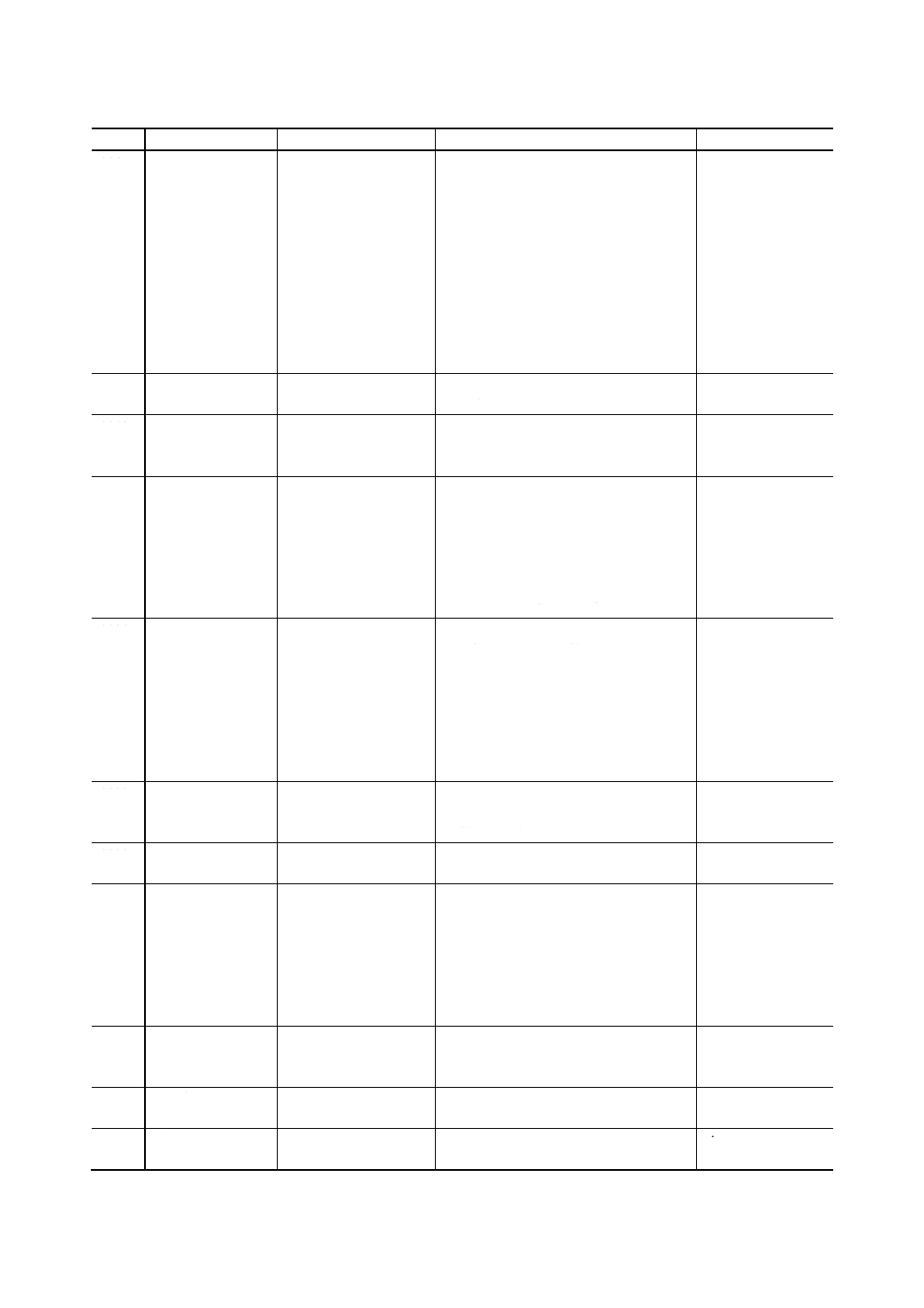

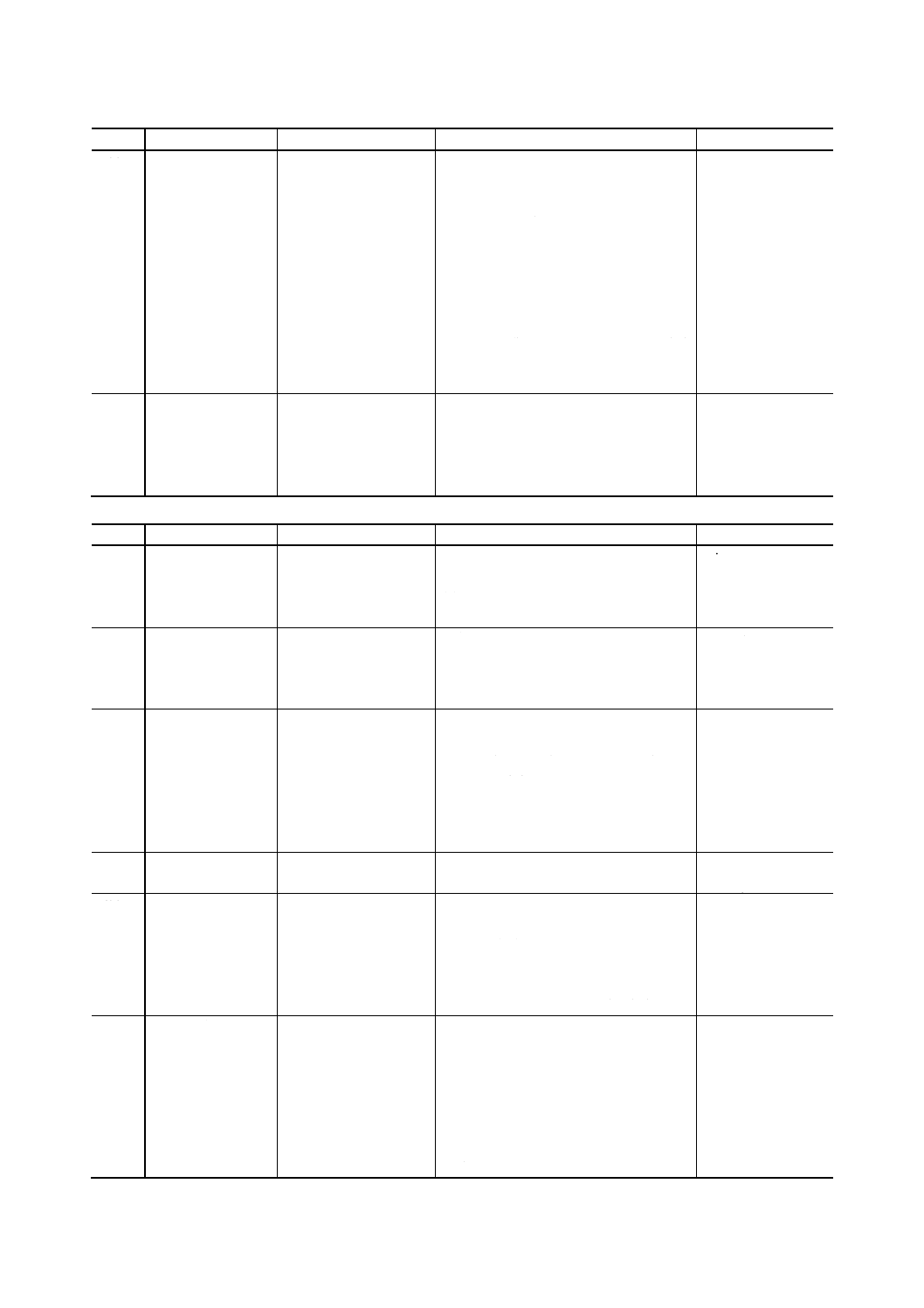

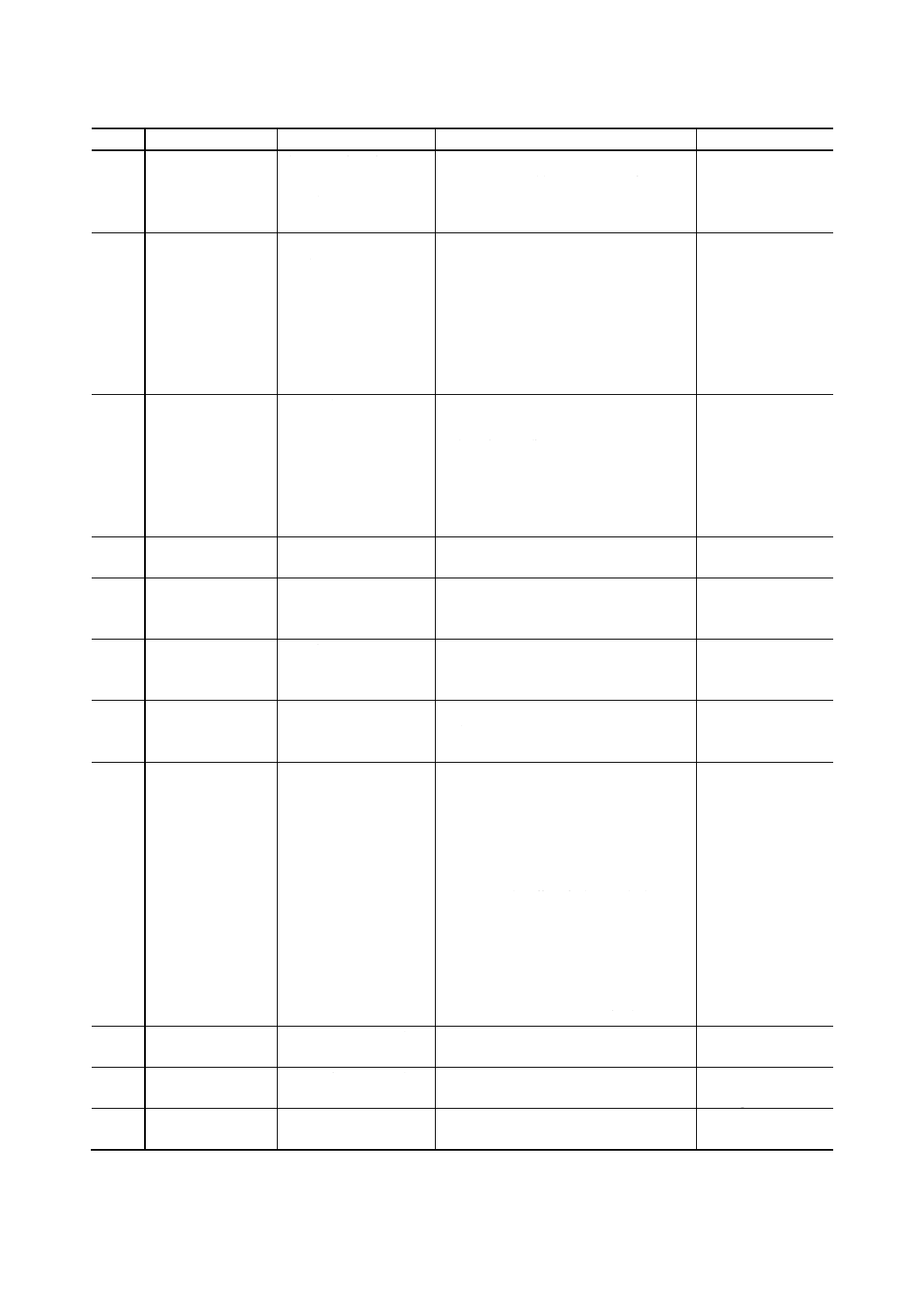

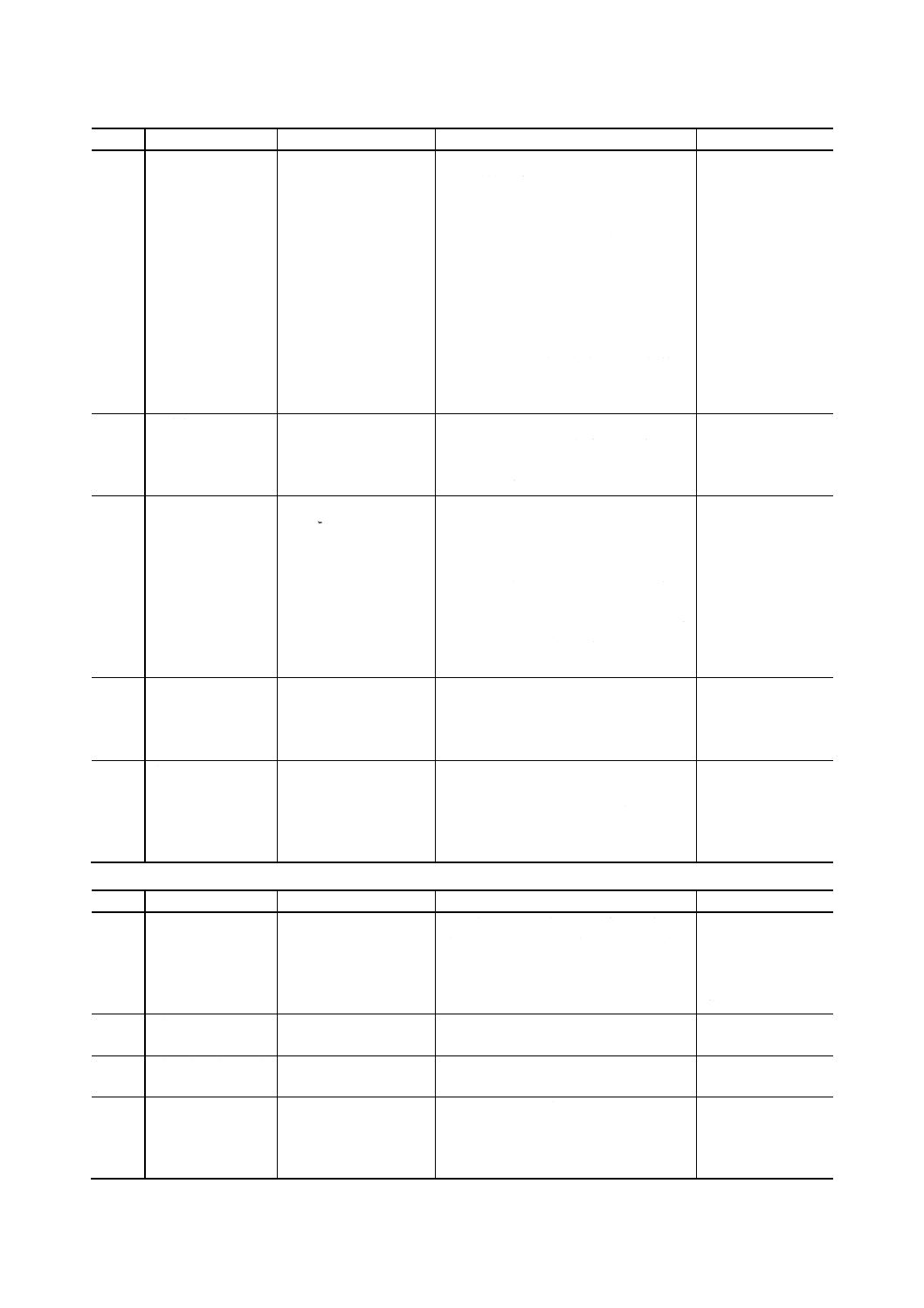

(2) デバイス関連用語

番号

用語

読み方(参考)

定義

対応英語(参考)

2001

マイクロエレクト

ロニクス

超小形電子技術

まいくろえれくとろに

くす

ちょうこがたでんしぎ

じゅつ

一般に得られるよりも小形化の程度が

進んだ電子回路を実現,又はその利用

に関連した技術の総称。

備考 関連用語として“超小形電子

工学”,“超小形電子方式”,

“超小形電子系”,“超小形

電子回路”,“超小形構成部

分”などがある。

microelectronics

2002

バイポーラトラン

ジスタ

電子と正孔がともに動作に関与する3

端子のデバイス。エミッタ,ベース,

コレクタと呼ばれる三つの領域からな

り,npn又はpnpの2種類がある。

bipolar transistor

2003

電界効果トランジ

スタ

FET

でんかいこうかとらん

じすた

えふいーてぃー

電流通路(チャネル)のコンダクタン

スをゲート電極から横方向の電界によ

って制御するトランジスタ。

備考 ゲート構造によって,“接合

形FET (JFET)”,“金属・酸化

物・半導体FET (MOSFET)”,

“金属・半導体

FET

(MESFET) (“ショットキー

バリアゲートFET”ともい

う。)”などに分けられる。

field-effect transistor

2004

薄膜トランジスタ

TFT

はくまくとらんじすた

てぃーえふてぃー

絶縁体基板上に半導体薄膜を形成し,

その膜内にチャネルを設けて,絶縁ゲ

ート電界効果トランジスタとしたも

の。

thin film transistor

2005

MIS[構造]

えむあいえす[こうぞ

う]

金属 (metal) と半導体 (semiconductor)

との間に薄い絶縁物 (insulator) を挿入

した構造。

参考 電界効果トランジスタ,電界

発光素子,ジョセフソン素子

などに用いられる。

metal-insulator-semi

conductor

2006

MOS[構造]

えむおーえす[こうぞ

う]

MIS構造のうち,絶縁物が半導体を構

成する原子の酸化物 (oxide) であるも

の。

metal-oxide-semicon

ductor

2007

MOSキャパシタ

えむおーえすきゃぱし

た

もすきゃぱした

MOS構造を用いたキャパシタ。

metal-oxide-semicon

ductor capacitor

2008

MOSFET

えむおーえすえふいー

てぃー

もすえふいーてぃー

MOS構造の金属(ゲート)直下の酸化

膜・半導体界面の反転層をチャネルと

し,ここのキャリア数をゲート電圧で

制御することによってチャネルの面に

沿ったコンダクタンスを制御する電界

効果トランジスタ。

備考 チャネル反転層がn形のもの

をn-MOSFET,p形のものを

p-MOSFETという。

metal-oxide-semicon

ductor field-effect

transistor

4

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

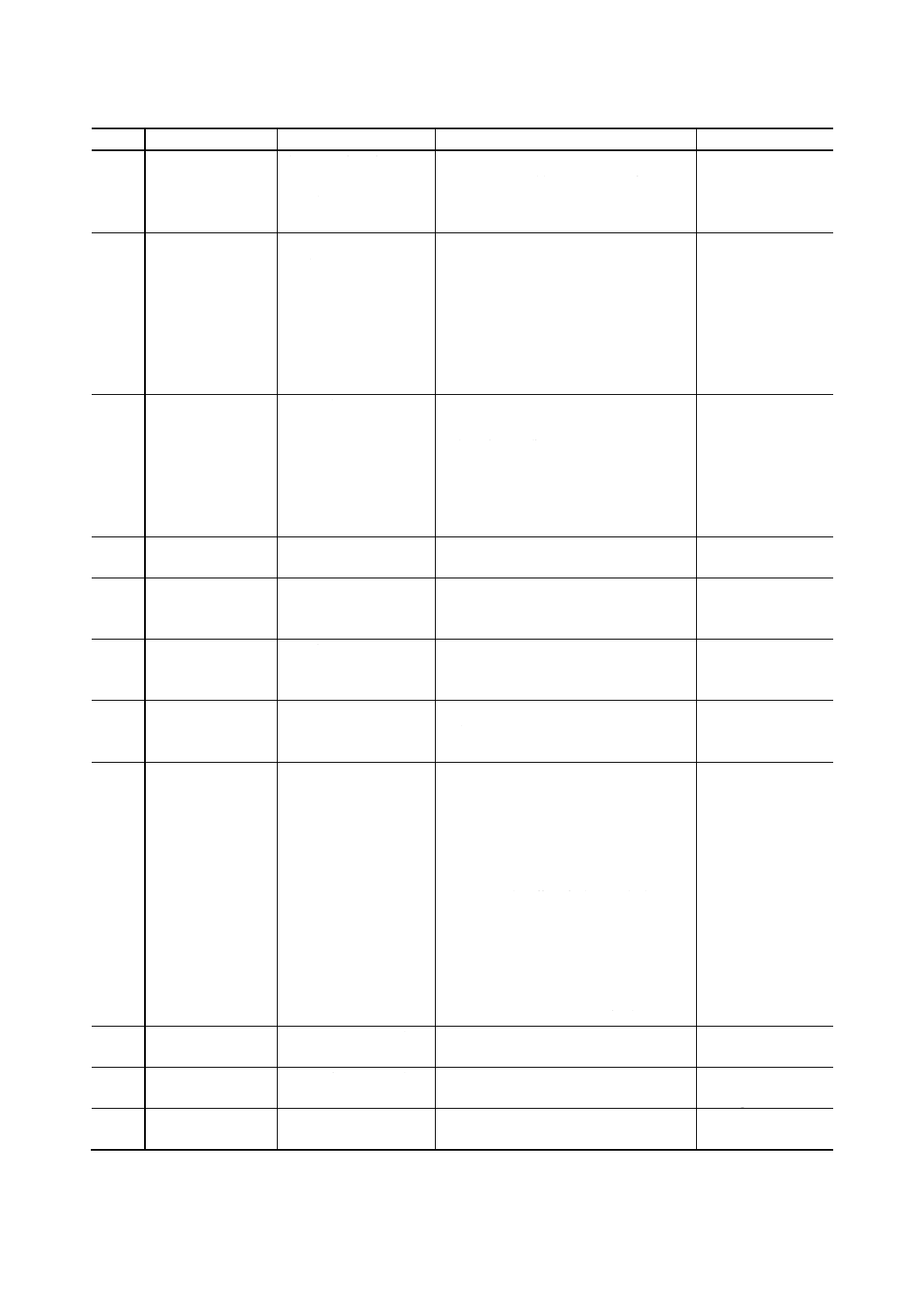

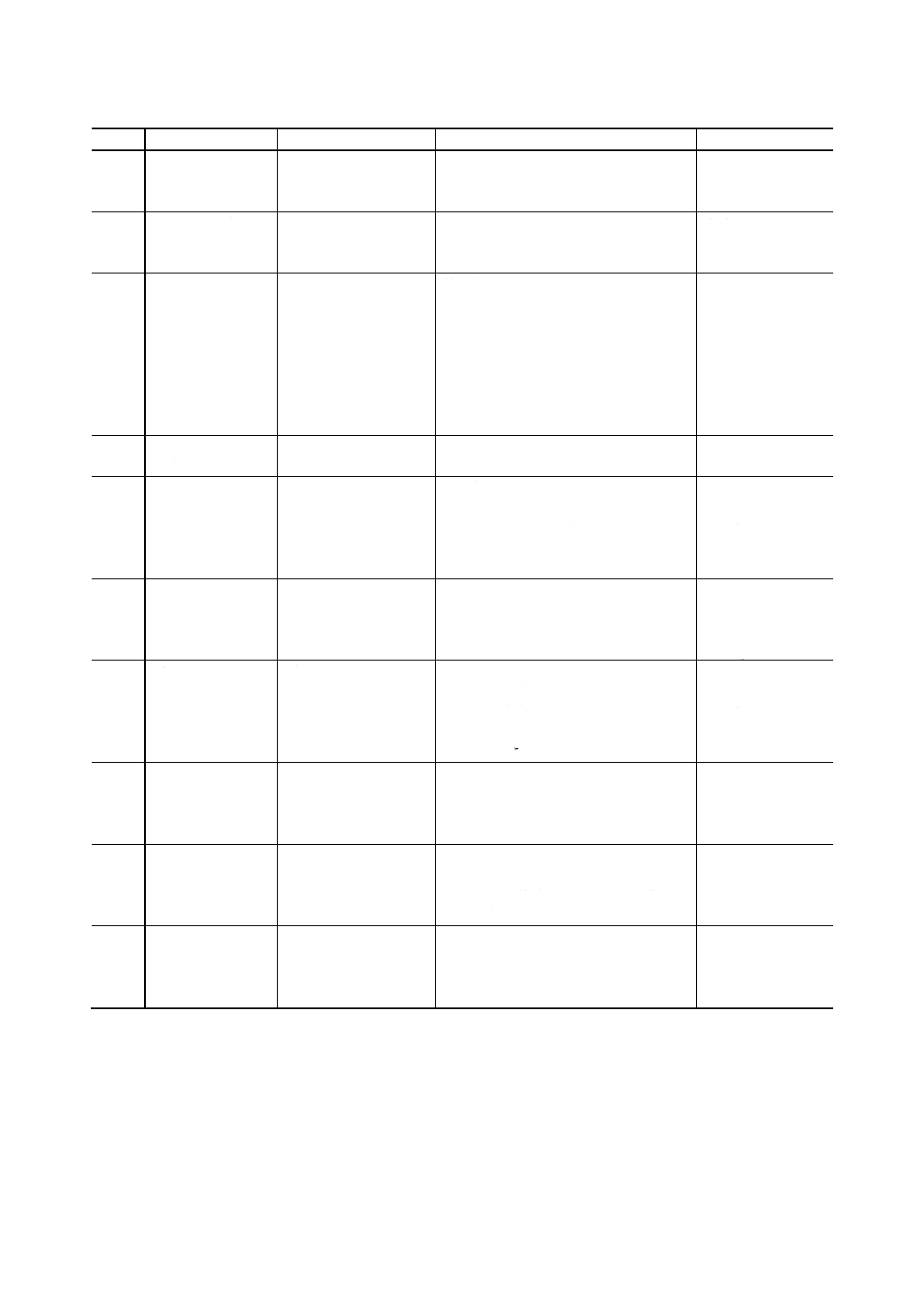

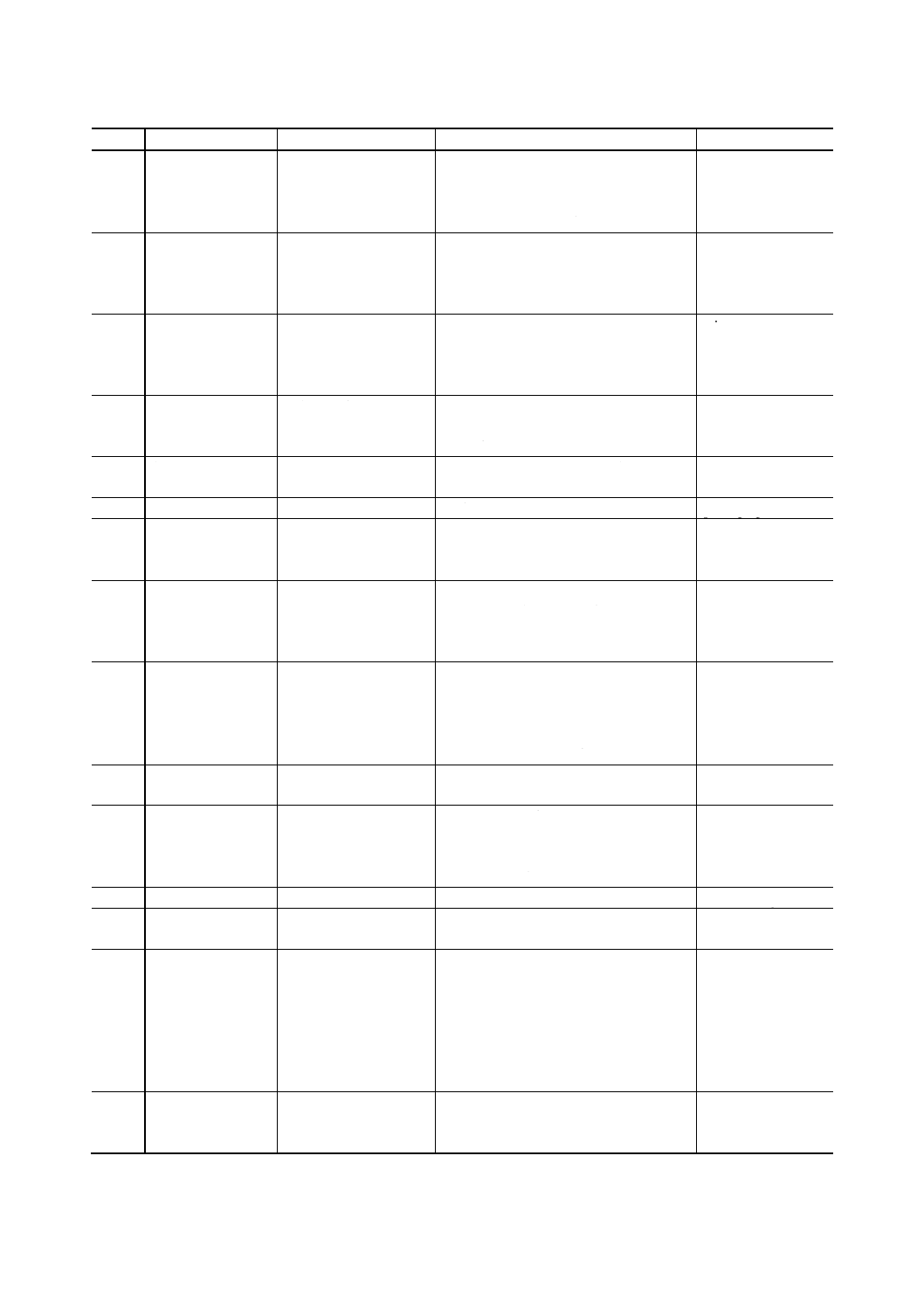

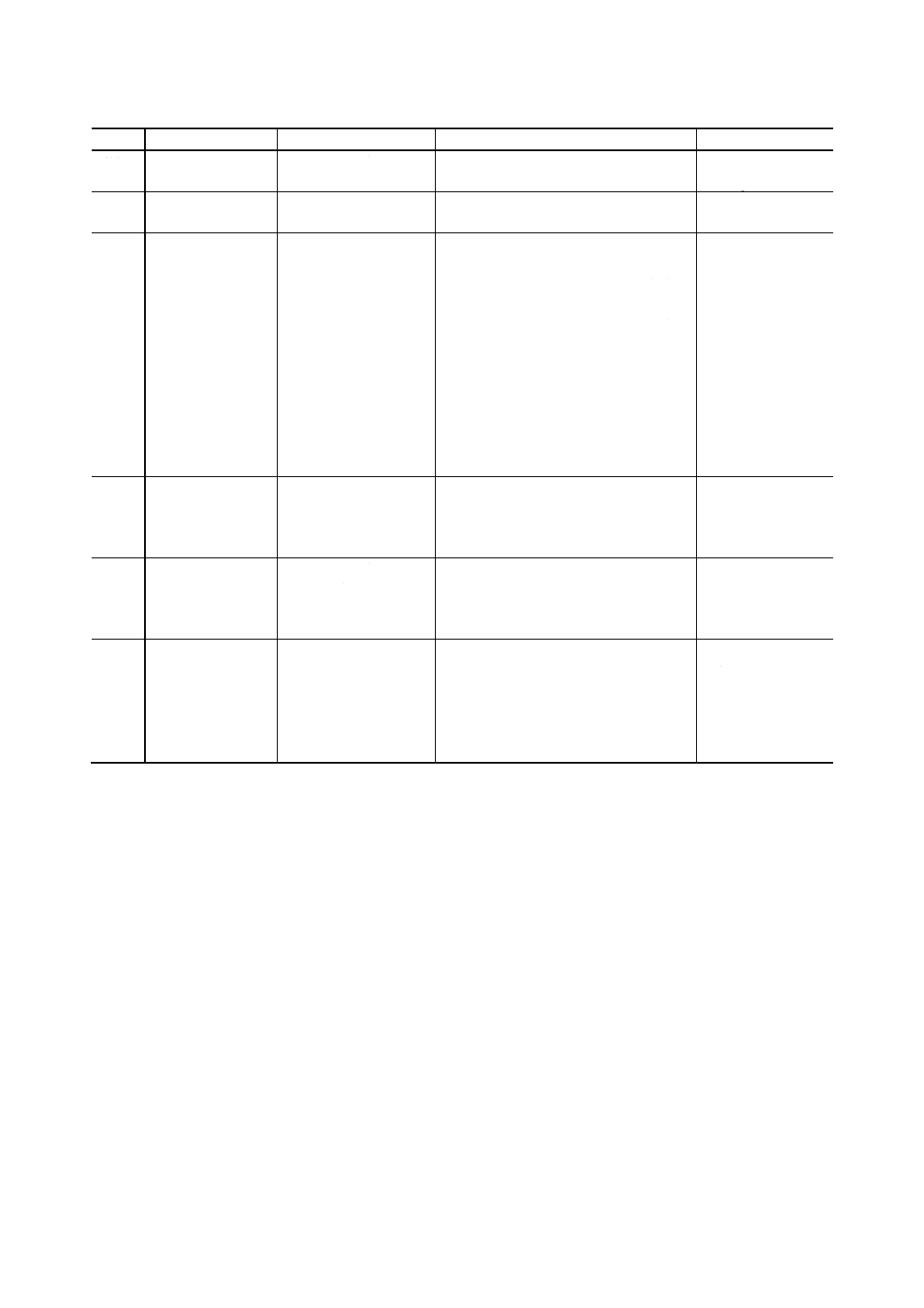

番号

用語

読み方(参考)

定義

対応英語(参考)

2009

MISFET

えむあいえすえふいー

てぃー

みすえふいーてぃー

ゲートをMIS構造で構成した,MOSFET

と同じ原理の電界効果トランジスタ。

metal-insulator-semi

conductor

field-effect

transistor

2010

MESFET

えむいーえすえふいー

てぃー

ゲート領域にショットキー障壁を設

け,そのショットキー障壁を逆バイア

スして空乏層の幅を変え,キャリアの

流れを制御する電界効果トランジス

タ。

備考 “金属・半導体FET”,“ショ

ットキーバリアゲートFET”

ともいう。

metal-electrode

semiconductor

field-effect

transistor

2011

JFET

じぇいえふいーてぃー

ゲート領域にpn接合を設け,そのpn

接合を逆バイアスし,ゲート直下の空

乏層の幅を制御することによってドレ

イン電流を制御する電界効果トランジ

スタ。

備考 “接合形電界効果トランジ

スタ”ともいう。

junction field-effect

transistor

2012

薄膜【集積回路技

術での】

はくまく

基板上に真空蒸着,イオンスパッタリ

ングなどによって得られる膜。

thin film

2013

厚膜【集積回路技

術での】

あつまく

基板上にインク状ペーストなどを塗布

し,スプレイ又は印刷した後,焼き付

ける方法などによって得られる膜。

thick film

2014

集積化

IC化

しゅうせきか

あいしーか

数多くの回路機能を一つにまとめ,よ

り大きな機能をもたせるようにするこ

と。

integration

2015

集積回路

IC

しゅうせきかいろ

あいしー

数多くの超小形素子が一つの基板上に

一体的に作り込まれている回路。

参考 JIS D 0103参照。

integrated circuit

2016

大規模集積回路

LSI

だいきぼしゅうせきか

いろ

えるえすあい

チップ当たりに多数の部品を集積化し

た集積回路。

参考 LSIの本来の対応英語は

large-scale integrationで大規

模集積化を意味する。集積度

の増加に伴い,歴史的にSSI

(small-scale integration),MSI

(medium-scale integration),

LSI,VLSI (very-large-scale

integration)

,

ULSI

(ultra-large-scale

integration)

という用語が使用されてき

た。JIS D 0103参照。

large-scale integrated

circuit

2017

モノリシック集積

回路

ものりしっくしゅうせ

きかいろ

1個の半導体のチップ内に作られた集

積回路。

monolithic integrated

circuit

2018

半導体集積回路

はんどうたいしゅうせ

きかいろ

半導体素子を主体として作られている

集積回路。

semiconductor

integrated circuit

2019

膜集積回路

まくしゅうせきかいろ

薄膜集積回路と厚膜集積回路の総称。

film integrated

circuit

5

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

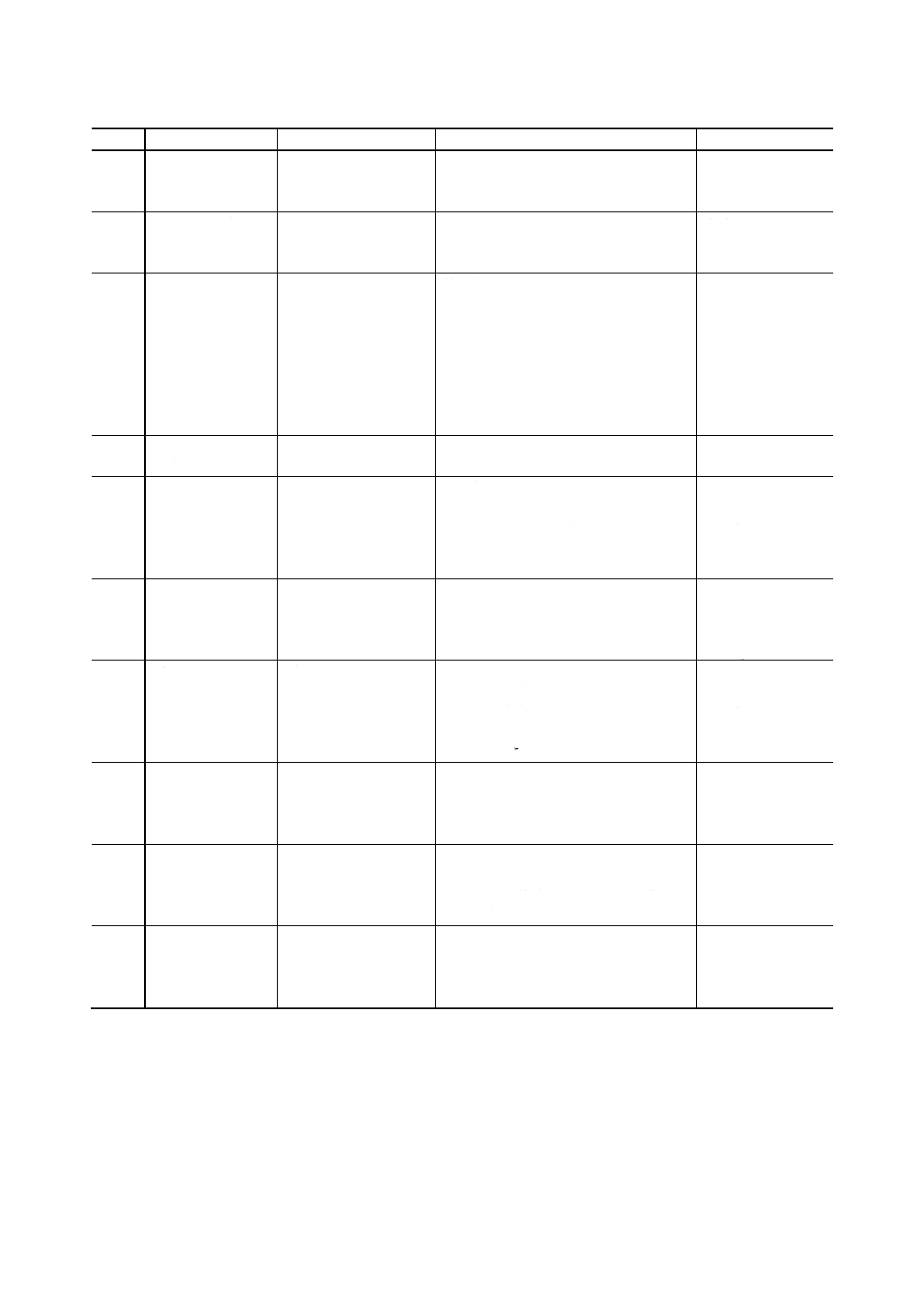

番号

用語

読み方(参考)

定義

対応英語(参考)

2020

薄膜集積回路

はくまくしゅうせきか

いろ

基板上に構成された回路素子とその相

互接続が薄膜から成り立った集積回

路。

thin film integrated

circuit

2021

厚膜集積回路

あつまくしゅうせきか

いろ

基板上に構成された回路素子とその相

互接続が厚膜から成り立った集積回

路。

thick film integrated

circuit

2022

マルチチップモジ

ュール

MCM

まるちちっぷもじゅー

る

えむしーえむ

複数個のLSIチップなどをセラミック

基板などに直接実装し,一つの機能に

まとめたモジュール又はパッケージ。

各モジュールの寸法,端子などの大き

さや形を標準化し,製作,組立を容易

にし,実装密度,性能の向上が図れる。

備考 広義には,ハイブリッドIC

も含まれる。

multichip module

2023

バイポーラ集積回

路

ばいぽーらしゅうせき

かいろ

バイポーラの素子で構成される半導体

集積回路。

bipolar integrated

circuit

2024

CMOS

しーもす

基本的なインバータ回路がp-MOSと

n-MOSの一対で構成され,両者が入力

に対して互いに相補的にスイッチング

する構造の回路方式。

備考 “相補形MOS”ともいう。

complementary

metal-oxide-semic

onductor

2025

CMOS集積回路

しーもすしゅうせきか

いろ

CMOSを主体として構成された集積回

路。

complementary

metal-oxide-semic

onductor

integrated circuit

2026

BiMOS

ばいもす

バイポーラ素子とMOS素子とを同一チ

ップ上に混載して,互いの長所を生か

す回路構成方式。

備考 “バイポーラMOS”ともい

う。

bipolar

metal-oxide-semic

onductor

2027

BiCMOS

ばいしーもす

バイポーラ素子とCMOS素子とを同一

チップ上に混載した回路構成方式。

備考 “バイポーラCMOS”ともい

う。

bipolar

complementary

metal-oxide-semic

onductor

2028

SOI

えすおーあい

高集積度,高速動作及び各種の特性改

善をめざして,絶縁性基板ウェーハ上

にシリコン薄膜を設け,ここに集積回

路を形成する構造。

silicon on insulator

2029

半導体メモリ

はんどうたいめもり

情報を一時的,又は長期的に記憶する

機能をもつ半導体デバイス。

参考 MOSメモリ,バイポーラメ

モリなどがある。

semiconductor

memory

6

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

2030

ランダムアクセス

メモリ

RAM

らんだむあくせすめも

り

らむ

メモリセルがマトリックス状に配置さ

れ,その場所に無関係にランダムにア

クセスして読出し,書込みがほぼ同等

の速度でできるメモリ装置。

備考 “随時書込み読出しメモリ”

ともいう。集積回路では,記

憶内容が無限時間保持がで

き,記憶保持動作が不要な

“スタティックRAM

(SRAM)”と,ある一定時間

ごとに記憶内容をリフレッ

シュする必要のある記憶保

持動作が必要な“ダイナミッ

クRAM (DRAM)”とがある。

参考 DRAMは,一つのセルがアク

セス用のMOSFETと記憶用

のMOSキャパシタからなる

簡単な構成で実現でき,低消

費電力,高密度化の特徴をも

つ。JIS X 0012参照。

random-access

memory

static random-access

memory

dynamic

random-access

memory

2031

リードオンリーメ

モリ

ROM

りーどおんりーめもり

ろむ

読出し専用の半導体メモリで,あらか

じめ書き込んである情報を読み出すこ

とだけに使用する。この情報は電源を

切っても失われることはない。

備考 “読出し専用メモリ”ともい

う。

参考 JIS X 0012参照。

read only memory

2032

プログラマブル

ROM

PROM

ぷろぐらまぶるろむ

ぴーろむ

ユーザが自由にデータを書き込み,プ

ログラムすることのできるROM。

備考 ヒューズを用いたバイポー

ラ形,MOS構造の酸化膜の

中に設けたフローティング

ゲートに電荷を蓄積する

MOS形及び“MNOS”構造

のシリコン窒化膜とシリコ

ン酸化膜の界面準位に電荷

を蓄積するMNOS形がある。

バイポーラ形では1回限りの

書込みで,消去と書換えはで

きないが,MOS形とMNOS

形では消去と書換えができ

る。さらに,MOS形とMNOS

形で,書込みを電気的に,消

去を紫外線で行う

“EPROM”,書込みと消去を

電気的に行う“EEPROM”と

がある。

参考 JIS X 0012参照。

programmable read

only memory

metal-nitride-oxide-s

emiconductor

erasable and

programmable

read only memory

electrically erasable

and programmable

read only memory

7

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

2033

フラッシュメモリ

メモリの内容を一括して消去し,再書

込みができるメモリ。

備考 紫外線で消去するものに対

し,電気的に消去するものを

いう。

flash memory

2034

イメージセンサ

光電変換,信号電荷の蓄積,走査の三

つの基本的機能をもつ光学的な画像情

報を電気的な信号に変換するデバイ

ス。

image sensor

2035

機能デバイス

きのうでばいす

電磁現象に限らず,熱,光,機械振動

及びその他の物理・化学現象を利用し

て,所要の信号及び(又は)エネルギ

ーの処理,変換などを目的とする機能

をもたせたデバイス。

functional device

2036

機能ブロック

きのうぶろっく

システム,サブシステムなどを構成す

るブロックであって,そのシステムに

必要な機能を果たすもの。

functional block

2037

混成集積回路

ハイブリッドIC

こんせいしゅうせきか

いろ

はいぶりっどあいしー

二つ以上の異種の集積回路の組合せ,

又は一つ以上の独立したテバイス若し

くは部品と一つ以上の集積回路とから

なる回路。

参考 JIS D 0103参照。

hybrid integrated

circuit

2038

発光ダイオード

LED

はっこうだいおーど

えるいーでぃー

pn接合を設けた半導体に電流を流し,

電子と正孔の発光再結合によって自然

放出光を放出するダイオード。

参考 光の波長は半導体材料のバ

ンドギャップで決まり,その

スペクトルはレーザに比べ

て広い。

light emitting diode

2039

レーザダイオード

LD

れーざだいおーど

えるでぃー

pn接合と光共振器を設けた半導体に電

流を流すことによって,レーザ光線を

発生させるpn接合ダイオード。

参考 実用上,発振効率のよい活性

層をクラッド層で挟んだダ

ブルヘテロ接合構造のもの

が使われる。発光する方向に

よって,活性層に平行な方向

に発光する端面発光形と垂

直な方向に発光する面発光

形に分類される。発振スペク

トルの単峰性を得るため,素

子内に回折格子を設けた“分

布帰還形 (DFB : distributed

feed-back) レーザ”,“分布

反射形 (DBR : distributed

bragg reflection) レーザ”など

がある。

JIS Z 8120参照。

laser diode

8

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

2040

フォトダイオード

PD

ふぉとだいおーど

ぴーでぃー

pn接合又はショットキー接合に照射し

た光によって生じた電子・正孔が空乏

層の電界によって分離されて生じる電

流を利用して光を検出するダイオー

ド。

参考 通常,接合に逆方向電圧を印

加した状態で使われる。バイ

ポーラトランジスタと同じ

構造で,ベース領域を受光部

にして,光照射によって発生

する多数キャリアの蓄積に

基づく大きな電流利得を利

用したものも多く使われて

いる。これはベース電極をも

たず,2端子で用いられるが,

構造上フォトトランジスタ

と呼ばれる。

JIS Z 8120参照。

photodiode

2041

pinフォトダイオ

ード

ぴーあいえぬふぉとだ

いおーど

ぴんふぉとだいおーど

フォトダイオードの一種で,p層とn層

との間に不純物濃度の低いi層を設け,

通常のpn接合形フォトダイオードより

高速応答性,受光感度の向上を図った

受光素子。

p-i-n photodiode

2042

アバランシェフォ

トダイオード

APD

あばらんしぇふぉとだ

いおーど

えいぴーでぃー

フォトダイオードの一種で,pn接合又

はショットキー接合の逆方向に高電圧

を印加し,アバランシェ降伏領域で用

いることによって増幅作用を付加し,

高速,高感度特性を図った受光素子。

avalanche

photodiode

2043

フォトカップラ

発光素子と受光素子を組み合わせて,

電気信号を入力(発光素子)側から出

力(受光素子)側へ光に変えて送り,

入出力間を電気的に絶縁した構造の素

子。

photocoupler

2044

ヘテロ構造電界効

果トランジスタ

HFET

へてろこうぞうでんかい

こうかとらんじすた

えいちえふいーてぃー

ヘテロ接合構造を利用した電界効果ト

ランジスタの総称。

備考 異なる半導体材料を結晶学

的に接続した接合を“ヘテロ

接合”という。

参考 シングルヘテロ接合の界面

にできる電子蓄積層をチャ

ネルとする構造のもの,ダブ

ルヘテロ接合の間の量子井

戸層をチャネルとする構造

のものなどがあり,設計の自

由度を増すことで電界効果

トランジスタの高性能化が

可能になる。

heterostructure

field-effect

transistor

heterojunction

9

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

2045

高電子移動度トラ

ンジスタ

HEMT

こうでんしいどうどと

らんじすた

へむと

電界効果トランジスタの一つで,ヘテ

ロ接合と変調ドープ技術を利用してチ

ャネルでのキャリア散乱を減らすこと

によって,高速化,低雑音化を図った

もの。

備考 “変調ドープ

FET

(MODFET)”,“2次元電子ガ

スFET (2DEGFET)”とも呼ば

れる。

high electron

mobility transistor

modulation doped

field-effect

transistor

two-dimensional

electron gas

field-effect

transistor

2046

ヘテロ接合バイポ

ーラトランジス

タ

HBT

へてろせつごうばいぽ

ーらとらんじすた

えいちびーてぃー

エミッタにバンドギャップの広い半導

体を用い,ベース・エミッタヘテロ接

合に形成された電位障壁を利用するこ

とで,ベースからエミッタへの少数キ

ャリアの注入を抑制して,エミッタ注

入効率を1に近づけ,高い電流増幅率

を実現したバイポーラトランジスタ。

参考 例えば,ベースにはGaAsを,

エミッタにはベースよりも

広いバンドキャップをもつ

AlGaAs半導体を用いること

で,ベース抵抗とベース・エ

ミッタ間の接合容量が小さ

なトランジスタを実現でき

る。高周波性能,温度特性な

どの面で優れている。

heterojunction

bipolar transistor

2047

モノリシックマイ

クロ波集積回路

MMIC

ものりしっくまいくろ

はしゅうせきかいろ

えむえむあいしー

1個の半導体チップ内に複数の素子,高

周波用平面回路などの配線が一体的に

作り込まれ,主としてマイクロ波以上

の周波数帯域で機能する集積回路。

monolithic

microwave

integrated circuit

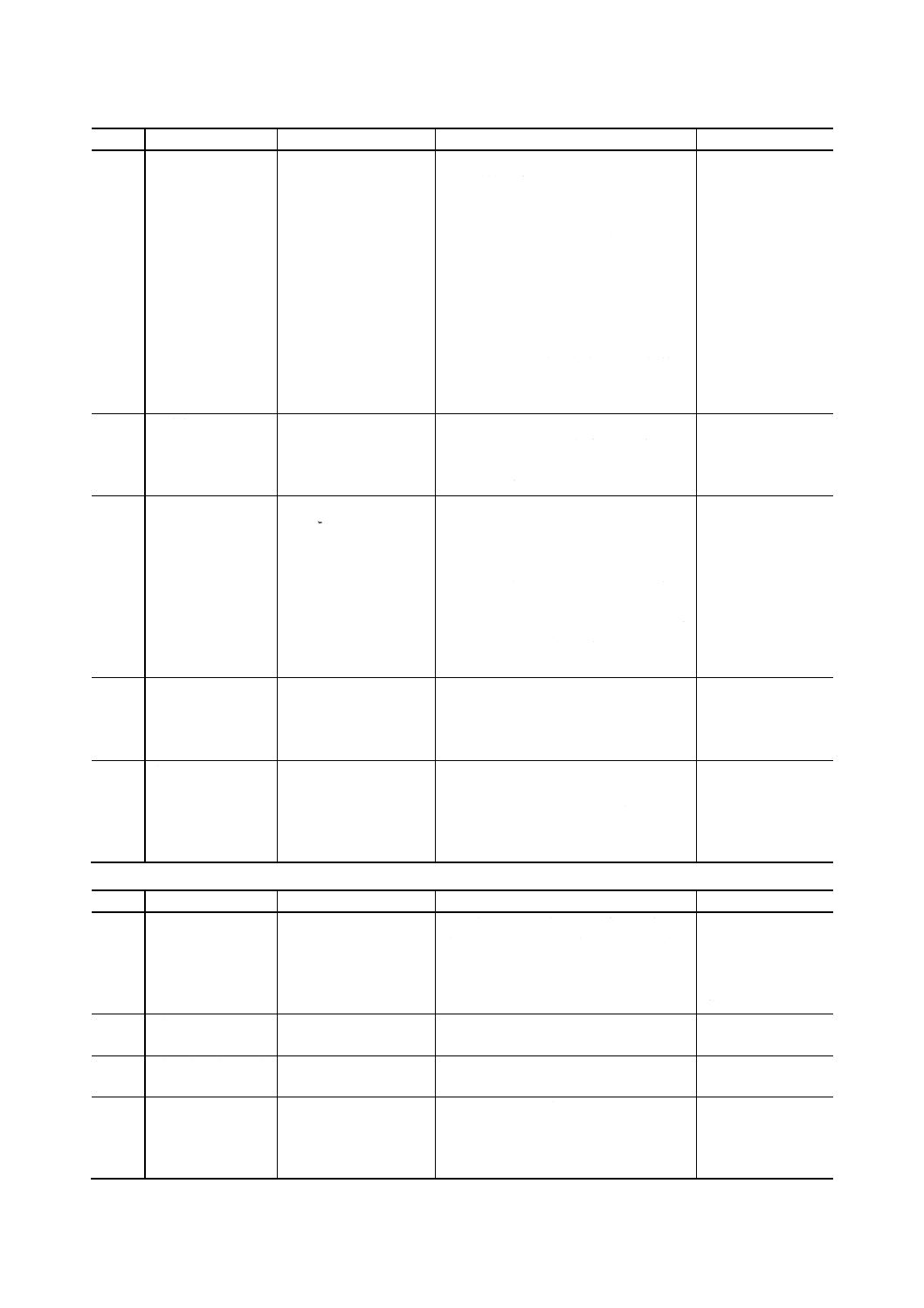

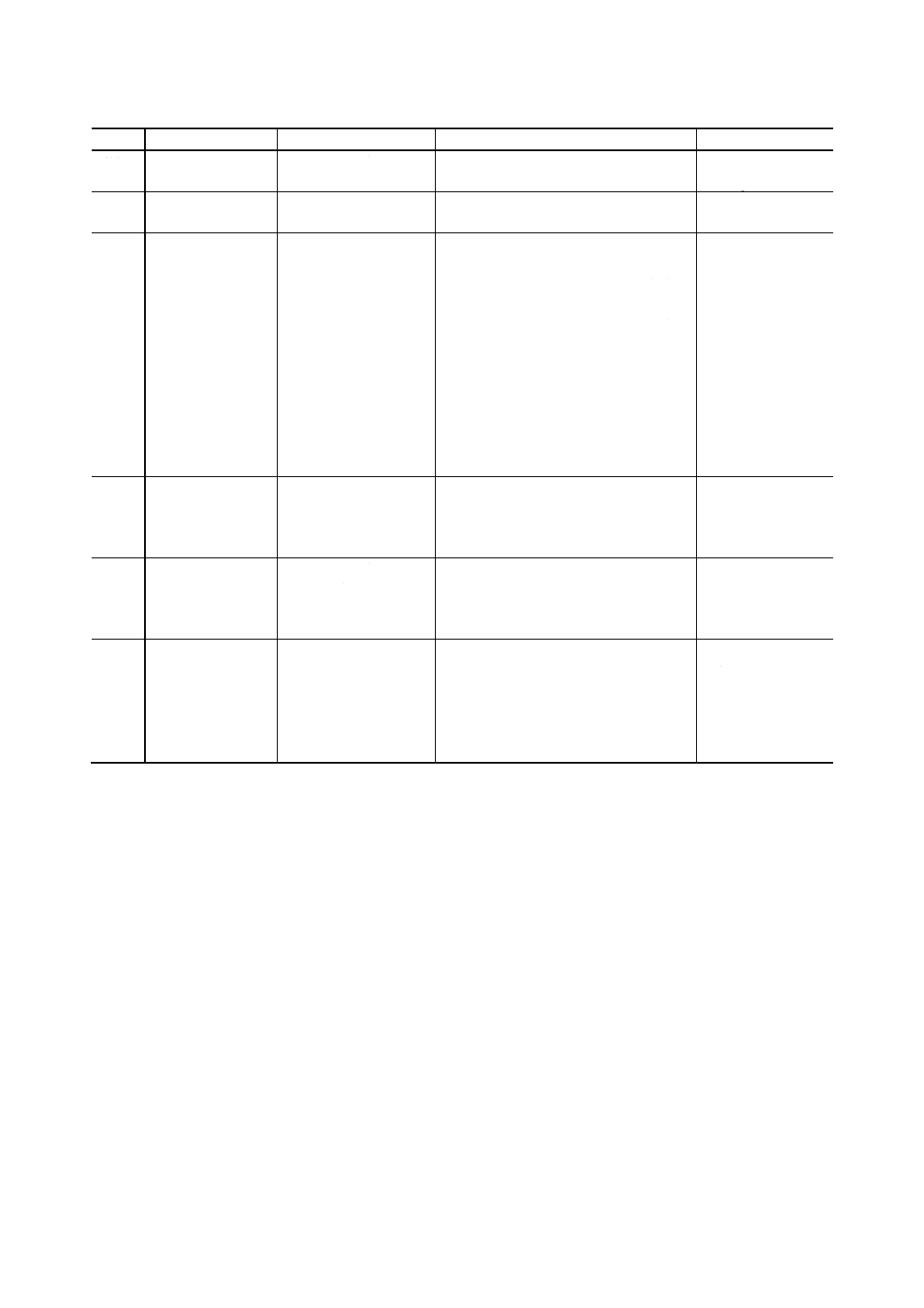

(3) プロセス関連用語

番号

用語

読み方(参考)

定義

対応英語(参考)

3001

基板

きばん

表面上又はその内部に集積回路などを

作るための土台となる半導体,絶縁体

などの板。

参考 JIS X 6221参照。

substrate

3002

ウェーハ

能動素子,受動素子若しくは集積回路

を形成,又は形成することを前提とし

た薄い半導体板。

wafer

3003

洗浄

せんじょう

ウェーハ表面上の物を除去すること。

cleaning

3004

酸化【シリコン集

積回路工程で

の】

さんか

シリコンの表面層を酸素と高温で反応

させることによって,二酸化けい素化

する工程。

oxidation

10

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

3005

エッチング

不要部分を化学的又は電気化学的に除

去すること。

備考 ガスを用いる“ドライエッチ

ング”,薬液を用いる“ウェ

ットエッチング”,エネルギ

ー粒子を用いる“スパッタエ

ッチング”などがある。

参考 JIS C 5603参照。

etching

dry etching

wet etching

sputter etching

3006

スパッタエッチン

グ

ガスやイオンのエネルギー粒子を物質

に衝突させて,その表面の構成原子分

子を放出させるエッチング方法。

備考 ガスイオンを基板に衝突さ

せ,不要部分を除去する意味

でも用いられる。

sputter etching

3007

スパッタたい積

すぱったたいせき

スパッタエッチングによって放出させ

た材料を基板上にたい積させる成膜方

法。

sputter deposition

3008

真空蒸着

しんくうじょうちゃく

真空内で物質を加熱し,これを蒸発さ

せ,その蒸発物を他の物質の表面上に

被着させることによって膜を作るこ

と。

vacuum evaporation

3009

メタライゼーショ

ン

ウェーハ上に電極や配線用の金属薄膜

を形成する工程。

metalization

3010

拡散

かくさん

熱拡散によって半導体中に不純物を導

入する工程。

diffusion

3011

イオン打込み

いおんうちこみ

不純物をイオンの形にして電界によっ

て加速し,半導体などの内部に打ち込

むこと。

ion implantation

3012

アニール

イオン打込みなどのプロセスによって

発生した欠陥を消滅させるための加熱

操作で,結晶性,キャリア密度,移動

度などの特性の回復を図ること。

参考 JIS K 6900参照。

anneal

3013

シンタ

粉体を融点以下の低温で加熱し,粉体

同士の結合を強め,固体化すること。

集積回路プロセスでは,蒸着した配線

金属多結晶体の結晶粒の結合強化,結

晶粒径増大,配向性増大,下地材料と

の密着性強化などをシンタによって行

う。

備考 “焼結”ともいう。

参考 JIS Z 2500参照。

sinter

3014

ゲート酸化膜

げーとさんかまく

MOSFETのゲート電極下にあるシリコ

ン酸化膜。

gate oxide

3015

フィールド酸化膜

ふぃーるどさんかまく

素子間の電気的分離に用いるシリコン

酸化膜。

field oxide

3016

層間絶縁膜

そうかんぜつえんまく

2層以上の導体層の間を電気的に絶縁

するための膜。

interlayer dielectric

11

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

3017

パッシベーション

表面不活性化

ぱっしべーしょん

ひょうめんふかっせい

か

半導体の表面を安定化するために表面

をシリコン酸化膜などのような物質で

被覆して,不活性にすること。

備考 このような目的で半導体表

面に形成された膜を“パッシ

ベーション膜”という。表面

を保護する目的でも使われ,

“表面保護膜”ともいう。

参考 回路を保護するための表面

保護膜に対して使われるこ

とがある。

passivation

surface passivation

passivation film

3018

リソグラフィ

写真食刻を使用して,回路のパターン

を形成する手法の総称。

lithography

3019

マスク合わせ

ますくあわせ

リソグラフィ工程内でウェーハのパタ

ーンに更に写真マスクを重ね合わせる

作業。

mask alignment

3020

フォトレジスト

リソグラフィに用いられる感光性樹

脂。

参考 光が照射される部分が現像

液に溶けるポジ形と,光が照

射されない部分が溶けるネ

ガ形がある。

JIS Z 8113参照。

photoresist

3021

露光

ろこう

塗布したフォトレジストに光を照射し

て所望のパターンを焼き付ける工程。

参考 マスクを通して紫外線を照

射し,マスク上のパターンを

転写する方法と電子ビーム,

イオンビームを使用して直

接描写する方法がある。

JIS Z 6000参照。

exposure

3022

埋込層

うめこみそう

半導体基板内部に形成された周囲とは

異なる導電率,又は導電形式の半導体

層若しくは金属層。

buried layer

3023

アイランド

半導体集積回路の基板内で電気的に基

板とは分離された半導体片の部分。

island

3024

ウェル

CMOSの構造作製のために基板表層部

に形成された基板とは異なった導電率

又は導電形式をもつ領域。

備考 “タブ”ともいう。

参考 2種類の導電形式層が隣接し

て形成されたものをツイン

ウェルと呼ぶ。

well

tub

3025

拡散抵抗

かくさんていこう

拡散層の層抵抗を利用した抵抗素子。

参考 層抵抗とは,その層の面積抵

抗を指す。

diffused resistor

3026

コンタクトホール

金属電極又は金属配線と基板を接続す

るために用いられる孔。

contact hole

3027

バイアホール

ビアホール

多層構造の配線を接続するために用い

られる孔。

via hole

12

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

3028

[素子間]分離

[そしかん]ぶんり

集積回路の構成部分同士が電気的に相

互の影響を受けないようにすること。

備考 分離には,半導体集積回路の

各素子をpn接合で分離する

“接合分離”,絶縁層,例え

ば,SiOなどによって分離す

る“絶縁層分離(酸化膜分離

ともいう。)”,単結晶と多結

晶との境界の絶縁性を利用

し,多結晶によって半導体集

積回路の各素子を電気的に

分離する“多結晶分離”など

がある。

isolation

junction isolation

dielectric isolation

polycrystalline

isolation

3029

化学気相反応法

CVD法

かがくきそうはんのう

ほう

しーぶいでぃーほう

気体分子の分解又は反応によって生成

物を基板表面に付着成膜させる方法。

備考 “化学気相成長法”ともい

う。

chemical vapor

deposition

3030

エピタキシャル成

長

えぴたきしゃるせいち

ょう

基板結晶上に気相又は液相で原料を供

給し,基板結晶と結晶軸をそろえて結

晶を成長すること。

備考 “エピタキシ”ともいう。

参考 気相で原料を供給する気相

エピキタシ,液相で原料を供

給する液相エピキタシ,非結

晶の固体を結晶化させる固

相エピキタシなどがある。

epitaxial growth

epitaxy

3031

プレナ技術

ぷれなぎじゅつ

選択拡散,イオン打込み,リソグラフ

ィ,膜成長などの技術を用いて,基板

結晶の同一平面上に素子を形成するこ

と。

planar technique

3032

クリーンルーム

プロセス中でウェーハなどの部品及び

材料が汚染されないように,空気中の

じんあいなどをフィルタで除去するな

ど特に念入りな手段で清浄化された

室。

clean room

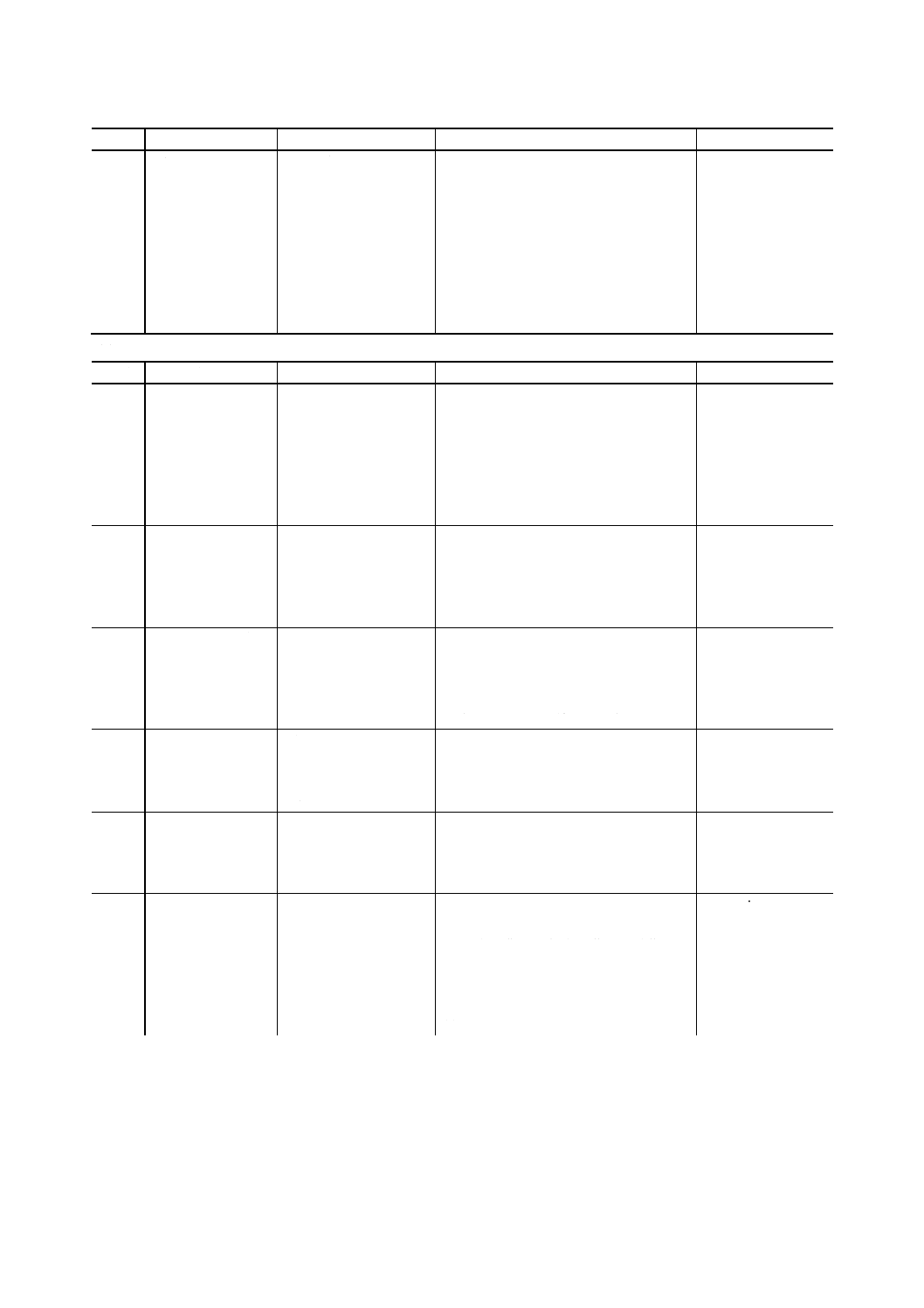

(4) 組立,実装関連用語

番号

用語

読み方(参考)

定義

対応英語(参考)

4001

チップ

受動素子,能動素子又は集積回路を形

成した,若しくは形成することを前提

とした半導体又は絶縁物の細片。

備考 “ペレット”又は“ダイ”と

もいう。

chip

pellet

die

4002

ダイ分割

だいぶんかつ

集積回路が形成されたウェーハを個々

のチップに分割すること。

die separation

4003

ダイボンディング

チップを基板又はパッケージに接着す

ること。

die bonding

4004

ボンディングパッ

ド

パッケージ引出線又はパッケージ引出

線に接続された細い金属線を接着する

ために半導体チップ上に設けた金属薄

膜による小面積の電極。

bonding pad

13

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

4005

電極

でんきょく

部品の特定な領域から電気的機能を取

り出し,他との電気的接続を行う導体

的構成部品。

参考JIS C 7102参照。

electrode

4006

端子

たんし

外部と接続するために利用できる構成

部分で,信号又はエネルギーの出入口

として用いられるもの。

参考 JIS C 8500参照。

terminal

4007

ワイヤボンディン

グ

素子相互間又はリードフレームとこれ

らの素子を相互接続するために極細線

を取り付けること。

参考 JIS X 3001参照。

wire bonding

4008

構成部品

こうせいぶひん

一つの機能体を構成している部品。例

えば,回路でのトランジスタ,抵抗,

コンデンサなどの部品。

component

4009

組立

くみたて

幾つかの部品を用いて機能体を組み立

てること。

assembly

4010

実装

じっそう

構成部品を配置,接続すること。

packaging

4011

配線

はいせん

一つの回路機能をもたせるために構成

部品同士を相互に導体で電気的に接続

すること。

interconnection

4012

多層配線

たそうはいせん

構成部品同士を相互に立体的に接続す

るための配線用導体と絶縁体とを交互

に積層して2層以上の導体層をもった

配線。

multilevel

interconnection

4013

パッケージ

構成部品を配置,接続保護するための

端子をもつ容器。

参考 システムとしては実装され

たデバイス群からなるサブ

システムを指すことがある。

package

4014

樹脂封止

じゅしふうし

成形用の型の中に樹脂を注入・加圧し

て部品を樹脂で封じ込めること。

plastic molding

4015

気密封止

きみつふうし

外気の流通を遮断するように部品を封

じ込めること。

備考 “ハーメチックシール”とも

いう。

hermetic sealing

4016

リード成形

りーどせいけい

リードを所定の形状に整えること。

lead forming

4017

リード外装

りーどがいそう

はんだ付けをするために前もってリー

ドをはんだで覆うこと。

lead soldering

4018

バンプ

半導体チップ又は配線用リードに形成

された突起状の接続電極。

参考 半導体チップ上のバンプに

は前処理工程で作り込むも

のとワイヤボンダで作るワ

イヤバンプがある。

JIS B 0153参照。

bump

4019

リードフレーム

一つのデバイスに対応したダイパッド

及びリードのパターンを繰り返し形成

したテープ状の金属製フィルム。

lead frame

14

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

4020

TAB

てぃーえいびー

テープ状に加工したリードフレーム繰

返しパターンと半導体チップを連続的

に接着し,配線を行う自動的ボンディ

ング方法。

備考 表面同士を対向させて密着

し接続することを“フェース

ダウンボンディング”又は

“フェースボンディング”と

いう。

tape automated

bonding

face down bonding

face bonding

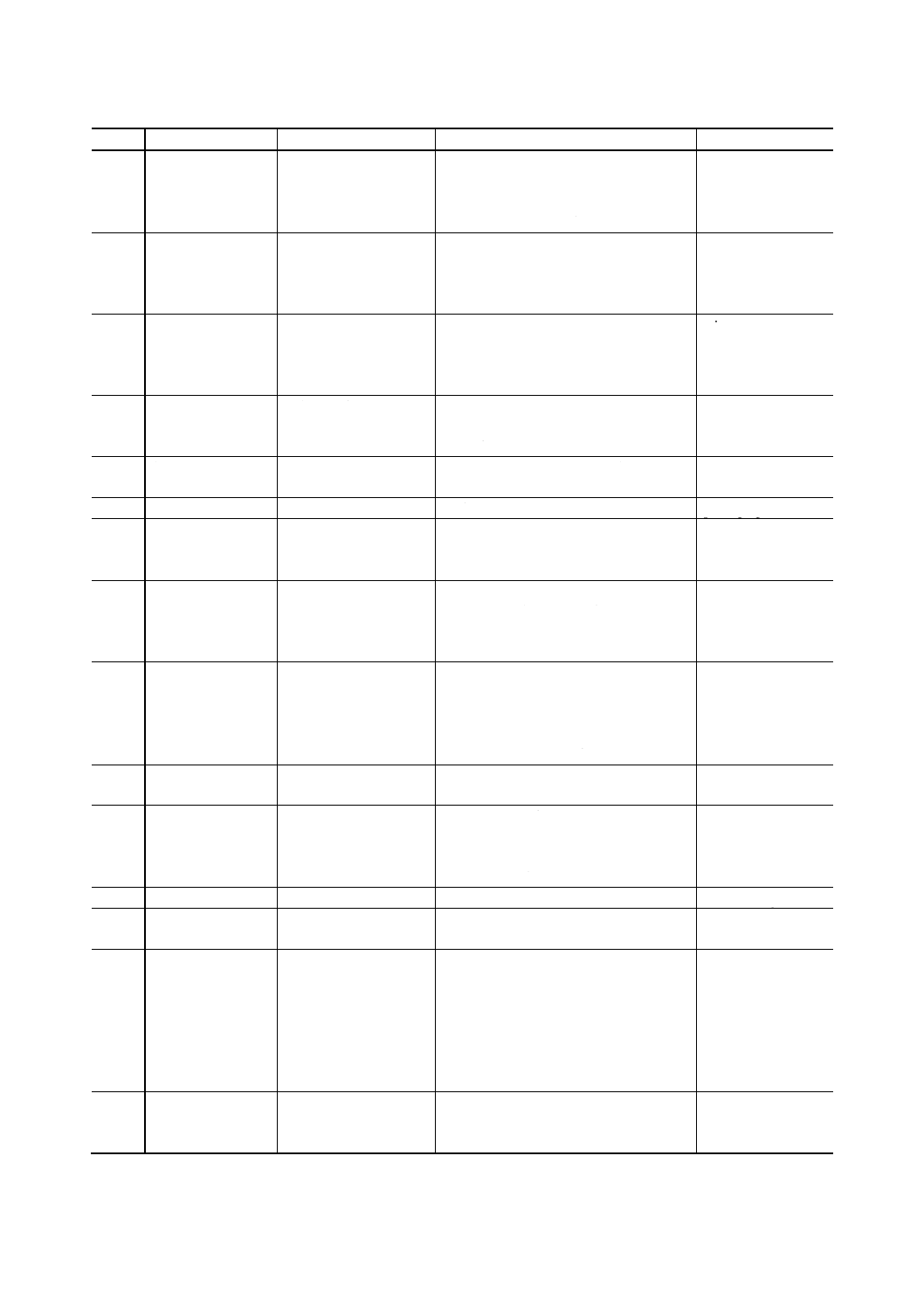

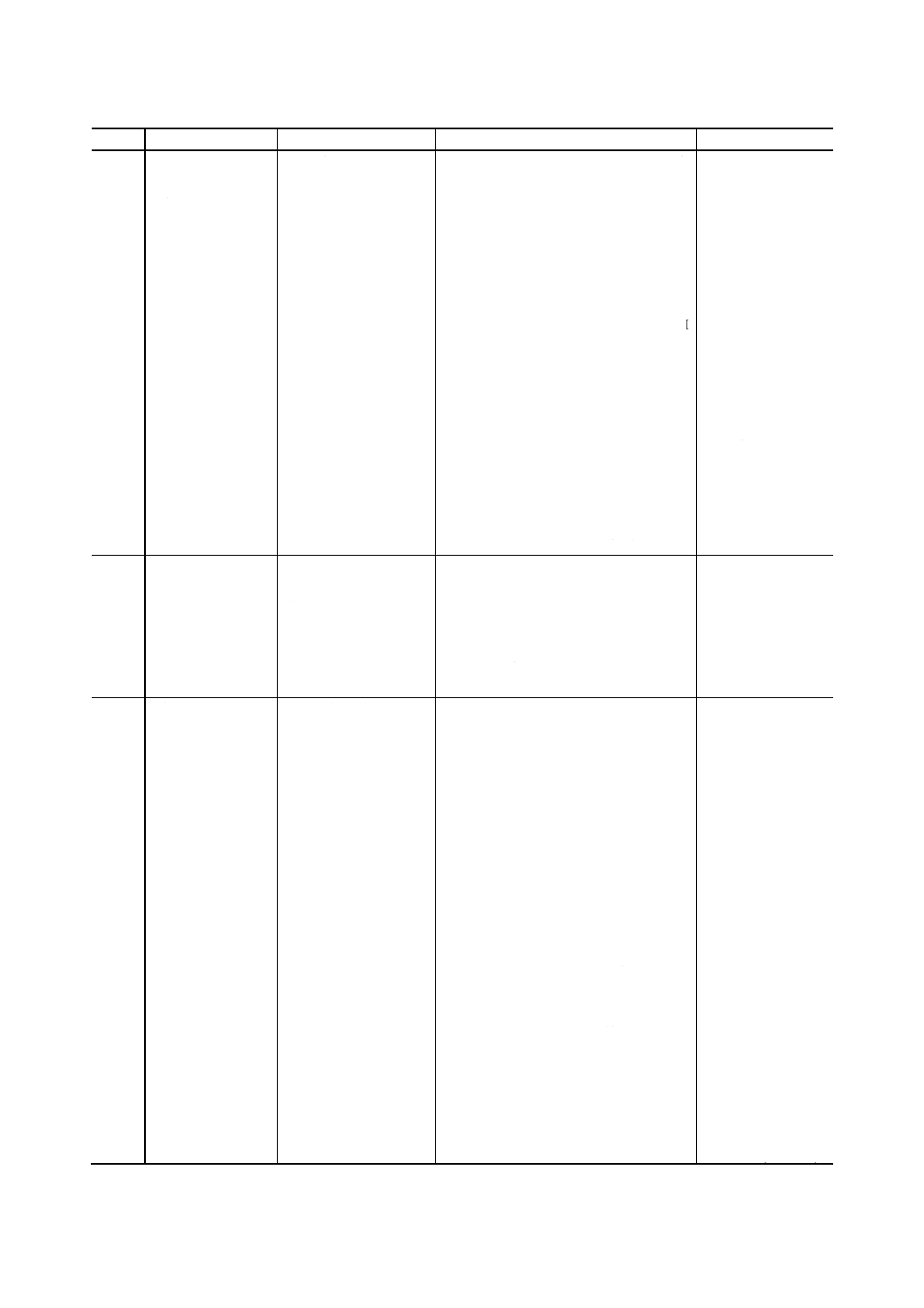

(5) 信頼性関連用語

番号

用語

読み方(参考)

定義

対応英語(参考)

5001

歩留り

ぶどまり

集積回路製造の各工程で,着手数に対

する良品完成数の比率。

参考 各工程で,ウェーハ歩留り,

ダイソード歩留り,アセンブ

リ歩留り,テスト歩留りなど

と呼ばれている。

JIS Z 8141参照。

yield

5002

エレクトロマイグ

レーション

大電流ストレスを受けた金属配線中の

金属原子の移動が原因でボイド形成又

は原子の蓄積が生じ,配線の抵抗値増

加,オープン及び(又は)配線間ショ

ートなどの故障を引き起こす現象。

electromigration

5003

ストレスマイグレ

ーション

金属配線膜がパッシベーション膜又は

層間絶縁膜から受ける応力に起因し

て,高温処理又は温度サイクルによっ

て配線内の原子移動が起こり,抵抗値

が変動したり,断線する現象。

stress-migration

5004

絶縁膜経時破壊

TDDB

ぜつえんまくけいじは

かい

てぃーでぃーでぃーび

ー

瞬時の絶縁破壊を生じる電圧よりも低

い電圧ストレスを絶縁膜が長時間受け

ることによって破壊する現象。

time dependent

dielectric

breakdown

5005

静電破壊

せいでんはかい

帯電した人体や物体などがリードに接

触した場合,又は帯電したデバイスが

導体に接触した場合の放電によって,

素子が破壊する現象。

electrostatic

discharge damage

5006

ホットキャリア効

果

ほっときゃりあこうか

半導体中の高電界によって発生したホ

ットキャリアがゲート酸化膜に注入さ

れ,酸化膜界面や酸化膜中に電荷を生

成し,トランスコンダクタンス(相互

コンダクタンス)又はしきい値電圧な

どのMOSFET特性変動を生じさせる効

果。

hot carrier effect

15

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

5007

ソフトエラー

α線などの放射線が半導体チップ内に

入射し,内部に電子・正孔ペアを発生

させることによって生じる集積回路の

一過性の誤動作。

参考 RAMのメモリセル容量部に

入射する場合にはメモリ情

報の反転が起こる。物理的欠

陥に起因しないで,全くラン

ダムに発生する誤動作を総

称してソフトエラーと呼ぶ

ことがある。

JIS D 0103参照。

soft error

5008

ラッチアップ

CMOSデバイスの端子電圧が,変動又

は外部トリガによってある値を超える

と寄生サイリスタ回路が導通状態とな

り,大電流が流れ,回路動作が阻害さ

れたり,IC自体が破壊される現象。

latchup

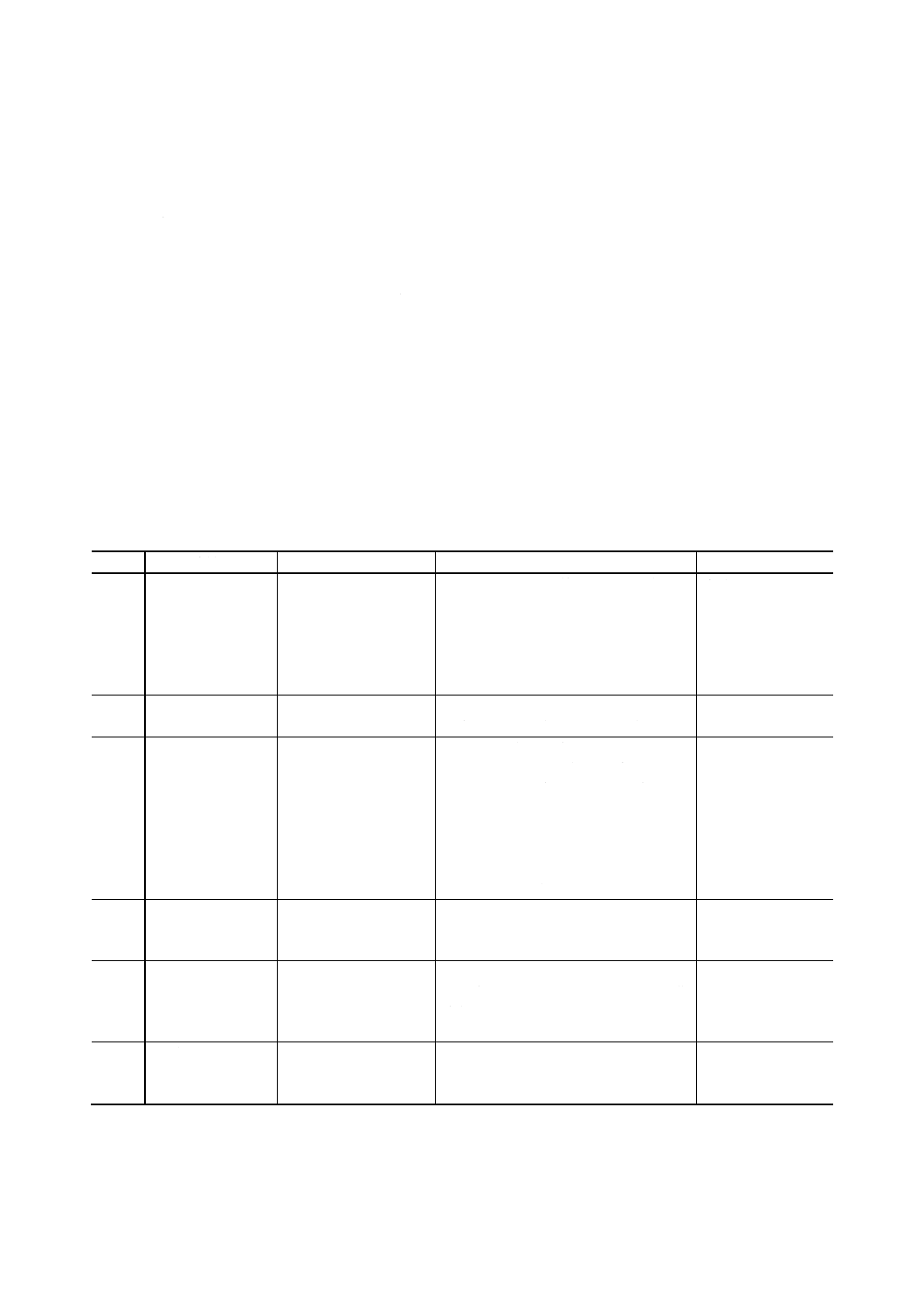

(6) 設計,回路関連用語

番号

用語

読み方(参考)

定義

対応英語(参考)

6001

マイクロプロセッ

サ

一つの半導体チップ上に演算,制御,

入出力回路などを集積化した処理装

置。

参考 JIS X 0011参照。

microprocessor

6002

計算機使用設計

CAD

けいさんきしようせっ

けい

しーえいでぃー

きゃど

計算機を使用しての設計,シミュレー

ション及び検証の総称。

参考 JIS B 3000参照。

computer aided

design

6003

レイアウト設計

れいあうとせっけい

設計の前工程である論理設計又は回路

設計で決められた回路接続情報に従っ

て,回路の基本素子の形状を決定し,

チップ領域内での位置及び向きと必要

な相互配線経路を決め,さらに製造工

程で用いるマスクのパターンを決定す

る工程。

layout design

6004

ASIC

えいしっく

ある特定の応用に最適設計された特定

用途向け集積回路。

application specific

integrated circuit

6005

ゲートアレイ方式

げーとあれいほうしき

論理ゲートを構成するためのトランジ

スタなどの回路素子を規則的に配列し

たはん(汎)用のウェーハをあらかじ

め作っておき,これにユーザの仕様に

合わせて設計した配線パターンを追加

して,所望のLSIに仕上げる方式。

gate array method

6006

スタンダードセル

方式

すたんだーどせるほう

しき

何種類かの機能ブロック(インバータ,

NOR,フリップフロップなど)をあら

かじめレイアウト設計し,それをセル

としてライブラリに登録しておき,設

計の際は与えられた論理設計仕様に基

づいて,これらのセルに対する配置・

配線設計を行って所望のLSIを実現す

る方式。

standard cell metbod

16

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

番号

用語

読み方(参考)

定義

対応英語(参考)

6007

カスタムLSI

かすたむえるえすあい

ユーザの使用目的に合わせて設計した

専用のLSI。

custom large-scale

integrated circuit

6008

BIST

びーあいえすてぃー

回路内部に試験系列発生機構を組み込

んだ自己試験方法。

built-in self test

6009

RISC

りすく

コンピュータアーキテクチャ設計の一

手法で,命令セットを少数の単純命令

セットで構成し,これらの単純命令を

高速(例えば,1命令を1マシンサイク

ル)に実行することによって,高速性

能化した処理装置。

備考1.“縮小命令セットコンピュー

タ”ともいう。

2.“CISC”は1命令で複雑な機

能を実効する命令セット

で構成し,高性能化に対処

した処理装置。

reduced instruction

set computer

complex instruction

set computer

6010

ECL

エミッタ結合論理

いーしーえる

えみったけつごうろん

り

バイポーラトランジスタを用いたディ

ジタル回路の一つで,トランジスタの

活性領域と遮断領域との間をスイッチ

して用いる代表的な不飽和論理回路。

emitter coupled logic

6011

TTL

トランジスタ・ト

ランジスタ論理

てぃーてぃーえる

とらんじすた・とらんじ

すたろんり

バイポーラトランジスタを組合せ構成

したNANDゲートを実現する論理ゲー

トで,飽和領域と遮断領域のどちらか

で動作する代表的な飽和論理回路。

transistor transistor

logic

6012

IIL

集積注入論理

あいあいえる

しゅうせきちゅうにゅ

うろんり

マルチコレクタnpnトランジスタをス

イッチングトランジスタとして用いた

インバータ回路。

参考 抵抗及びアイソレーション

領域を必要としないので,高

密度回路が形成される。

integrated injection

logic

17

C 5610-1996

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

集積回路用語 JIS原案作成委員会 構成表

氏名

所属

(委員長)

木 村 忠 正

電気通信大学電気通信学部

(幹事)

和 田 嘉 記

日本電信電話株式会社

伊 東 俊 樹

株式会社日立製作所

川 城 三 治

株式会社ゼクセル

瀬戸屋 孝

株式会社東芝

立 川 明

社団法人日本電子機械工業会

千 野 健 一

住友金属鉱山株式会社

中 林 正 和

三菱電機株式会社

鳴 神 長 昭

財団法人日本電子部品信頼性センター

中 島 一 郎

通商産業省機械情報産業局

二 川 清

日本電気株式会社

萩 原 良 昭

ソニー株式会社

馬 場 智 也

シャープ株式会社

福 田 裕

沖電気工業株式会社

古 市 正 敏

工業技術院

和 田 哲 明

松下電子工業株式会社

(事務局)

東 條 喜 義

社団法人日本電子工業振興協会