X 6305-3:2012 (ISO/IEC 10373-3:2010)

(1)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

目 次

ページ

序文 ··································································································································· 1

1 適用範囲························································································································· 1

2 引用規格························································································································· 2

3 用語及び定義 ··················································································································· 2

4 試験方法における一般適用条件 ··························································································· 3

4.1 試験環境 ······················································································································ 3

4.2 準備 ···························································································································· 3

4.3 試験方法の選択 ············································································································· 3

4.4 許容誤差 ······················································································································ 3

4.5 総合的測定の不確かさ ···································································································· 3

4.6 電気計測の規則 ············································································································· 3

4.7 試験装置 ······················································································································ 3

4.8 試験方法と基本規格の要求項目との関係············································································ 11

5 外部端子付きICカードの電気的特性の試験方法 ··································································· 13

5.1 VCC端子 ···················································································································· 13

5.2 I/O端子 ······················································································································ 14

5.3 CLK端子 ···················································································································· 15

5.4 RST端子 ····················································································································· 16

5.5 SPU(C6)端子 ················································································································ 17

6 外部端子付きICカードの論理的な操作の試験方法 ································································ 17

6.1 リセット応答 ··············································································································· 17

6.2 T=0プロトコル ············································································································ 18

6.3 T=1プロトコル ············································································································ 20

7 IFDの物理的特性及び電気的特性の試験方法 ········································································ 28

7.1 外部端子の活性化 ········································································································· 28

7.2 VCC端子 ···················································································································· 28

7.3 I/O端子 ······················································································································ 30

7.4 CLK端子 ···················································································································· 31

7.5 RST端子 ····················································································································· 32

7.6 SPU(C6)端子 ················································································································ 34

7.7 外部端子の非活性化 ······································································································ 34

8 IFDの論理的な操作の試験方法 ·························································································· 34

8.1 リセット応答 ··············································································································· 34

8.2 T=0プロトコル ············································································································ 35

8.3 T=1プロトコル ············································································································ 37

X 6305-3:2012 (ISO/IEC 10373-3:2010) 目次

(2)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ページ

8.4 不正なPCBに対するIFDの応答 ····················································································· 43

X 6305-3:2012 (ISO/IEC 10373-3:2010)

(3)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

まえがき

この規格は,工業標準化法第14条によって準用する第12条第1項の規定に基づき,一般社団法人日本

ICカードシステム利用促進協議会(JICSAP)及び一般財団法人日本規格協会(JSA)から,工業標準原案

を具して日本工業規格を改正すべきとの申出があり,日本工業標準調査会の審議を経て,経済産業大臣が

改正した日本工業規格である。

これによって,JIS X 6305-3:2002は改正され,この規格に置き換えられた。

この規格は,著作権法で保護対象となっている著作物である。

この規格の一部が,特許権,出願公開後の特許出願又は実用新案権に抵触する可能性があることに注意

を喚起する。経済産業大臣及び日本工業標準調査会は,このような特許権,出願公開後の特許出願及び実

用新案権に関わる確認について,責任はもたない。

JIS X 6305の規格群には,次に示す部編成がある。

JIS X 6305-1 第1部:一般的特性

JIS X 6305-2 第2部:磁気ストライプ付きカード

JIS X 6305-3 第3部:外部端子付きICカード及び接続装置

JIS X 6305-5 第5部:光メモリカード

JIS X 6305-6 第6部:外部端子なしICカード−近接型

JIS X 6305-7 第7部:非接触(外部端子なし)ICカード−近傍型

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

日本工業規格 JIS

X 6305-3:2012

(ISO/IEC 10373-3:2010)

識別カードの試験方法−

第3部:外部端子付きICカード及び接続装置

Identification cards-Test methods-

Part 3: Integrated circuit cards with contacts and related interface devices

序文

この規格は,2010年に第2版として発行されたISO/IEC 10373-3を基に,技術的内容及び構成を変更す

ることなく作成した日本工業規格である。

なお,この規格で側線又は点線の下線を施してある参考事項は,対応国際規格にはない事項である。

また,この規格は,JIS X 6301に定義されたIDカードのパラメタ及び国際流通用としてのこのIDカー

ドの使用方法のうち,外部端子付きICカードを規定する一連の規格(JIS X 6320-2,JIS X 6320-3及びJIS

X 6320-4)及びこれに関連する接続装置の試験方法について規定する。

1

適用範囲

この規格は,JIS X 6320規格群の規定に従い,外部端子付きICカード及び関連した接続装置の特性の試

験方法を定義する。

各々の試験方法は,一つ以上の基本規格を引用して規定する。基本規格は,JIS X 6301又は識別カード

アプリケーションで使用される情報記憶技術を規定する一つ以上の補助規格であってもよい。

注記 許容性の基準は,この規格には含まれず,参照する規格に存在する。

JIS X 6305規格群の第3部であるこの規格は,外部端子付きICカード技術に固有な試験方法を扱う。JIS

X 6305規格群の第1部であるJIS X 6305-1は,1種類以上のカード技術に関する共通の試験方法について

扱い,JIS X 6305規格群の他の部は,それぞれのカードの試験技術について扱う。

この規格で記述される複数の試験方法は,それぞれ別々に独立して実行できるように配慮されている。

被試験のICカードに対し全ての試験を順番に適用することは,要求されていない。この規格で規定される

試験方法は,JIS X 6320-3に基づく。

ICカード及びIFDのそれぞれがこの規格で定義する試験方法を用いた適合性を満たしていても,実環境

で使用する場合に障害が起こらないことは保証されない。信頼性試験は,この規格の範囲外とする。

この規格は,ICカードの完全な機能を証明するためのいかなる試験も定義しない。試験方法は,最小限

の機能が確かめられることだけを要求する。最小限の機能は,次に定義する。

− カードの集積回路は,基本規格に適合するリセット応答を返す。

− カードの集積回路につながる外部端子は,基本規格に適合する電気抵抗を保持する。

注記 この規格の対応国際規格及びその対応の程度を表す記号を,次に示す。

ISO/IEC 10373-3:2010,Identification cards−Test methods−Part 3: Integrated circuit cards with

contacts and related interface devices(IDT)

2

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

なお,対応の程度を表す記号“IDT”は,ISO/IEC Guide 21-1に基づき,“一致している”こ

とを示す。

2

引用規格

次に掲げる規格は,この規格に引用されることによって,この規格の規定の一部を構成する。これらの

引用規格は,記載の年の版を適用し,その後の改正版(追補を含む。)は適用しない。

JIS X 6301:2005 識別カード−物理的特性

注記 対応国際規格:ISO/IEC 7810:2003,Identification cards−Physical characteristics(IDT)

JIS X 6320-3:2009 識別カード−ICカード−第3部:外部端子付きICカードの電気的インタフェー

ス及び伝送プロトコル

注記 対応国際規格:ISO/IEC 7816-3:2006,Identification cards−Integrated circuit cards−Part 3: Cards

with contacts−Electrical interface and transmission protocols(IDT)

JIS X 6320-4:2009 識別カード−ICカード−第4部:交換のための構成,セキュリティ及びコマンド

注記 対応国際規格:ISO/IEC 7816-4:2005,Identification cards−Integrated circuit cards−Part 4:

Organization, security and commands for interchange(IDT)

3

用語及び定義

この規格で用いる主な用語及び定義は,JIS X 6301及びJIS X 6320-3によるほか,次による。

3.1

ICカード(card)

JIS X 6320規格群で規定する外部端子付き集積回路カード。

3.2

試験対象品,DUT(DUT,device under test)

この規格の適用範囲内で試験されるICカード又はIFD。

3.3

ETU因子(etu-factor)

JIS X 6320-3の6.3.1及び7.1に記載されているように,プロトコル及びパラメタ選択(protocol and

parameters selection, PPS)によって,基本値(negotiated values)が取り決められ(to be negotiated),etuを

決定しているパラメタ群。

3.4

IFD(interface device)

JIS X 6320-3で規定する外部端子付きICカードに接続する接続装置。

3.5

通常使用(normal use)

カード技術に適した実装プロセスをもつ識別カード(JIS X 6301の4. 参照)及び装置間で使用される個

人情報の記録媒体としての使用。

3.6

試験方法(test method)

規格を満たしていることを確認するために,識別カード及び接続する接続装置の特性を試験する方法。

3

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.7

試験シナリオ(test scenario)

この規格で規定する試験方法で使用される代表的なプロトコル及びアプリケーション固有通信。

3.8

代表的プロトコル及びアプリケーション固有通信(typical protocol and application specific communication)

DUTと試験装置との間の通信であって,DUTに実装されたプロトコル及びアプリケーションに基づき,

かつ,通常使用に対応した通信。

4

試験方法における一般適用条件

4.1

試験環境

別途指定のない限り,試験環境は,23 ℃±3 ℃,相対湿度40 %〜60 %とする。

4.2

準備

試験方法で要求される場合,試験対象カードは,別途指定のない限り,試験開始の24時間前から,試験

環境条件を満足する場所に置かなければならない。

4.3

試験方法の選択

試験方法は,関連した基本規格(4.8参照)によって定義されるカードの特質を試験するために,必要に

応じて適用しなければならない。

4.4

許容誤差

別途指定のない限り,試験装置の性能(例えば,直線性)及び試験仕様(例えば,試験装置の調整)を

規定する数値に対する許容誤差は,±5 %以内でなければならない。

4.5

総合的測定の不確かさ

この試験方法によって測定された各値の不確かさを,試験成績書の中に記載しなければならない。

4.6

電気計測の規則

電位差は,ICカードのGND端子を基準に定義され,ICカードへ流れる電流を正とする。

4.7

試験装置

4.7.1

外部端子付きICカードを試験するための装置(ICカード試験装置)

4.7.1.1

VCC端子電圧(UCC)及びタイミングの生成

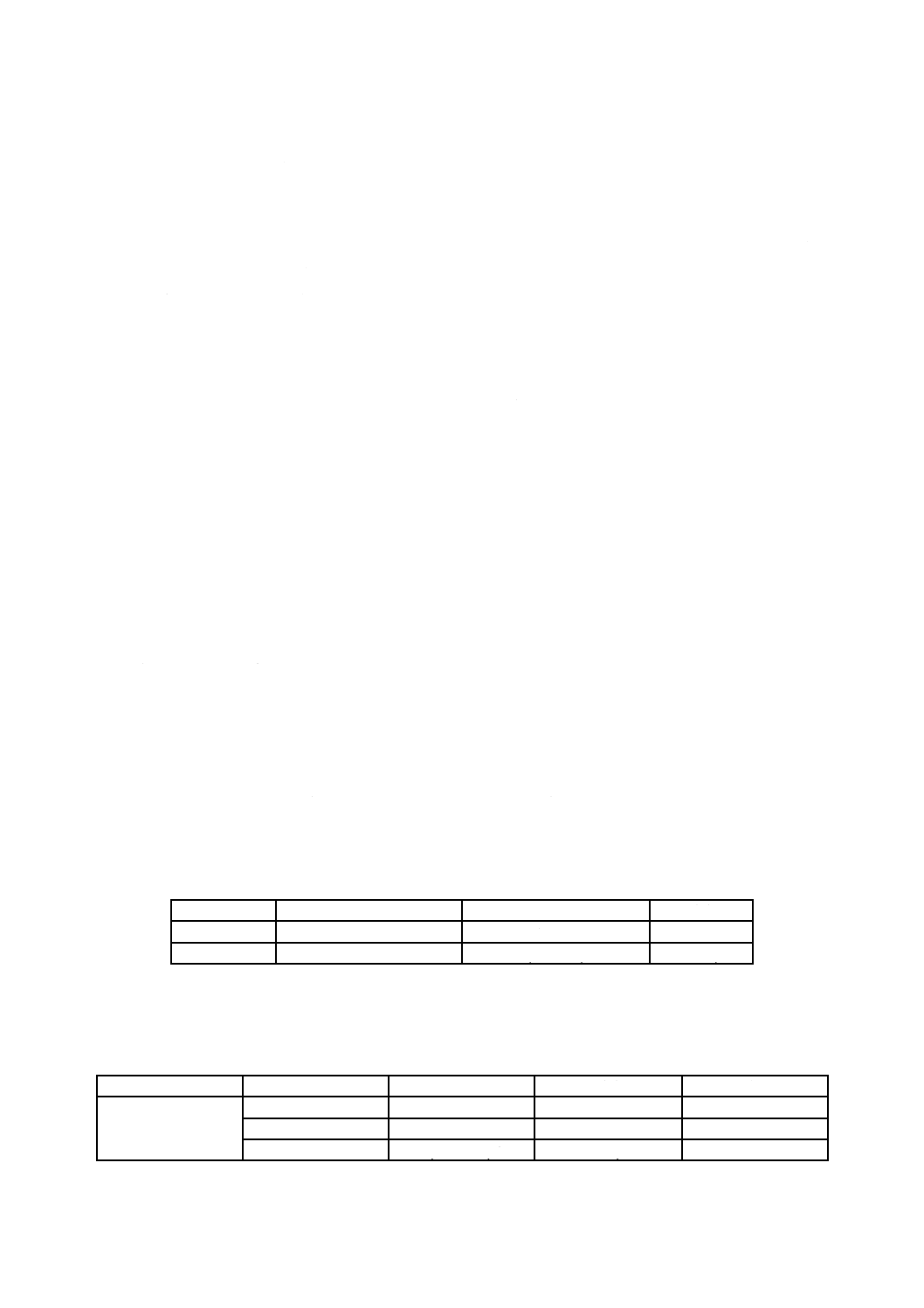

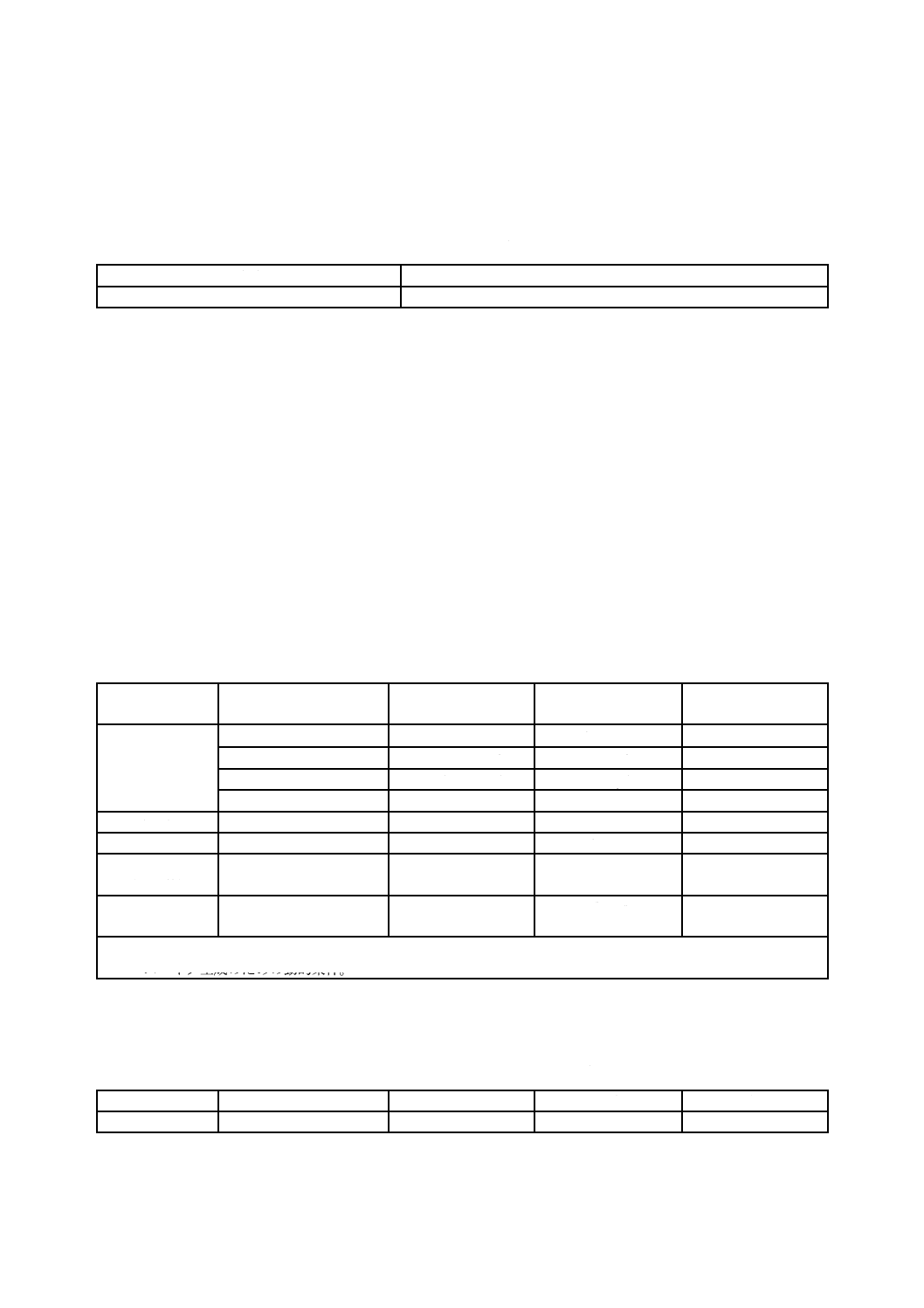

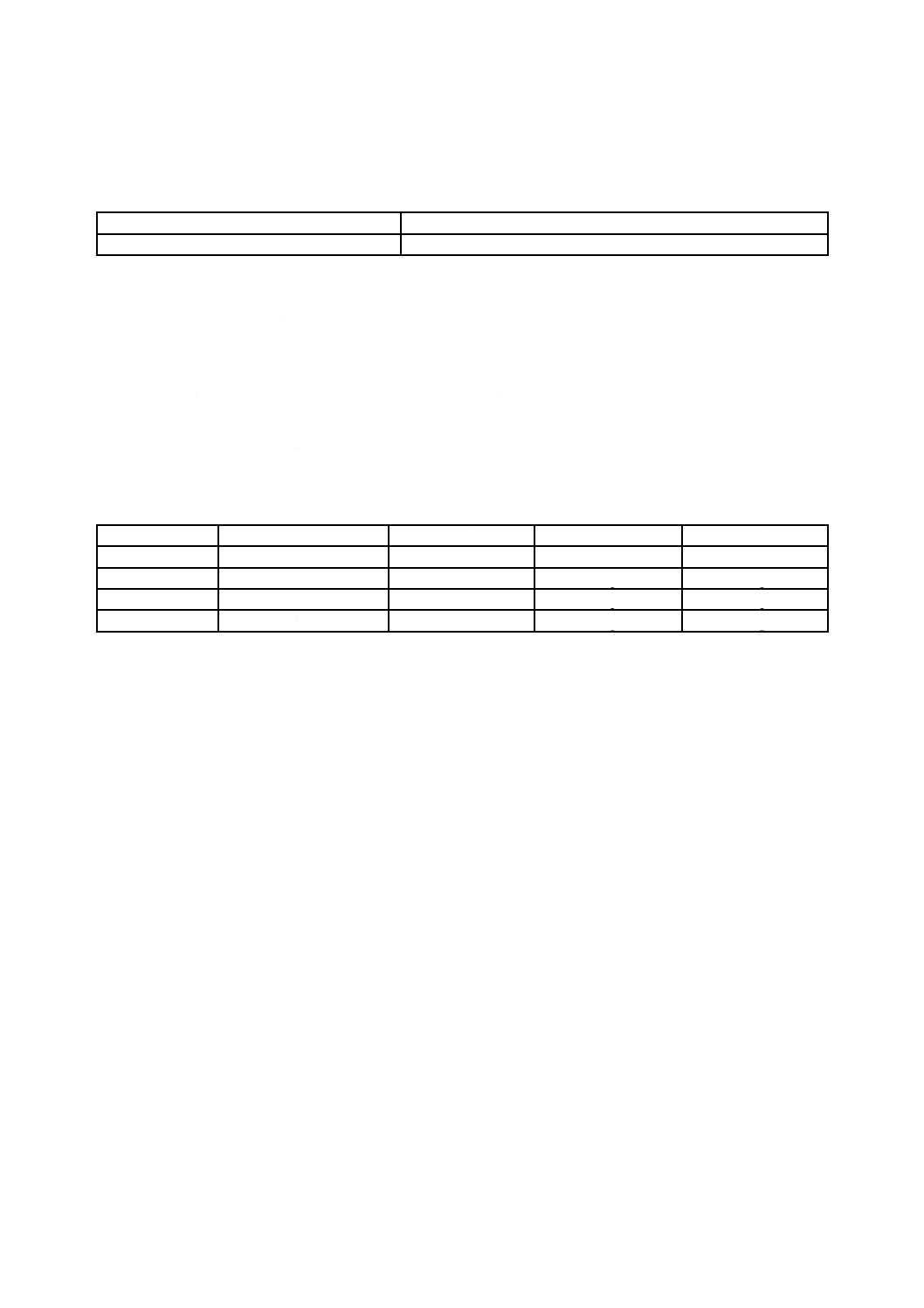

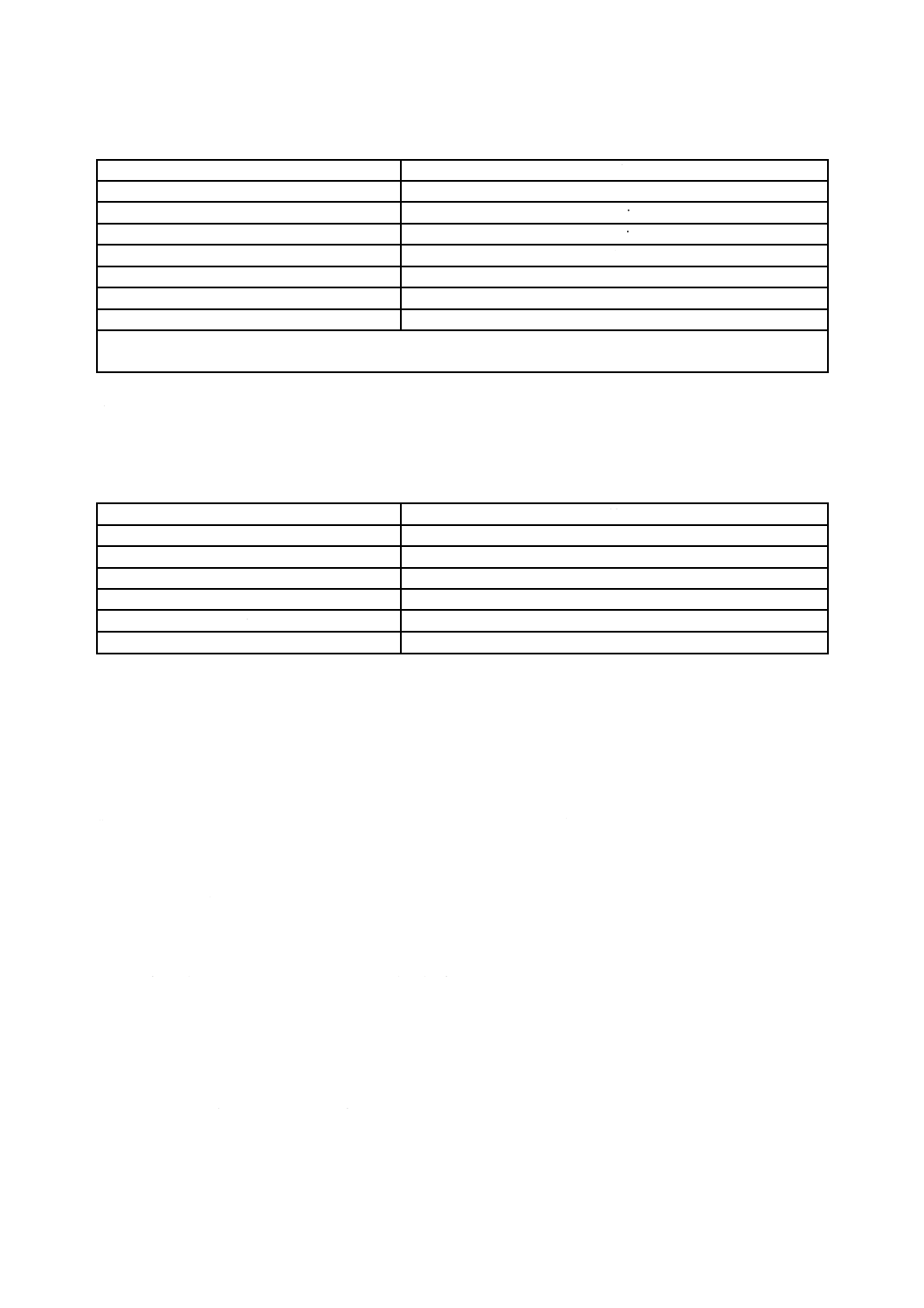

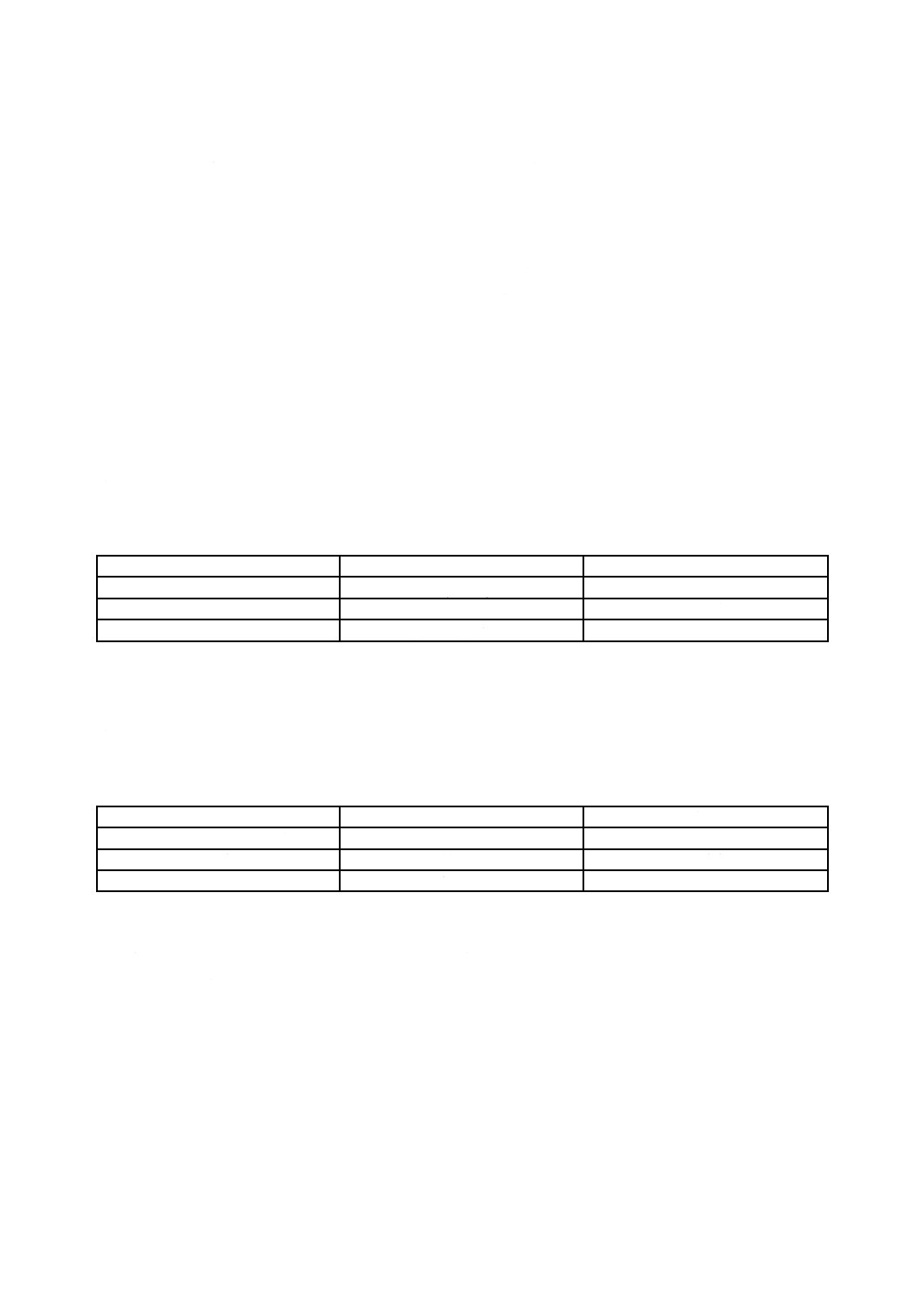

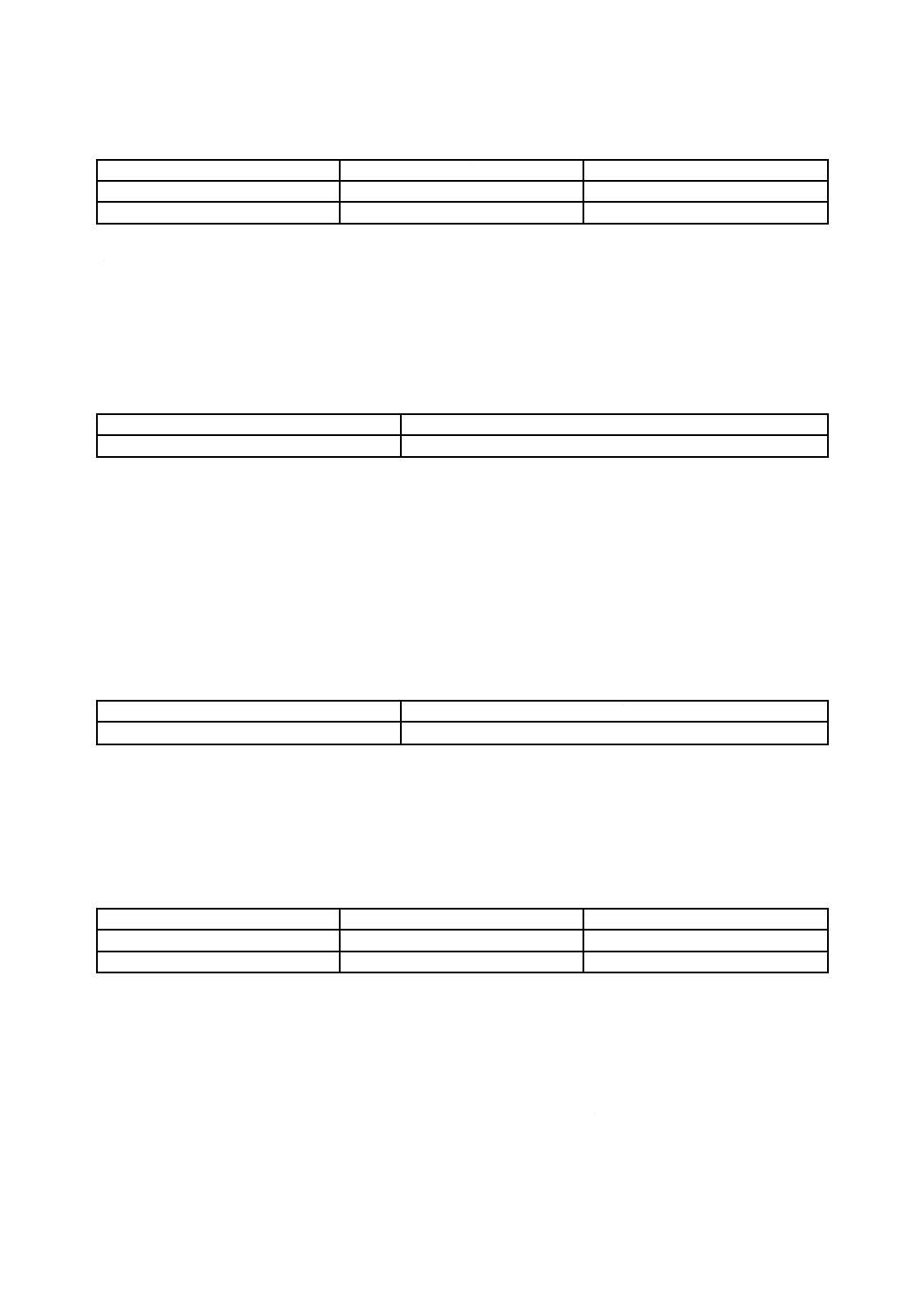

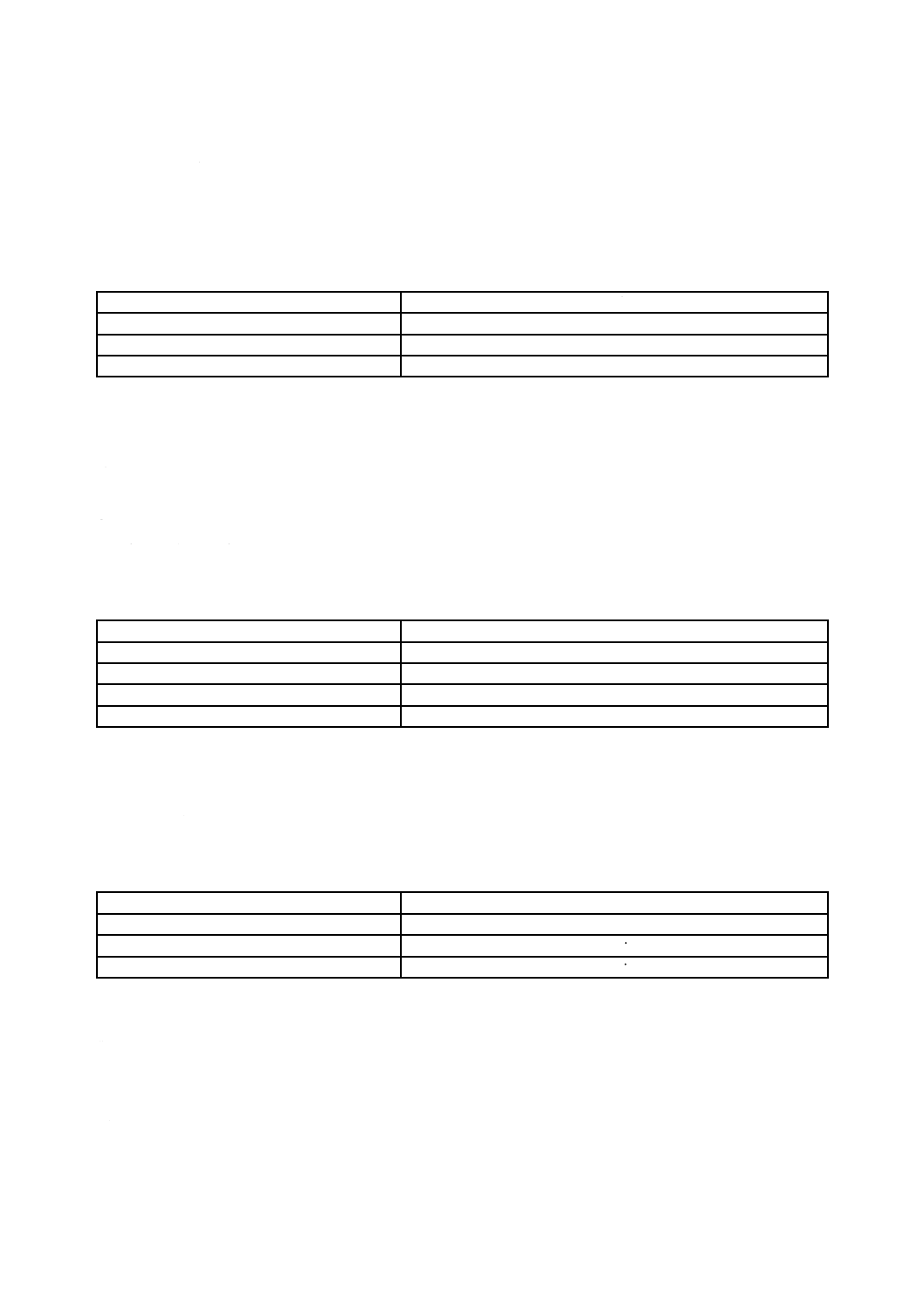

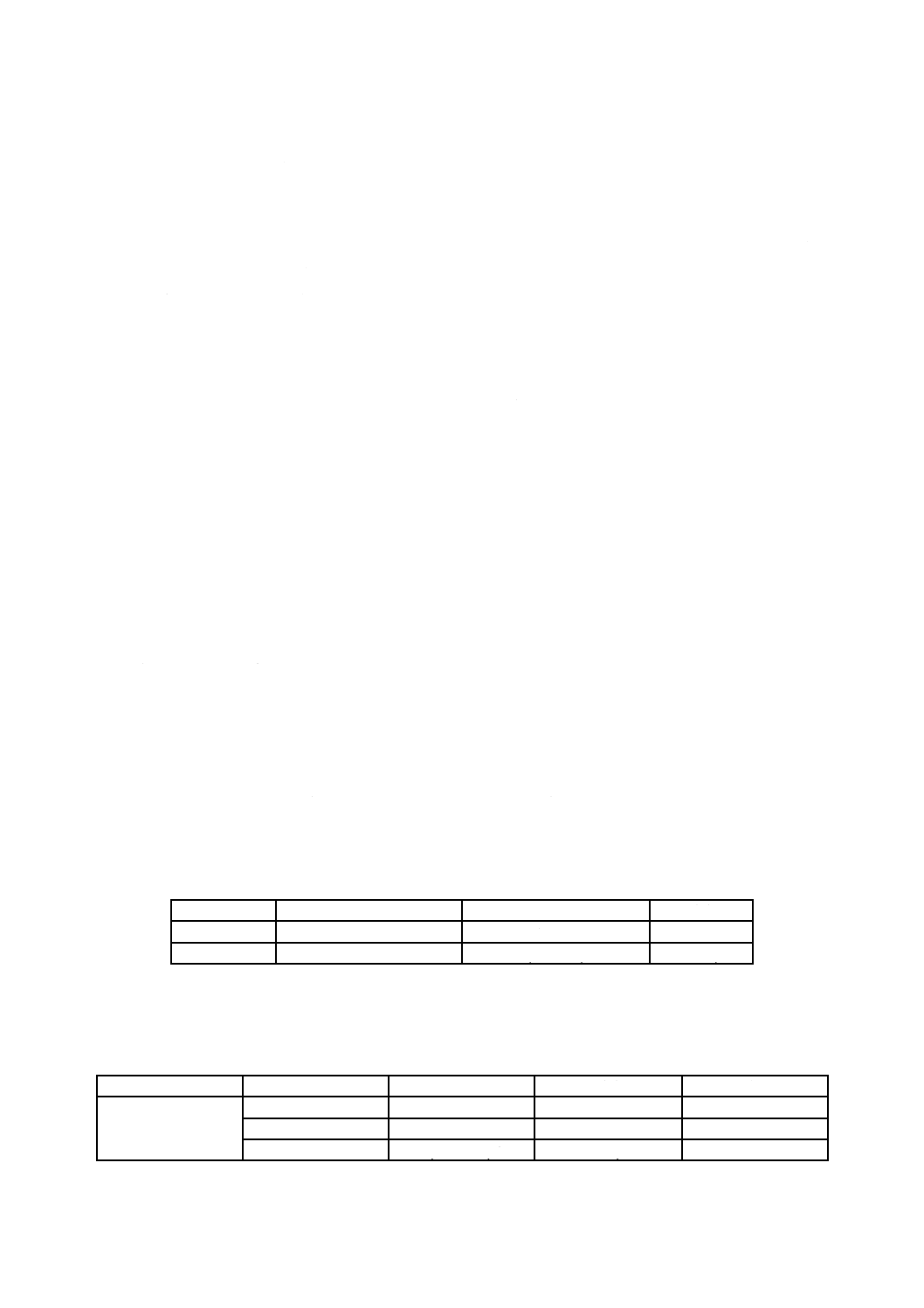

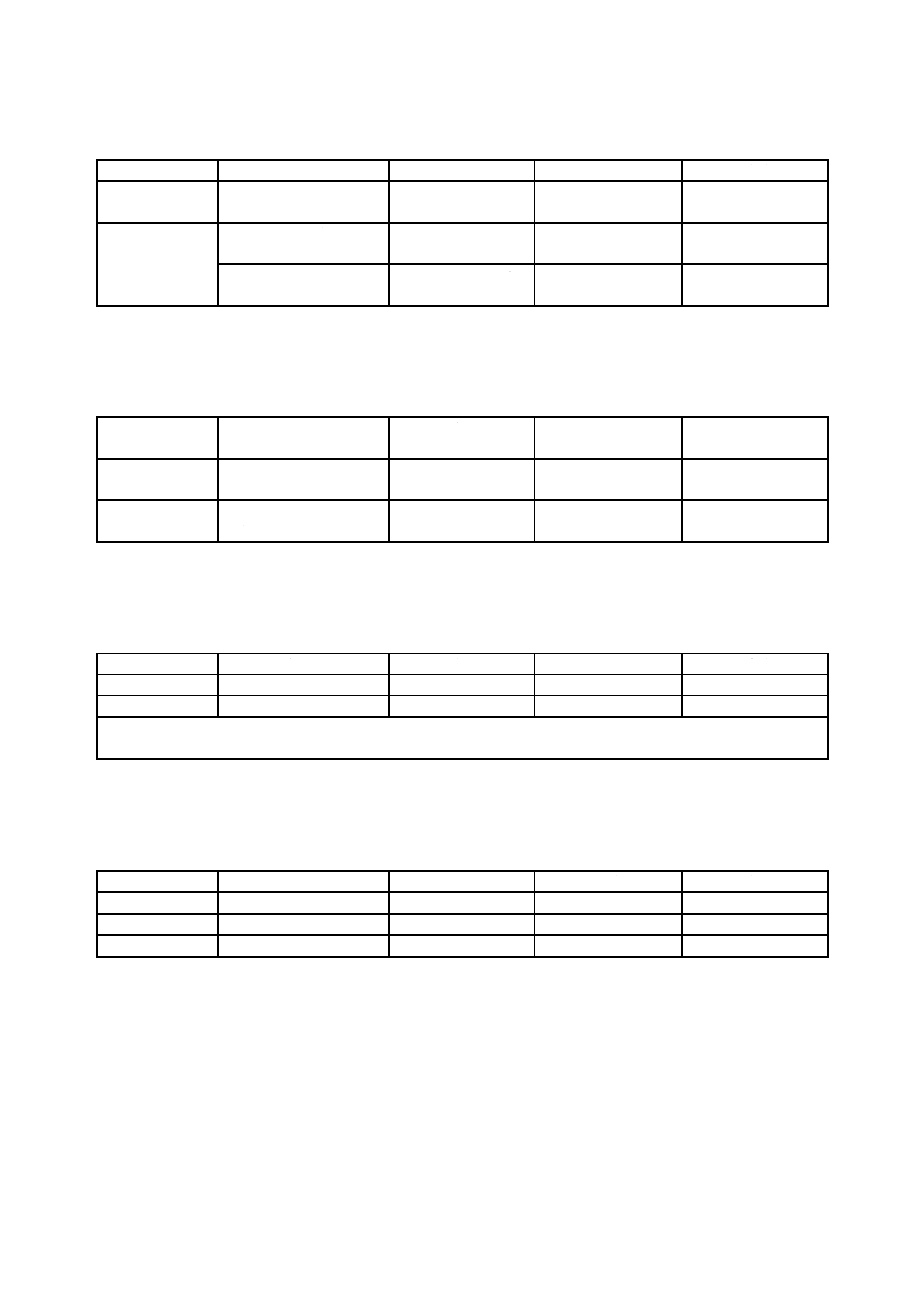

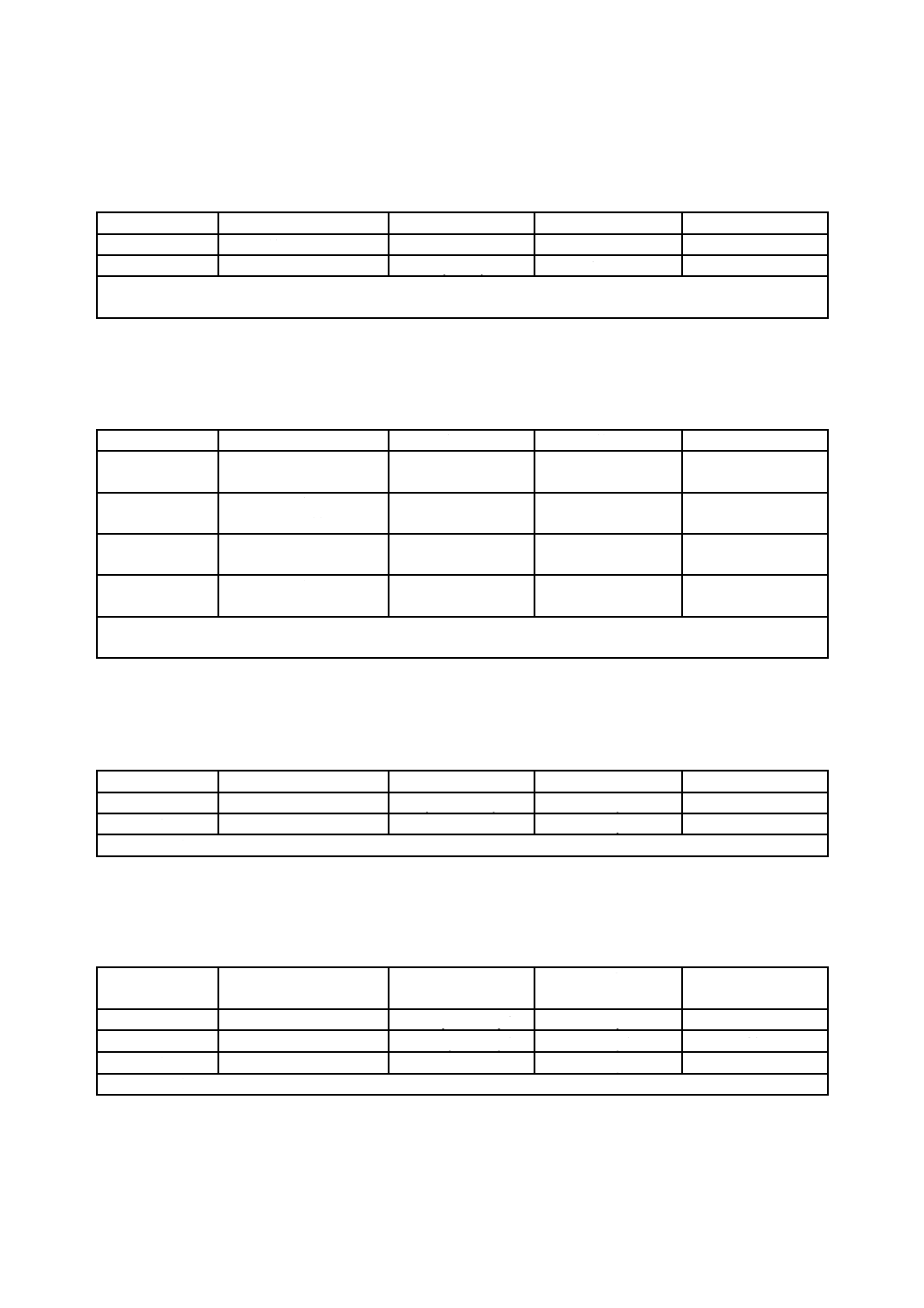

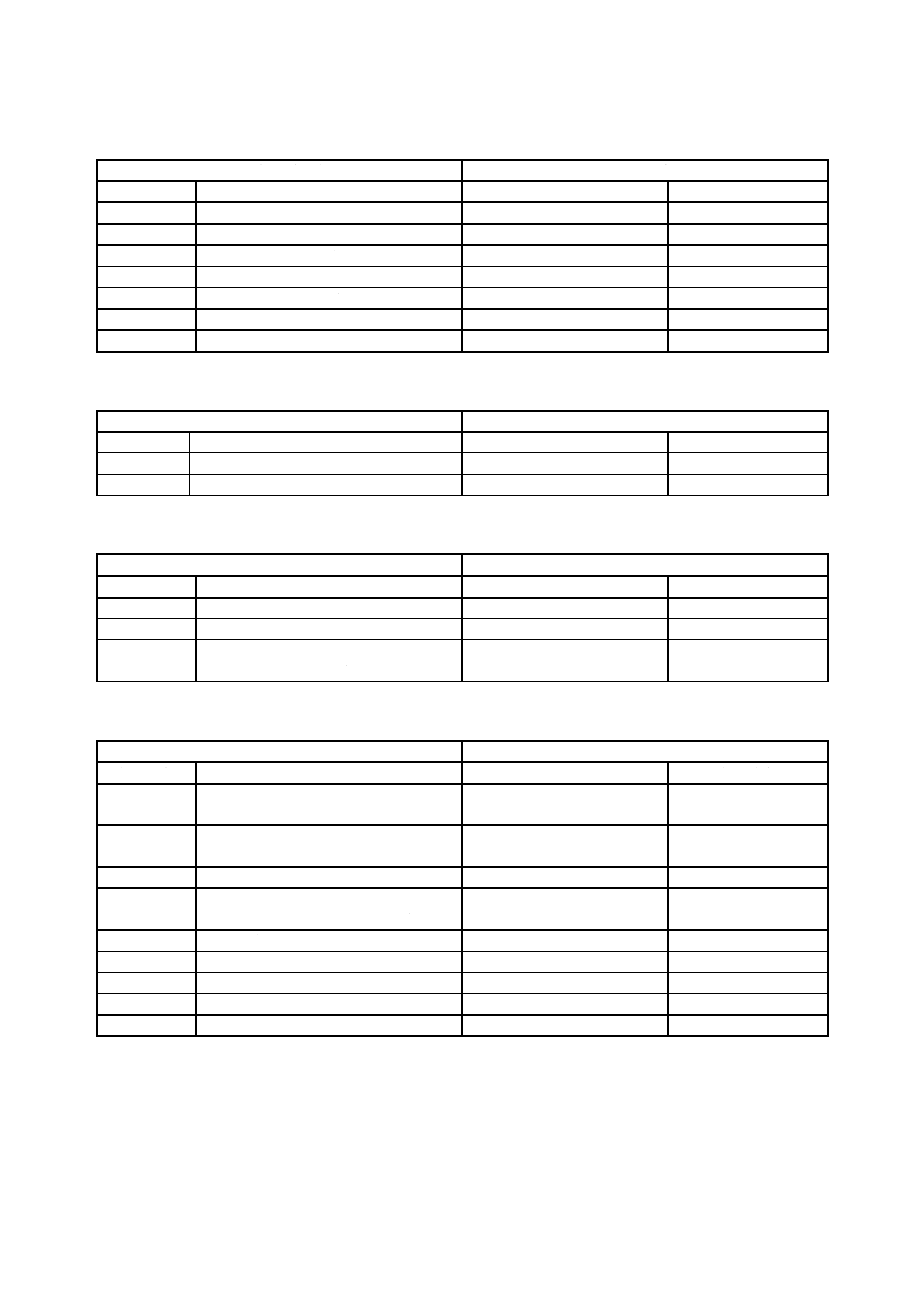

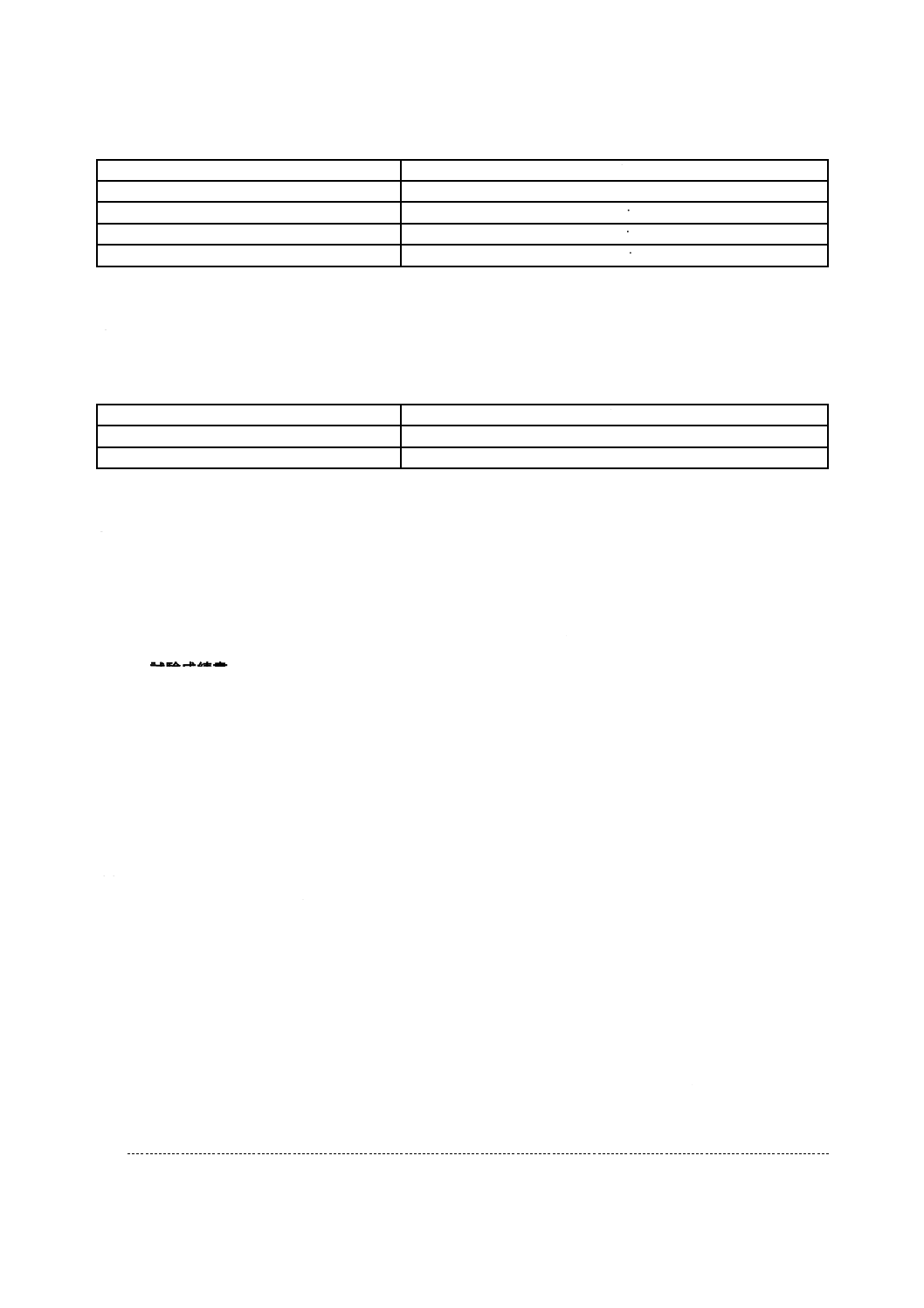

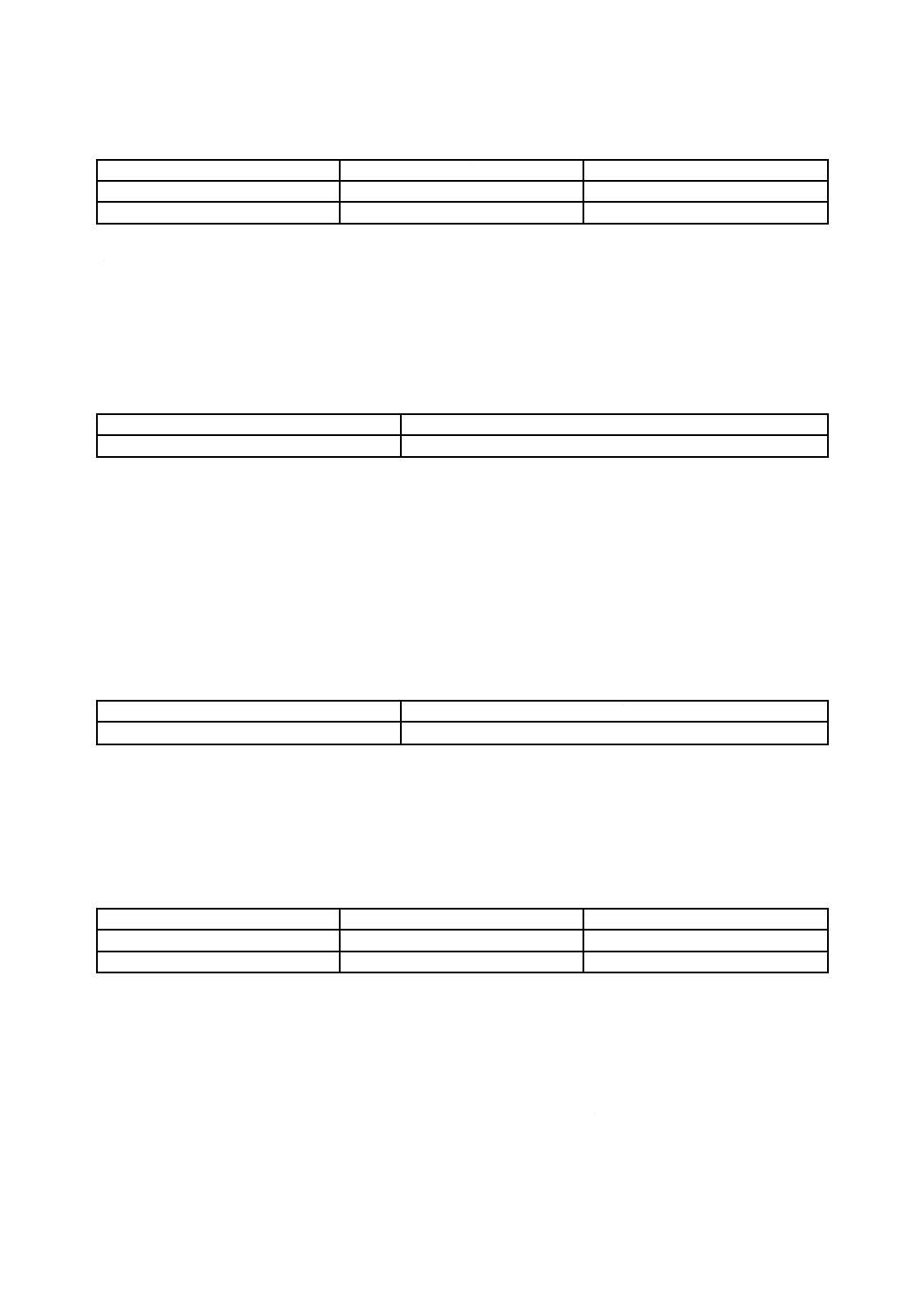

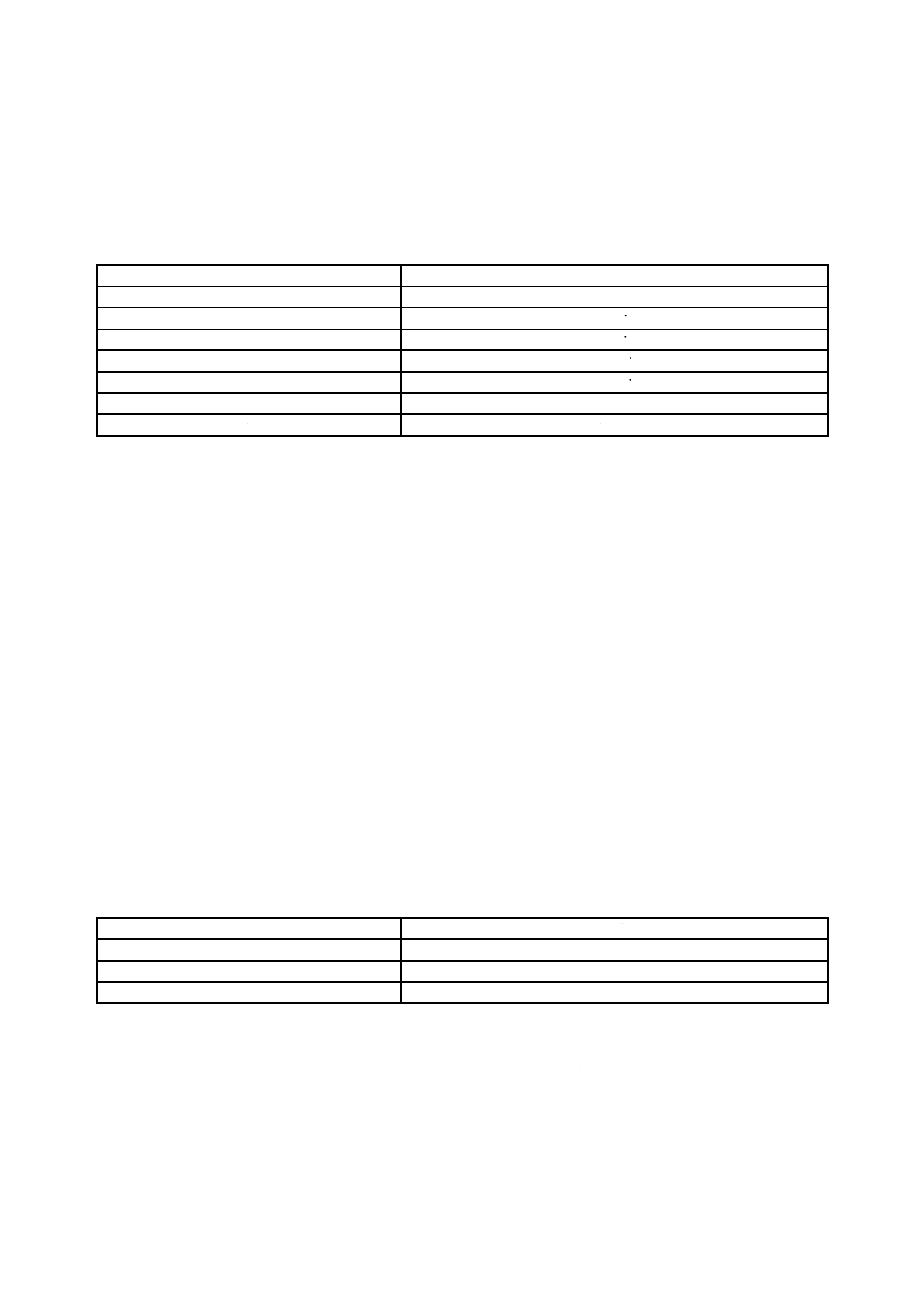

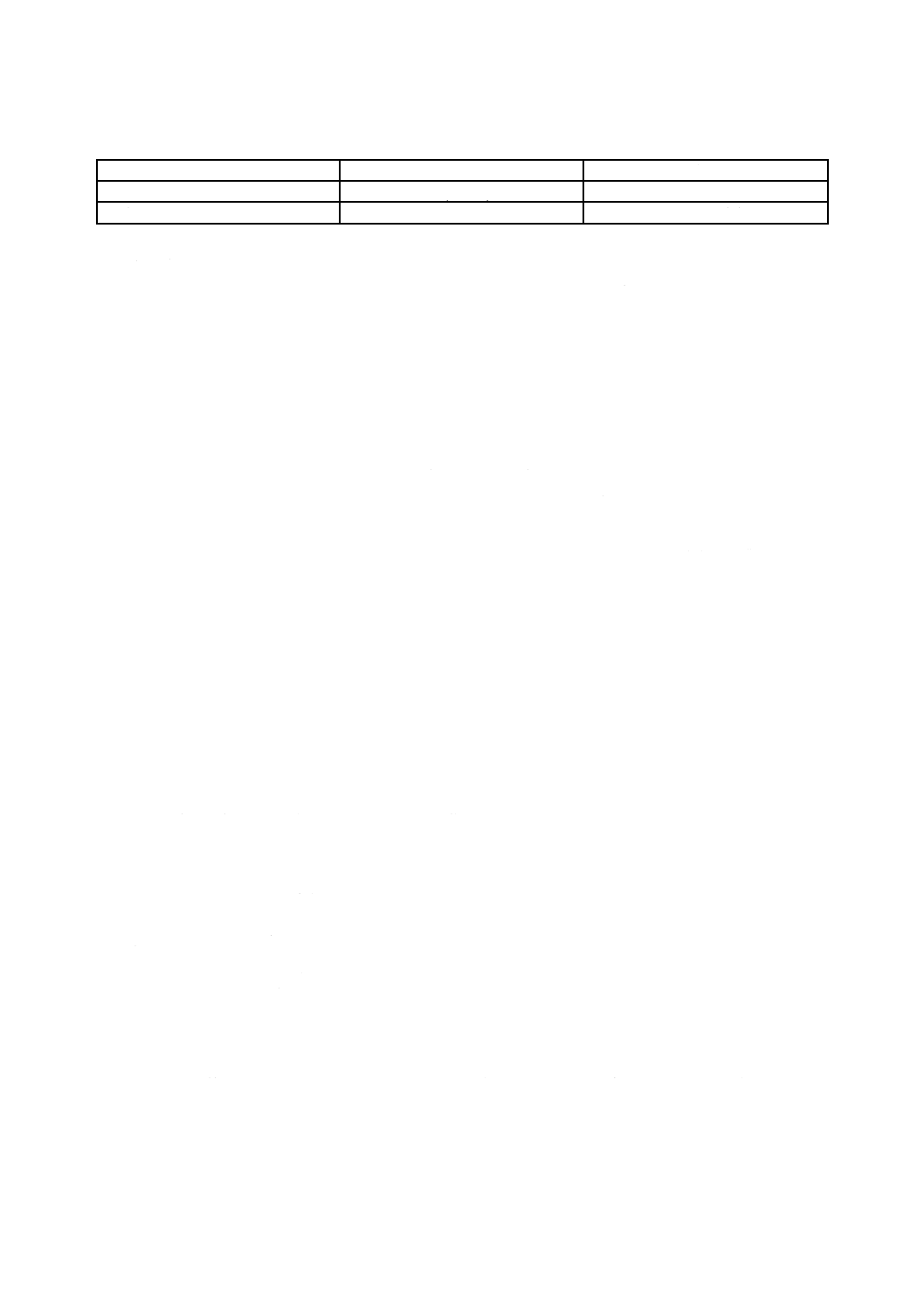

表1−VCC端子電圧及びタイミング

パラメタ

動作クラス

範囲

精度

UCC

クラスA,B,C

−1 V〜6 V

±20 mV

tR,tF

クラスA,B,C

0 μs〜500 μs

±100 μs

4.7.1.2

ICCの測定

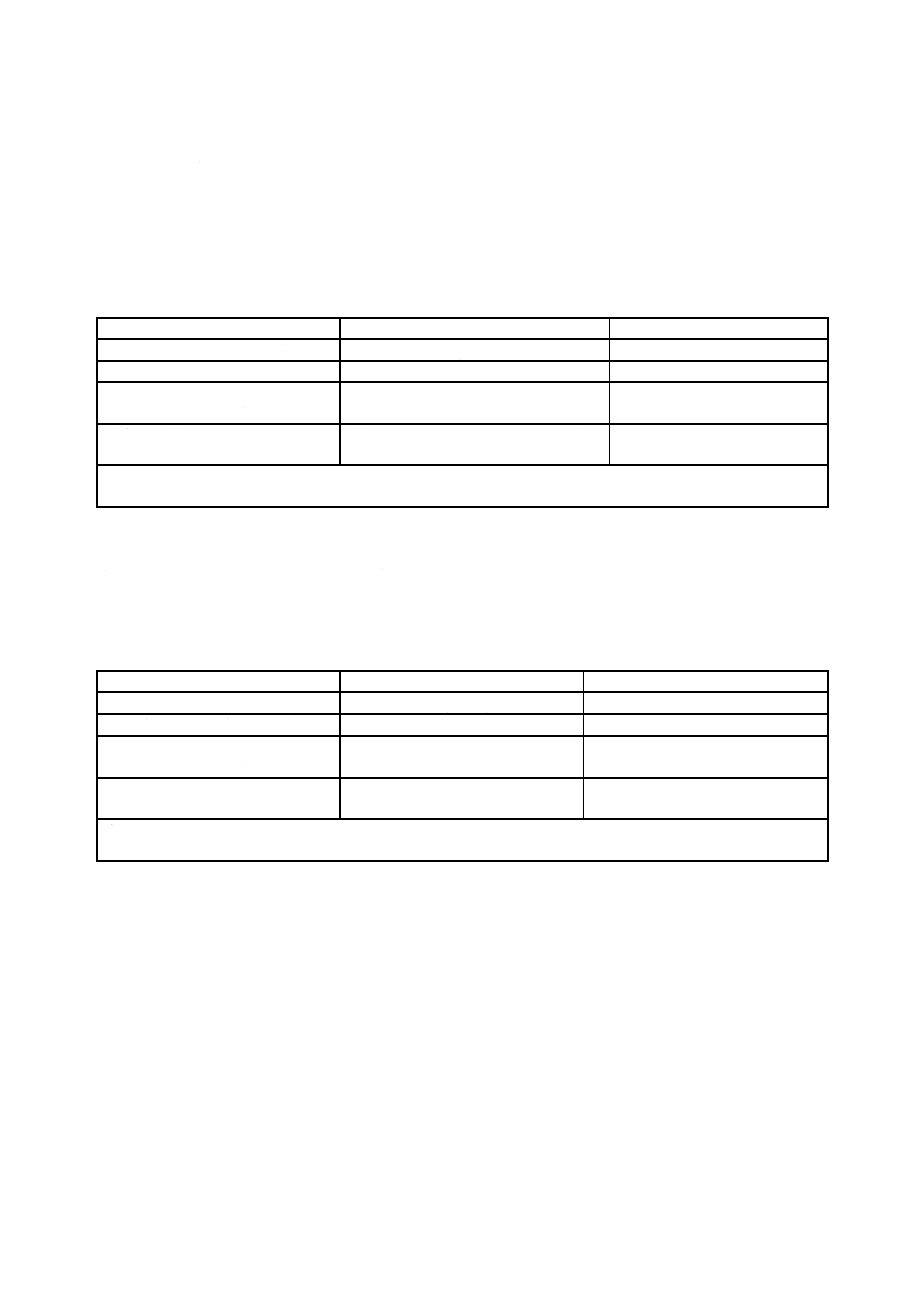

表2−ICCパラメタ

特性

モード

範囲

精度

分解能

ICC

スパイク電流測定時

0 mA〜200 mA

±2 mA

20 ns

活性化状態

0 mA〜100 mA

±1 mA

1 ms間以上の平均

クロック停止時

0 μA〜200 μA

±10 μA

1 ms間以上の平均

4

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.7.1.3

SPU(C6)端子電圧の生成

5.5及びJIS X 6320-3による。

4.7.1.4

RST端子電圧及びタイミングの生成

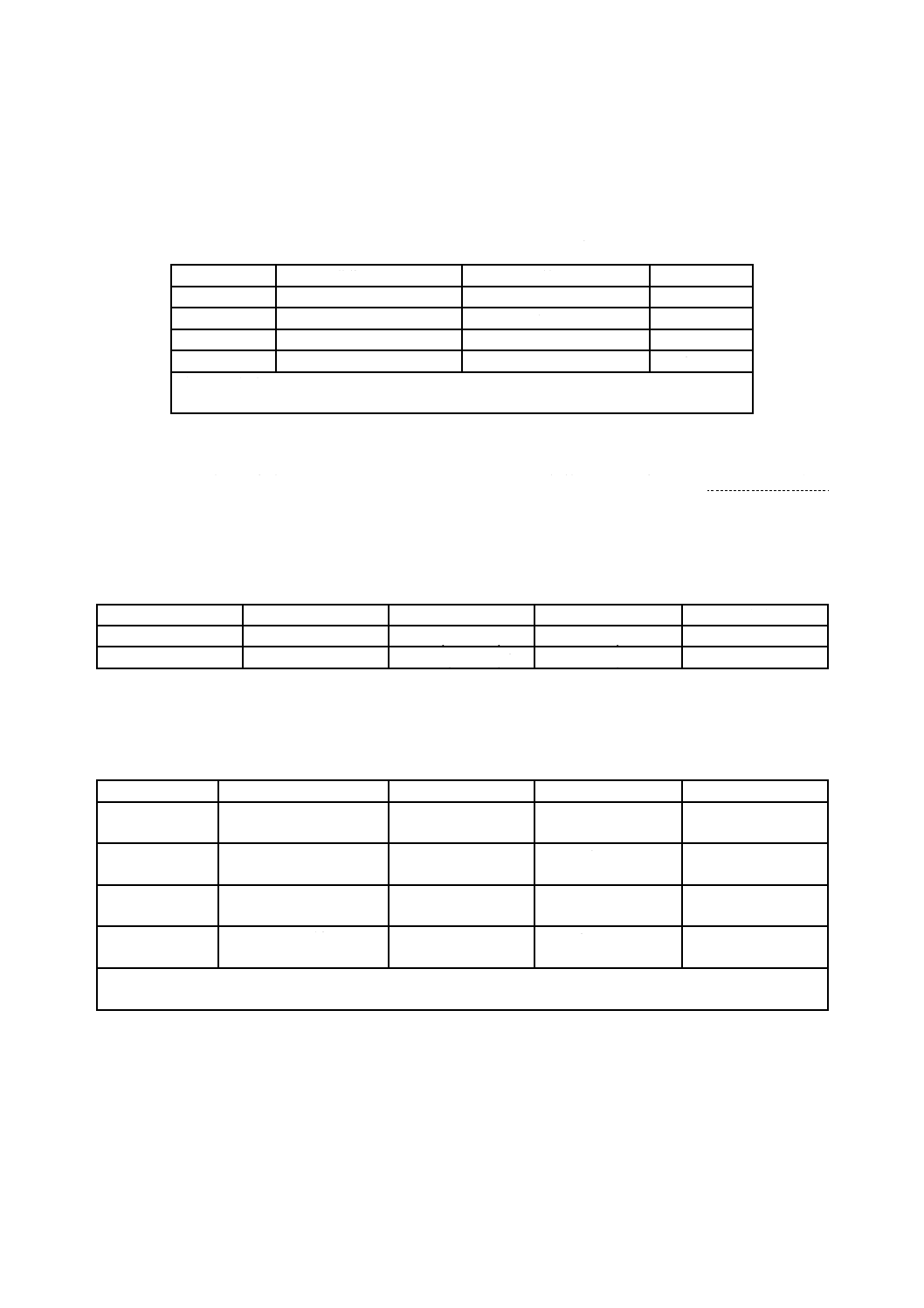

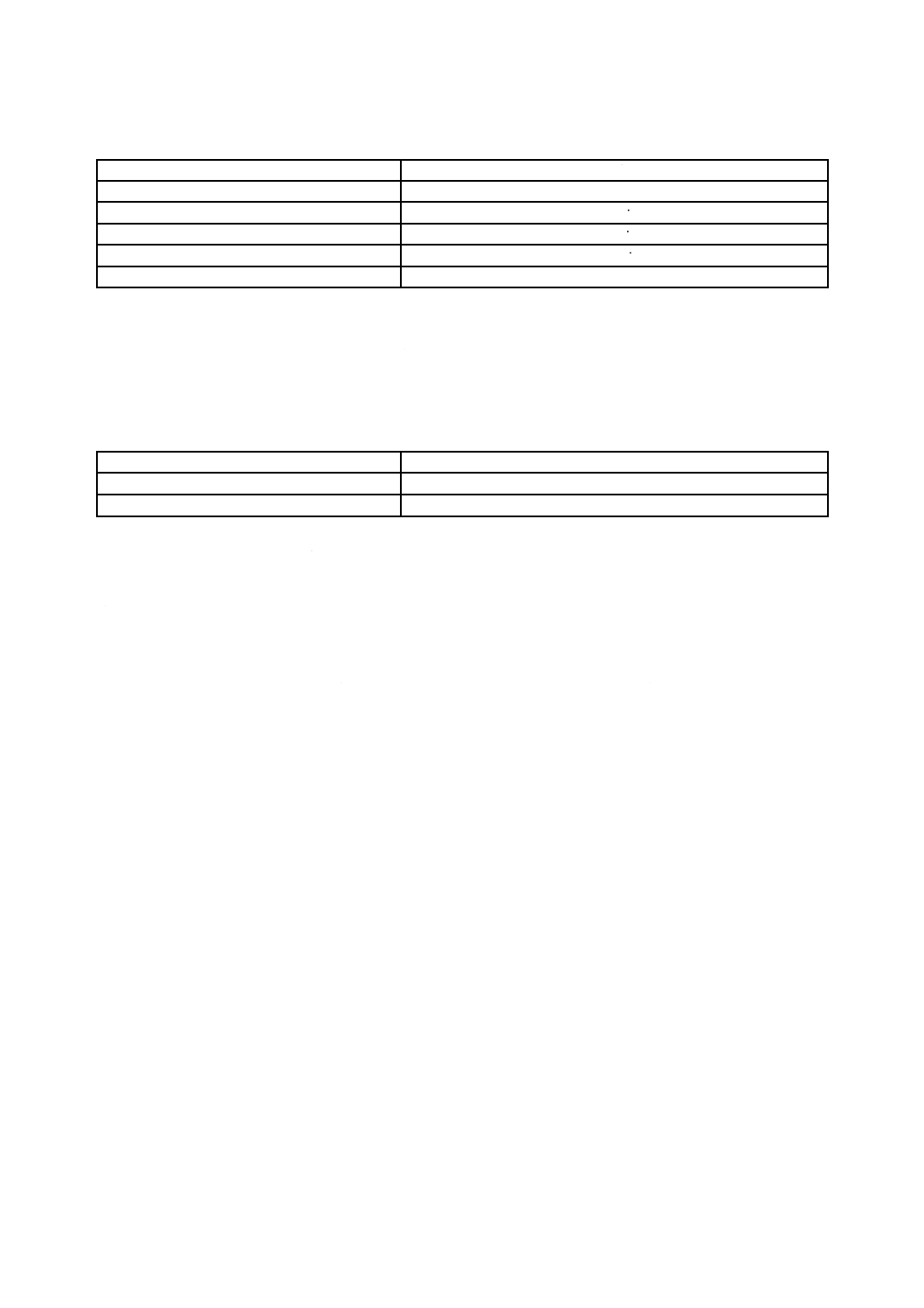

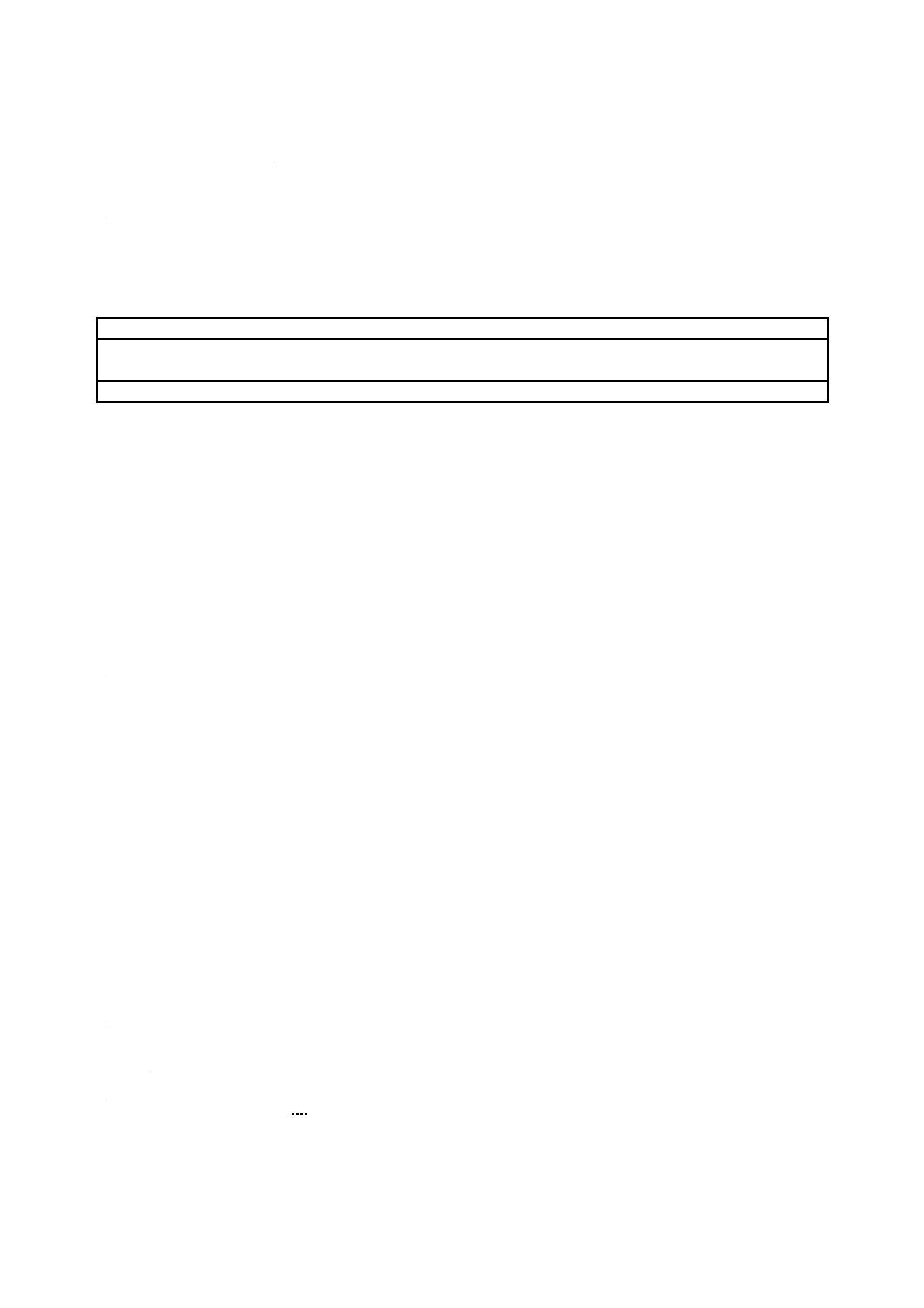

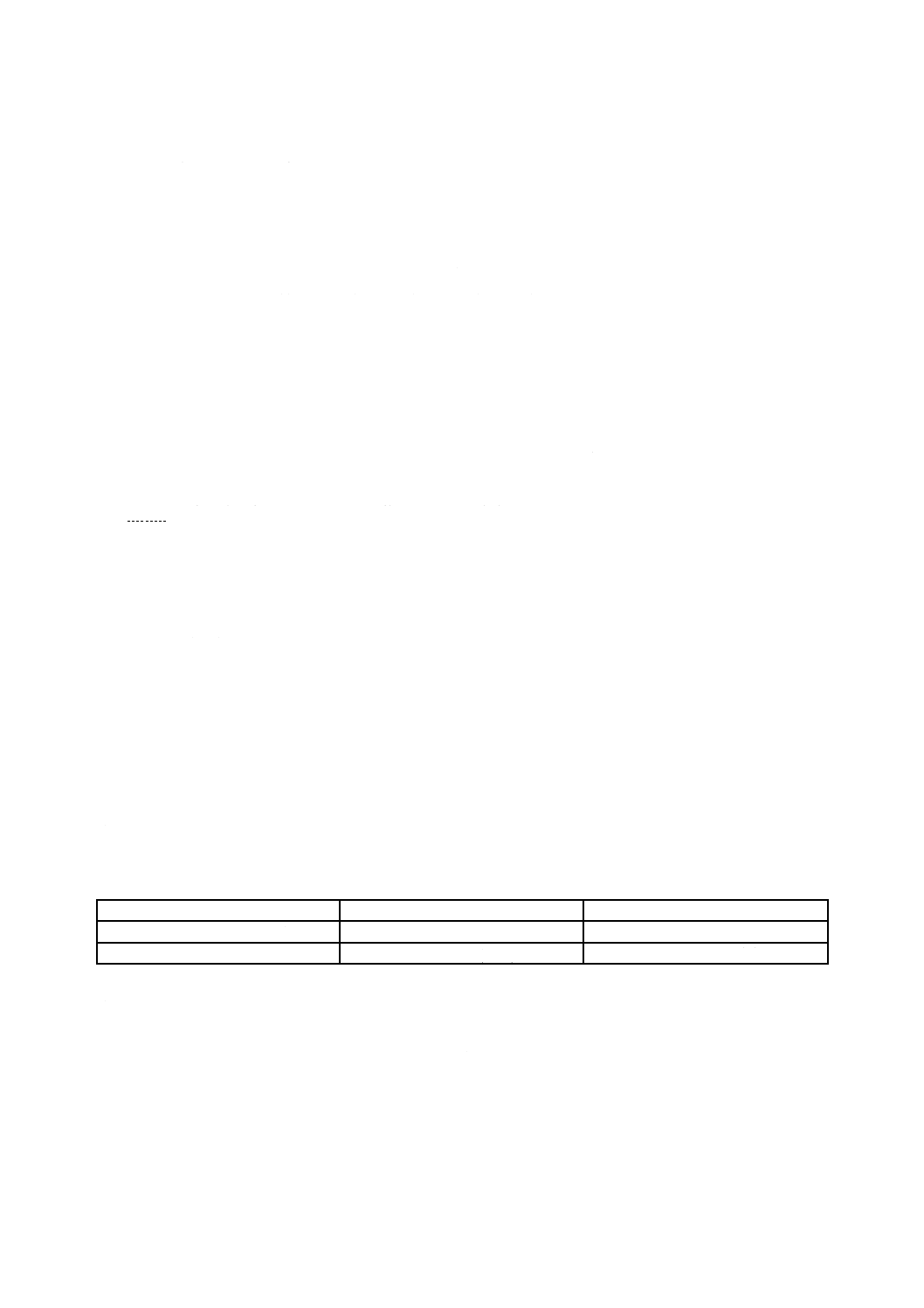

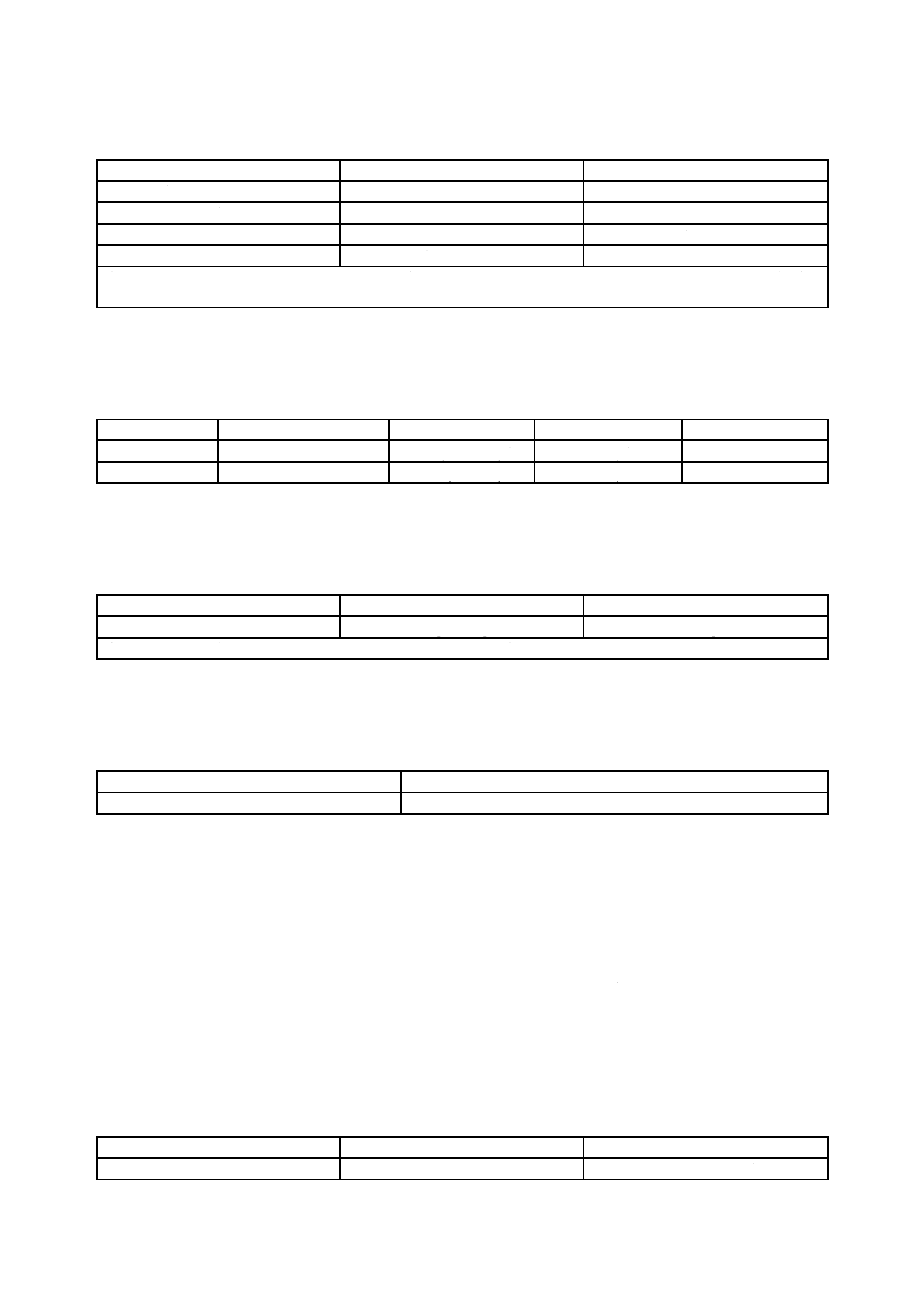

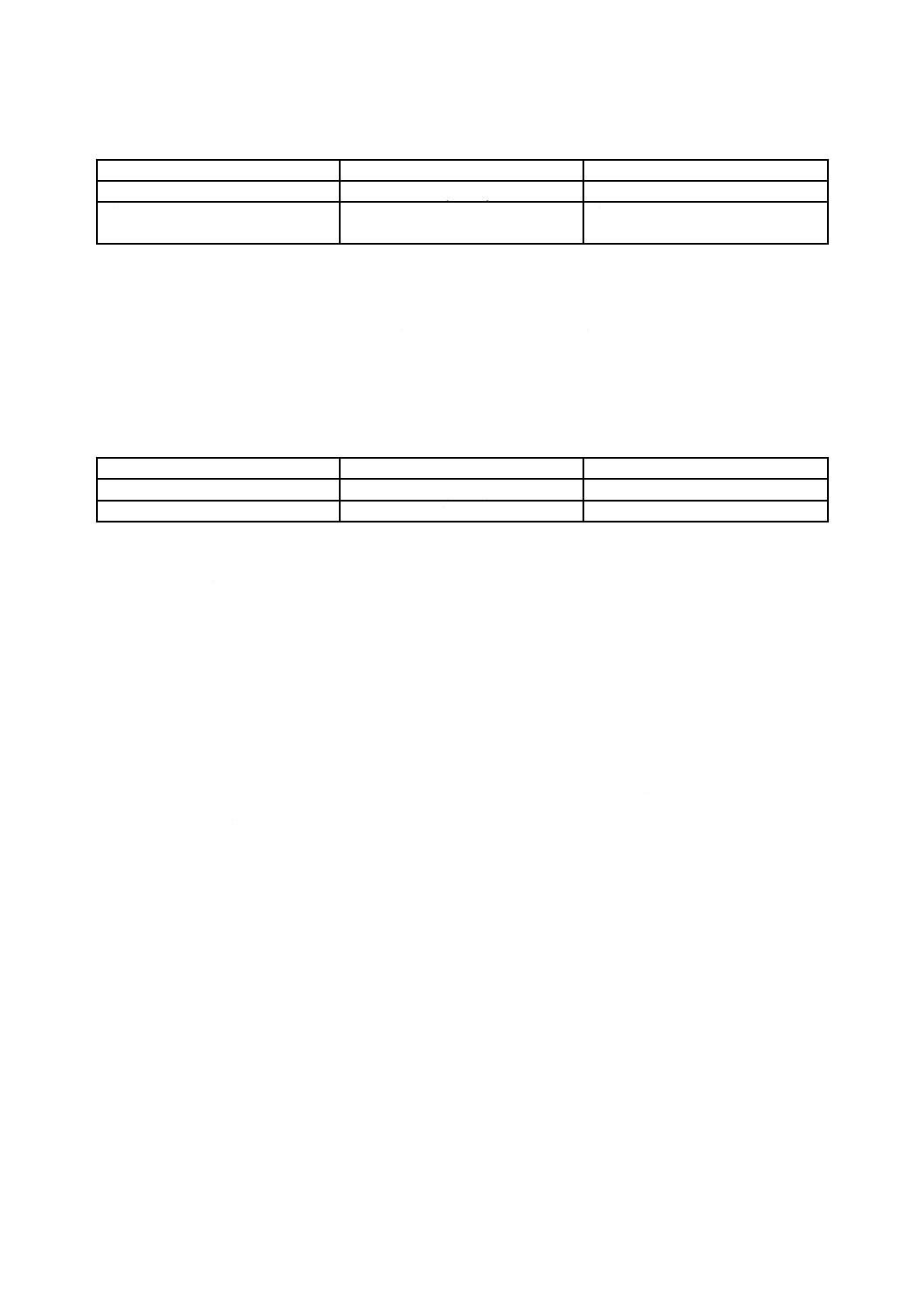

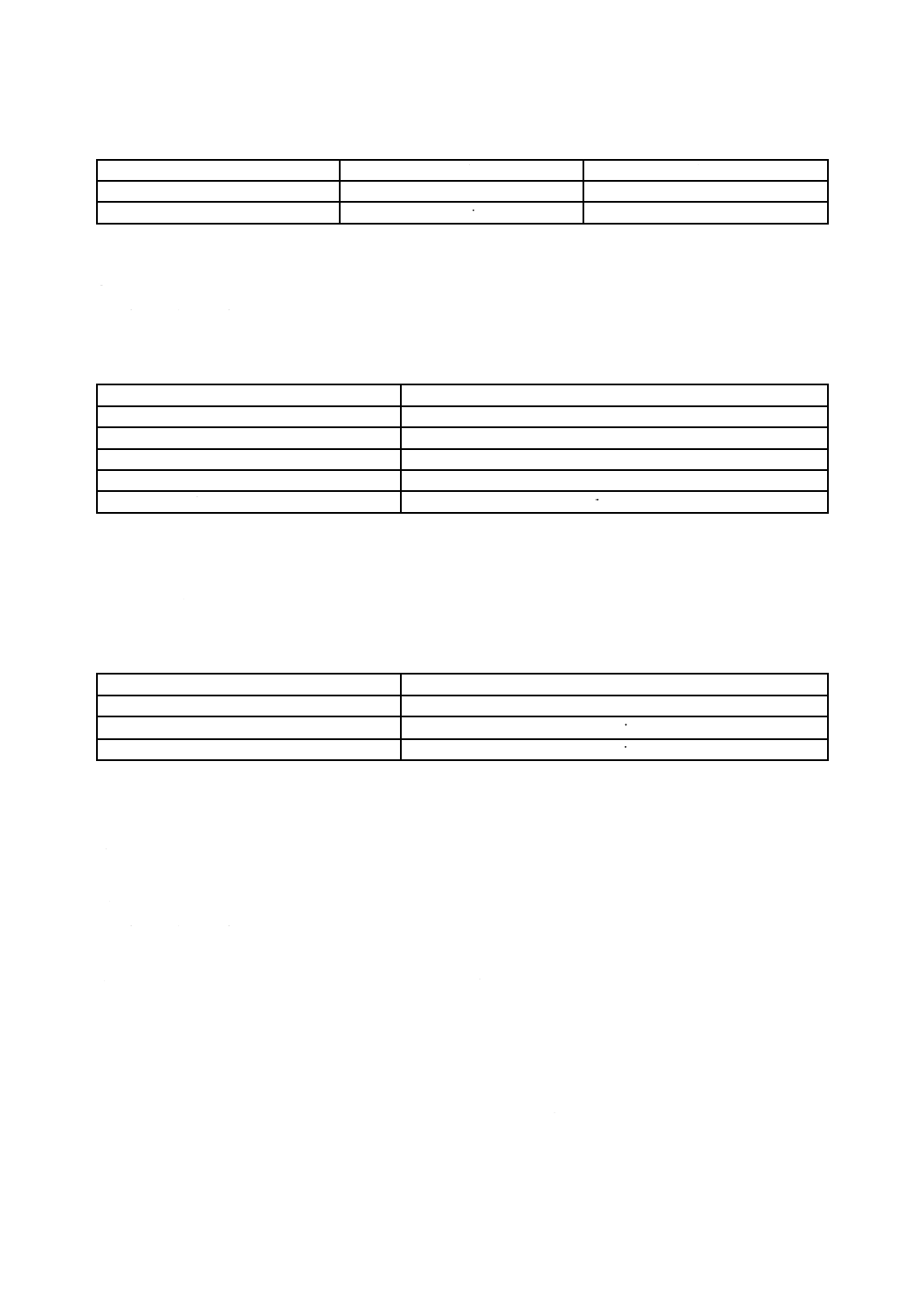

表3−RST端子電圧及びタイミング

パラメタ

動作クラス

範囲

精度

UIH,UIL

クラスA,B

−1 V〜6 V

±20 mV

UIH

クラスC

−1 V〜2 V

±20 mV

UIL

クラスC

−1 V〜1 V

±20 mV

tR,tF

0 μs〜2 μs

±20 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上

がり及び立下がり)時間を示す。

注記 表3の内容は,試験を実施するための基本条件であり,試験装置設定値の可変範囲を示してい

る。試験を実施するに当たっては,動作クラス別に電気的特性を規定したJIS X 6320-3を参照

することが望ましい。

4.7.1.5

RST端子電流の測定

表4−RST端子電流

特性

モード

範囲

精度

分解能

IIH

活性化状態

−30 μA〜200 μA

±10 μA

100 ns

IIL

活性化状態

−200 μA〜30 μA

±10 μA

100 ns

4.7.1.6

ICカードの受信モードにおけるI/O端子電圧及びタイミングの生成

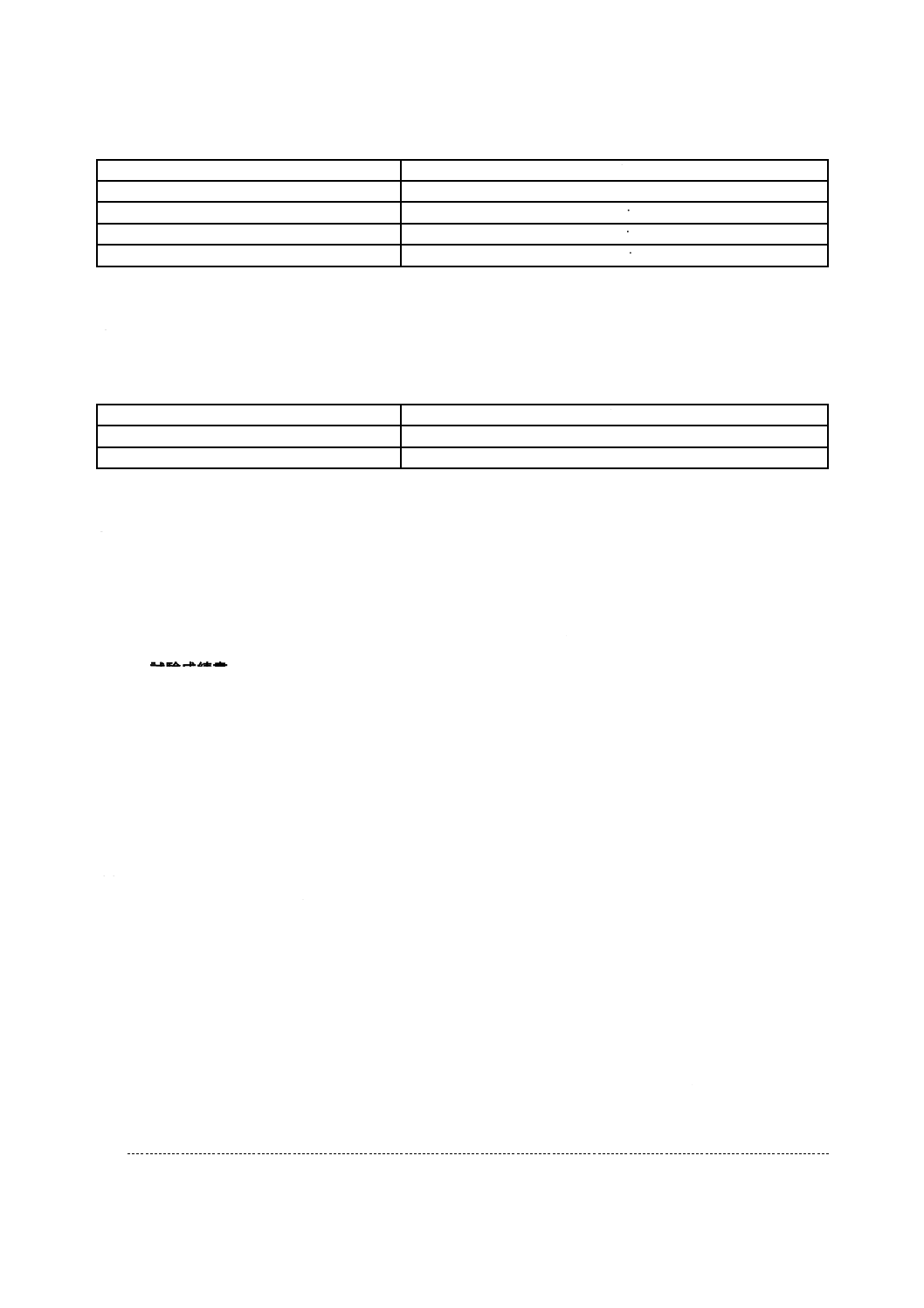

表5−I/O端子電圧及びタイミング

パラメタ

モード

動作クラス

範囲

精度

UIH,UIL

ICカード:受信モード

試験装置:送信モード

クラスA,B

−1 V〜6 V

±20 mV

UIH

ICカード:受信モード

試験装置:送信モード

クラスC

−1 V〜2 V

±20 mV

UIL

ICカード:受信モード

試験装置:送信モード

クラスC

−1 V〜1 V

±20 mV

tR,tF

ICカード:受信モード

試験装置:送信モード

0 μs〜2 μs

±100 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上がり及び立下がり)時間

を示す。

4.7.1.7

ICカードの受信モードにおけるI/O端子電流の測定

5

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

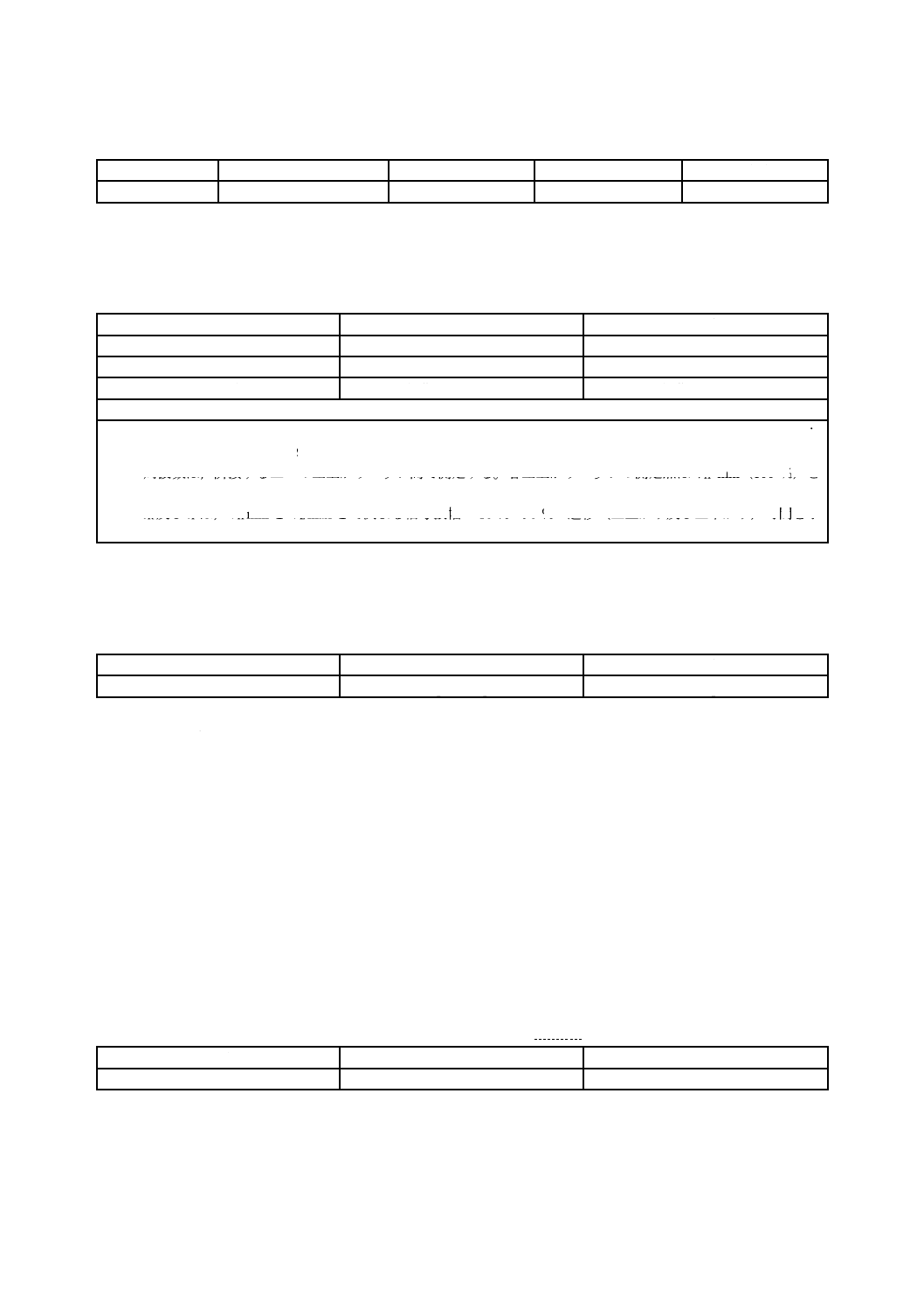

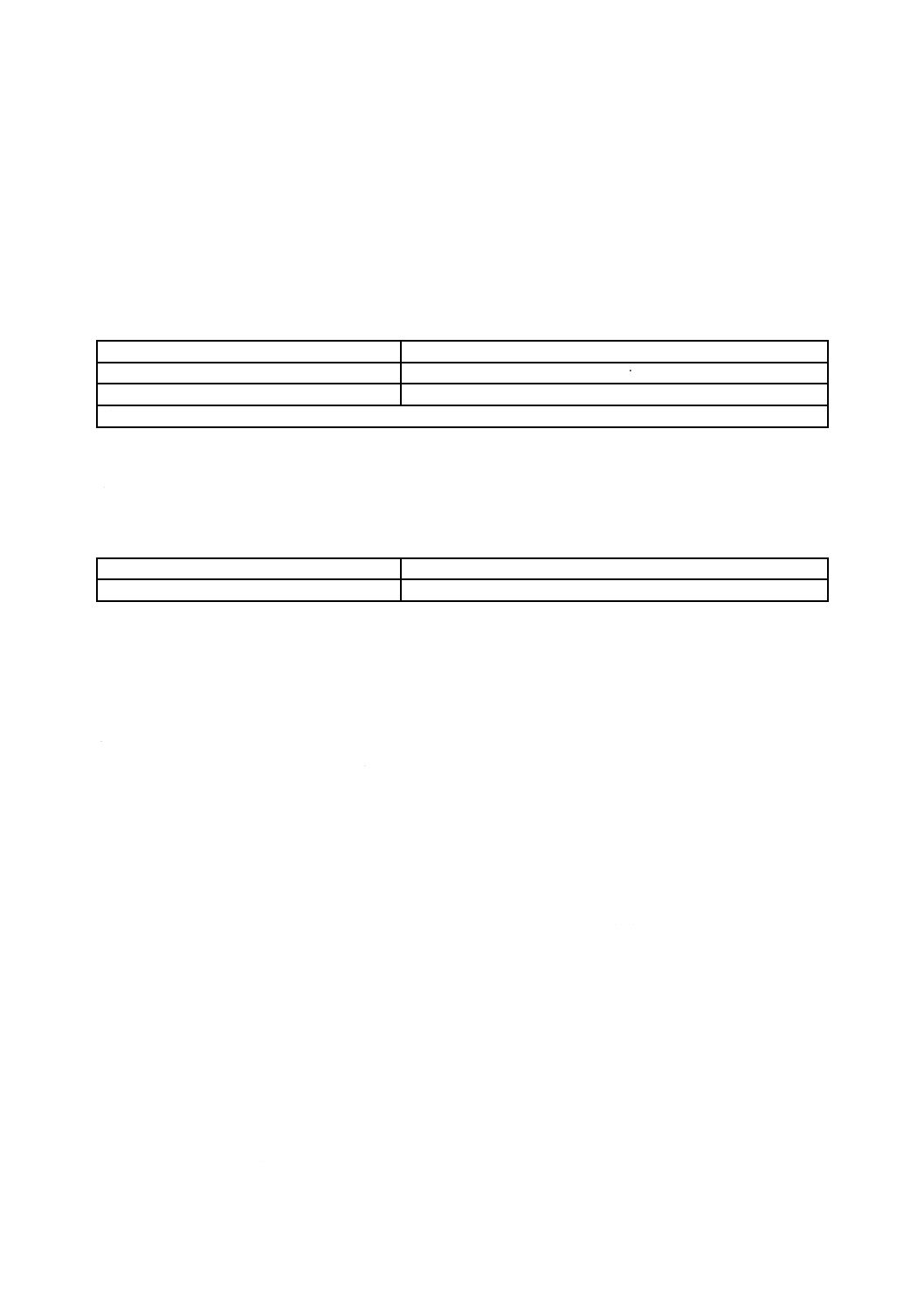

表6−I/O端子電流(受信モード)

パラメタ

モード

範囲

精度

分解能

IIH

ICカード:受信モード

試験装置:送信モード

−300 μA〜30 μA

±10 μA

100 ns

IIL

ICカード:受信モード

試験装置:送信モード

−1.5 mA〜−0.2 mA

±50 μA

100 ns

ICカード:受信モード

試験装置:送信モード

−200 μA〜30 μA

±10 μA

100 ns

4.7.1.8

I/O端子電流の生成

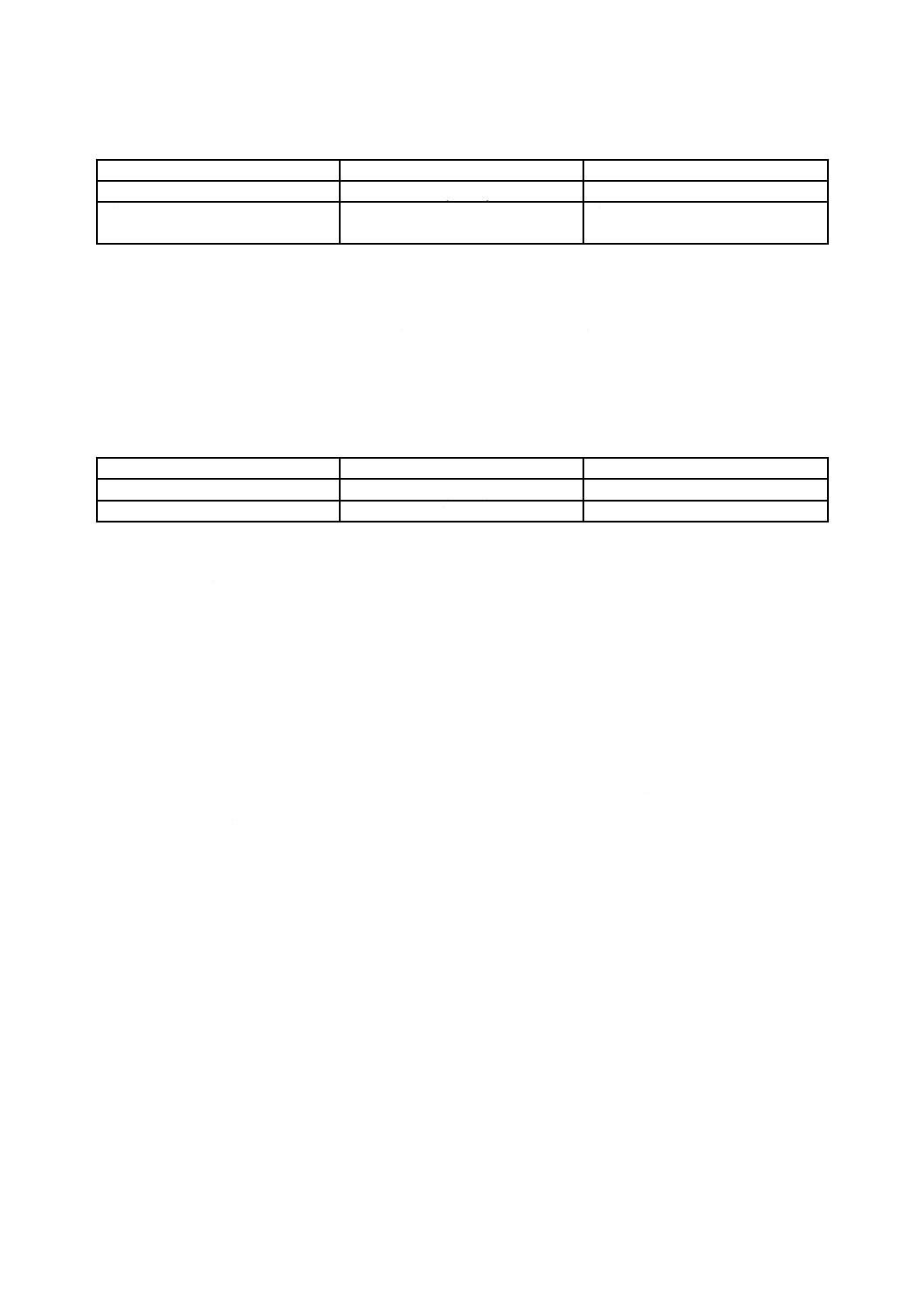

表7−I/O端子電流

パラメタ

モード

範囲

精度

レベルに達した後の

安定化時間

IOH

ICカード:送信モード

試験装置:受信モード

VCCに20 kΩで接続

又は同等の回路

±200 Ω

IOL

ICカード:送信モード

試験装置:受信モード

0 mA〜1.5 mA

±50 μA

100 ns未満

4.7.1.9

I/O端子電圧及びタイミングの測定

表8−I/O端子電圧及びタイミング

特性

動作クラス

範囲

精度

分解能

UIH,UIL

クラスA,B,C

−1 V〜6 V

±20 mV

20 ns

tR,tF

0 μs〜2 μs

±20 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上がり及び立下がり)時間

を示す。

4.7.1.10 CLK端子電圧の生成

表9−CLK端子電圧

特性

動作クラス

範囲

精度

分解能

UIH,UIL

クラスA,B

−1 V〜6 V

±20 mV

20 ns

UIH

クラスC

−1 V〜2 V

±20 mV

20 ns

UIL

クラスC

−1 V〜2 V

±20 mV

20 ns

4.7.1.11 CLK端子の波形の生成(一周期の測定)

6

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

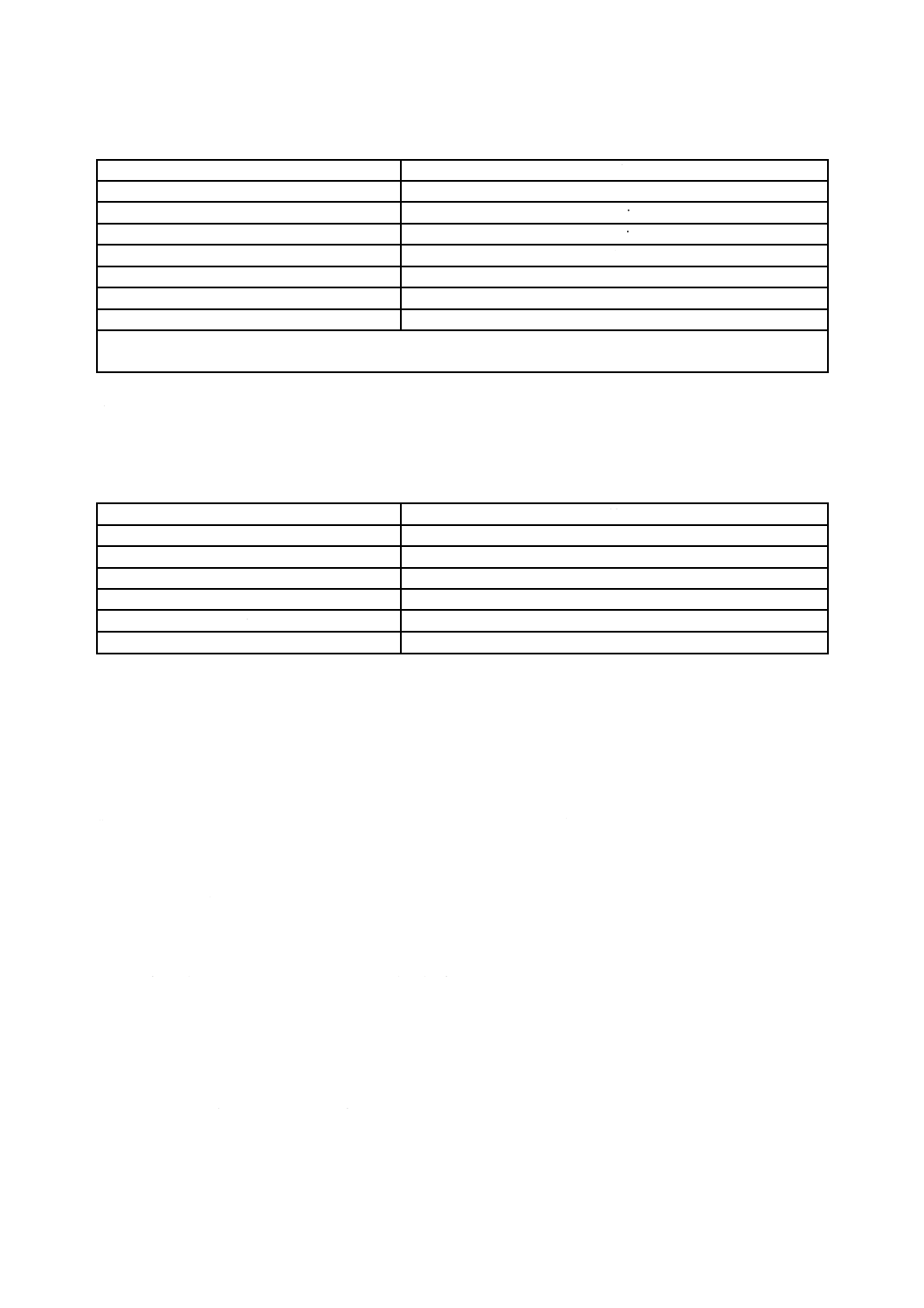

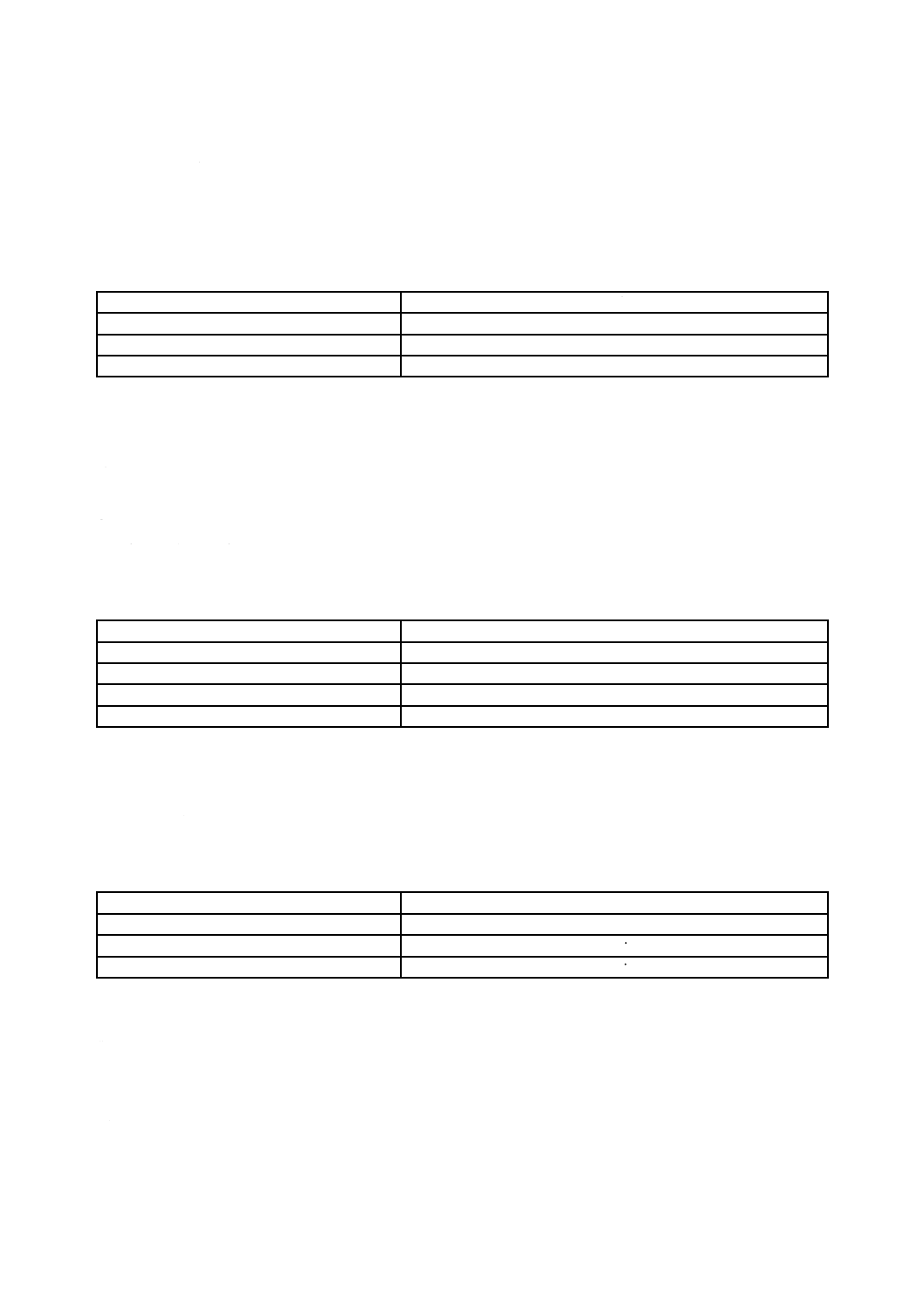

表10−CLK端子の波形

特性

範囲

精度

デューティサイクル

周期の35 %〜65 %

±5 ns

周波数

0.5 MHz〜5.5 MHz

±5 kHz

周波数

5 MHz〜20.5 MHz

±50 kHz

tR,tF

周期の1 %〜10 %

±5 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上がり及び立下がり)時間

を示す。

4.7.1.12 CLK端子電流の測定

表11−CLK端子電流

特性

動作クラス

範囲

精度

分解能

IIH

活性化状態

−30 μA〜150 μA

±10 μA

20 ns

IIL

活性化状態

−150 μA〜30 μA

±10 μA

20 ns

4.7.1.13 RST,CLK及びI/O端子の静電容量の測定

表12−外部端子の静電容量

特性

範囲

精度

C

0 pF〜50 pF

±5 pF

注記 外部端子の負荷容量は,外部端子とGND端子との間で測定する。

4.7.1.14 外部端子の連続した活性化及び非活性化の生成

表13−活性化及び非活性化

信号切替え時間の範囲

精度

0 s〜1 s

±200 ns(又は1クロック周期のいずれか小さい値)

4.7.1.15 プロトコルのエミュレート

ICカード試験装置は,代表的なアプリケーション固有の通信を実行するときに要求されるプロトコル

T=0,T=1及びIFDのアプリケーションをエミュレートできなければならない。

注記 特定の機能がICカードに実装されていない場合には,ICカード試験装置に,対応する試験能

力を備えていることを要求しない(例えば,ICカードで実装されないT=0プロトコル)。

4.7.1.16 ICカードの受信モードにおけるI/Oキャラクタの生成タイミング

ICカード試験装置は,JIS X 6320-3に従い,I/O端子にビット列を生成できなければならない。

開始ビットの長さ,保護時間,誤り信号などの全てのタイミングパラメタを,設定できなければならな

い。

表14−I/Oキャラクタの生成タイミングの精度(受信モード)

記号

意味

精度

εt

全てのタイミングパラメタ

±4クロック周期

7

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.7.1.17 I/Oプロトコルの測定及び監視

ICカード試験装置は,CLK周波数に関係してI/O端子の論理的な“低”レベル状態及び“高”レベル状

態のタイミングを測定し,監視することができなければならない。

表15−タイミング特性

特性

精度

全てのタイミングパラメタ

±2クロック周期

4.7.1.18 プロトコル分析

ICカード試験装置は,JIS X 6320-3に適合したT=0プロトコル及びT=1プロトコルに一致するビット列

の分析のため,並びに上位のプロトコル及びアプリケーションの確認のために論理的なデータフローを抽

出できなければならない。

注記 特定の機能がICカードに実装されていない場合には,ICカード試験装置に,対応する試験能

力を備えていることを要求しない(例えば,ICカードで実装されないT=0プロトコル)。また,

試験装置は拡張された能力をもっていてもよい。例えば,ICカードが標準のREAD BINARYコ

マンドをサポートしていない場合,ケース2のいずれかのコマンド(JIS X 6320-4参照)を生

成してもよい。

4.7.2

接続装置を試験するための装置(IFD試験装置)

4.7.2.1

VCC端子電流(ICC)の生成

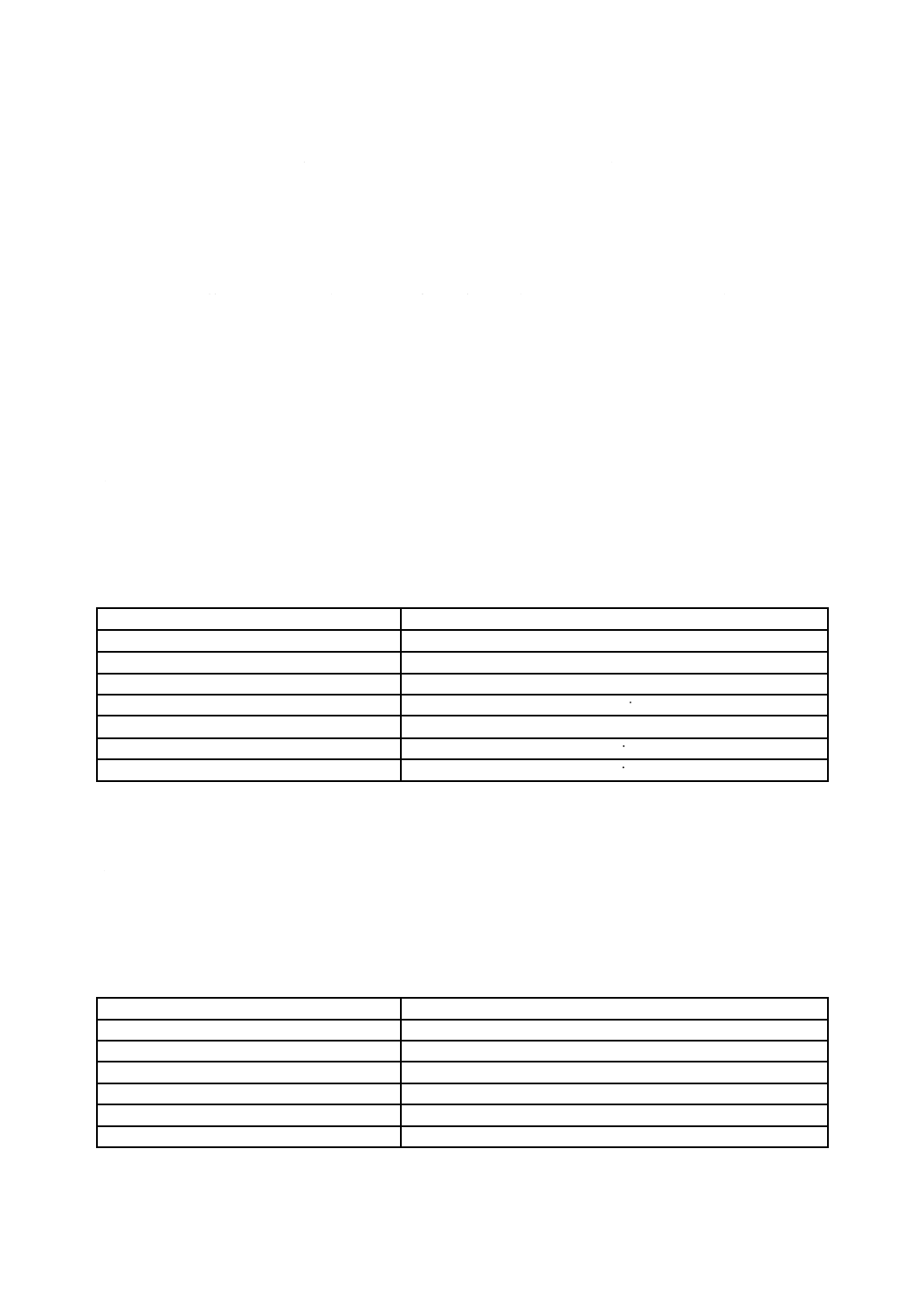

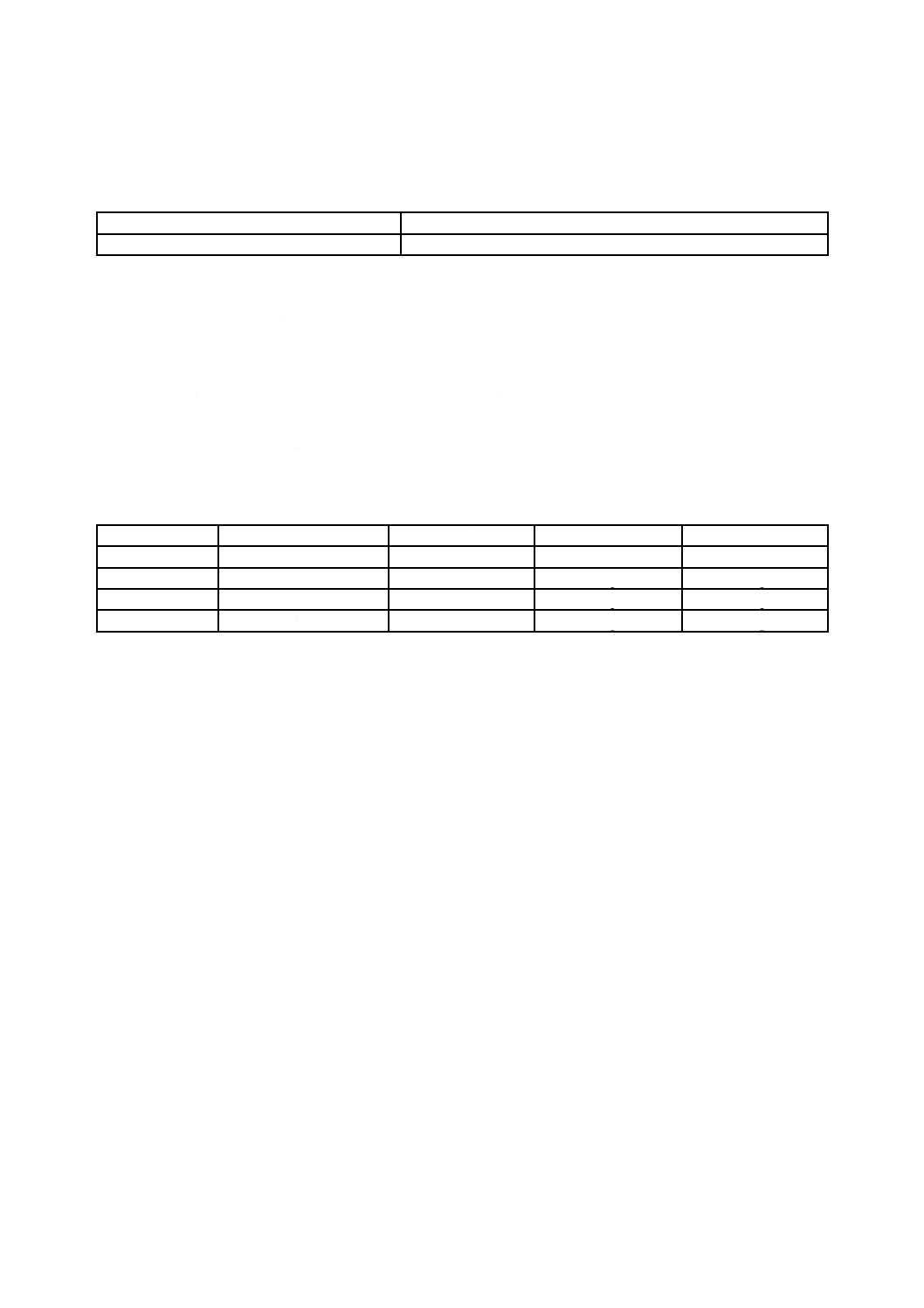

表16−VCC端子電流

パラメタ

モード

範囲

精度

レベルに達した後の

安定化時間

ICC

スパイク生成状態

0 mA〜120 mA

±2 mA b)

< 100 ns

活性化状態

0 mA〜70 mA

±1 mA

< 100 ns

クロック停止状態

0 mA〜1.2 mA

±10 μA

< 100 ns

非活性化状態a)

−1.2 mA〜0 mA

±10 μA

< 100 ns

tR,tF

100 ns

±50 ns

パルス長

100 ns〜500 ns

±50 ns

停止状態の長さ

(周期的)

100 ns〜1 000 ns

±50 ns

停止状態の長さ

(ランダム)

10 μs〜2 000 μs

±1 μs

注a) 最大出力電圧は,5 Vに制限しなければならない。

b) スパイク生成のための動的条件。

4.7.2.2

VCC端子電圧(UCC)及びタイミングの測定

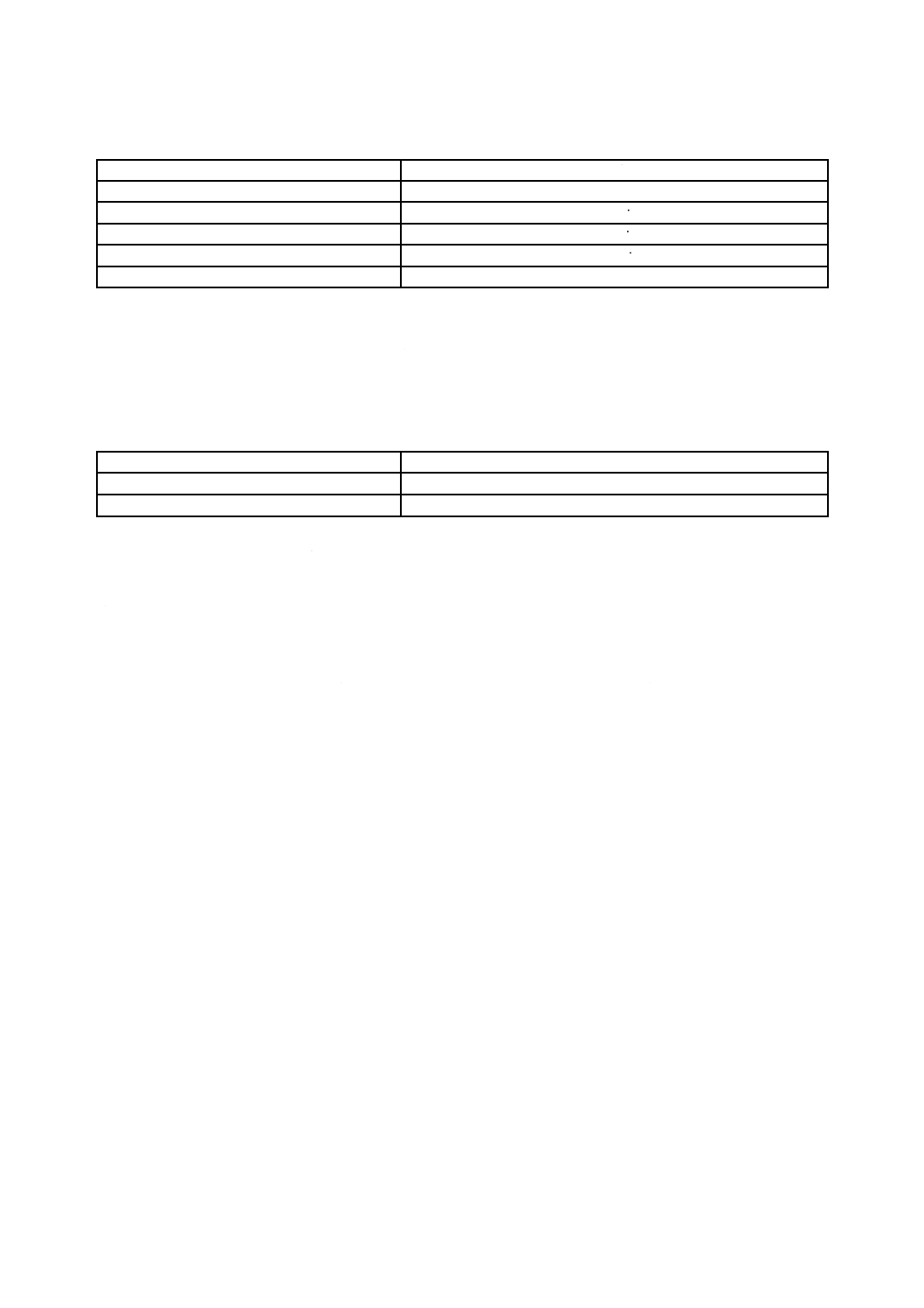

表17−VCC端子電圧及びタイミング

特性

動作クラス

範囲

精度

分解能

UCC

クラスA,B,C

−1 V〜6 V

±20 mV

10 ns

8

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.7.2.3

SPU(C6)端子電圧及びタイミングの測定

表18−SPU端子電圧及びタイミング

特性

動作クラス

範囲

精度

分解能

UCC

クラスA,B,C

−1 V〜6 V

±20 mV

10 ns

4.7.2.4

RST端子電流の生成

表19−RST端子電流

パラメタ

モード

範囲

精度

レベルに達した後の

安定化時間

IIH

活性化状態

−30 μA〜200 μA

±10 μA

< 100 ns

IIL

活性化状態

−250 μA〜30 μA

±10 μA

< 100 ns

I a)

非活性化状態

−1.2 mA〜0 mA

±10 μA

< 100 ns

注a) 出力電圧は,−0.5 V〜5.5 Vに制限する。

4.7.2.5

RST端子電圧及びタイミングの測定

表20−RST端子電圧及びタイミング

特性

動作クラス

範囲

精度

分解能

UIH,UIL

クラスA,B,C

−1 V〜6 V

±20 mV

20 ns

tR,tF

0 μs〜2 μs

±20 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上がり及び立下がり)時間

を示す。

4.7.2.6

I/O端子電流の生成

表21−I/O端子電流

パラメタ

モード

範囲

精度

レベルに達した後の

安定化時間

IIH,IOH

試験装置:受信モード

IFD:送信モード

又は

試験装置:送信モード

IFD:受信モード

−400 μA〜50 μA

±5 μA

< 100 ns

IIL

試験装置:受信モード

IFD:送信モード

又は

試験装置:受信モード

IFD:受信モード

0 mA〜1.5 mA

±10 μA

< 100 ns

IOL

IFDが受信モード

0 μA〜1 200 μA

±10 μA

< 100 ns

I a)

非活性化状態

−1.2 mA〜0 mA

±10 μA

< 100 ns

注a) 出力電圧は,−0.5 V〜5.5 Vに制限する。

9

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

4.7.2.7

I/O端子電圧及びタイミングの測定

表22−I/O端子電圧及びタイミング

特性

動作クラス

範囲

精度

分解能

UIH,UIL

クラスA,B,C

−1 V〜6 V

±20 mV

20 ns

tR,tF

0 μs〜2 μs

±20 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上がり及び立下がり)時間

を示す。

4.7.2.8

IFDの送信モードにおけるI/O端子電圧及びタイミングの生成

表23−I/O端子電圧及びタイミング(送信モード)

パラメタ

モード

動作クラス

範囲

精度

UIH,UIL

IFD:受信モード

試験装置:送信モード

クラスA,B

−1 V〜6 V

±20 mV

UIH

IFD:受信モード

試験装置:送信モード

クラスC

−1 V〜2 V

±20 mV

UIL

IFD:受信モード

試験装置:送信モード

クラスC

−1 V〜1 V

±20 mV

tR,tF

IFD:受信モード

試験装置:送信モード

0 μs〜2 μs

±100 ns

注記 tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の間の遷移(立上がり及び立下がり)時間

を示す。

4.7.2.9

IFDの送信モードにおけるI/O端子電流の測定

表24−I/O端子電流(送信モード)

パラメタ

モード

範囲

精度

分解能

IOL

送信モード

0 μA〜1 200 μA

±10 μA

20 ns

I a)

非活性化状態

0 mA〜1.2 mA

±10 μA

20 ns

注a) 出力電圧は,−0.5 V〜5.5 Vに制限する。

4.7.2.10 CLK端子電流の生成

表25−CLK端子電流

パラメタ

モード

範囲

精度

レベルに達した後の

安定化時間

IIH

活性化状態

−30 μA〜150 μA

±10 μA

< 20 ns

IIL

活性化状態

−150 μA〜30 μA

±10 μA

< 20 ns

I a)

非活性化状態

−1.2 mA〜0 mA

±10 μA

< 100 ns

注a) 出力電圧は,−0.5 V〜5.5 Vに制限する。

4.7.2.11 CLK端子電圧及びタイミングの測定

10

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表26−CLK端子電圧及びタイミング

特性

動作クラス

範囲

精度

分解能

UIH,UIL

クラスA,B,C

−1 V〜6 V

±20 mV

20 ns

4.7.2.12 CLK端子の波形の測定(一周期の測定)

表27−CLK端子の波形

特性

範囲

精度

デューティサイクルa)

周期の35 %〜65 %

周期の±2.5 %

周波数b)

0.5 MHz〜20.5 MHz

周期の±2.5 %

tR,tF c)

周期の1 %〜10 %

周期の±2.5 %

IFD試験装置は,測定の間,全てのサイクルを確認できなければならない。

注a) デューティサイクルは,隣接する二つの立上がりエッジ間で測定する。各立上がりエッジの測定点は,VH min

(100 %)とVL max(0 %)との50 %とする。

b) 周波数は,隣接する二つの立上がりエッジ間で測定する。各立上がりエッジの測定点はVH min(100 %)と

VL max(0 %)との50 %とする。

c) tR及びtFは,VH minとVL maxとで決まる信号振幅の10 %〜90 %の遷移(立上がり及び立下がり)時間を示

す。

4.7.2.13 GNDとI/O端子との間の静電容量の測定

表28−外部端子間の静電容量

特性

範囲

精度

C

0 pF〜50 pF

±5 pF

4.7.2.14 I/Oプロトコルのエミュレート

IFD試験装置は,試験シナリオを実行する場合に必要とされるプロトコルT=0,T=1及びICカードのア

プリケーションをエミュレートできなければならない。

注記 特定の機能がICカードに実装されていない場合には,IFD試験装置に,対応する試験能力を備

えていることを要求しない(例えば,ICカードで実装されないT=0プロトコル)。

4.7.2.15 送信モードにおけるI/Oキャラクタの生成タイミング

IFD試験装置は,JIS X 6320-3に従い,I/O端子にクロック周波数に応じたビット列を生成できなければ

ならない。

全てのビットの長さ,保護時間,誤り信号などの全てのタイミングパラメタが設定できなければならな

い。

表29−タイミングパラメタの精度

記号

意味

精度

εt

全てのタイミングパラメタ

±4クロック周期

4.7.2.16 I/Oプロトコルの測定及び監視

IFD試験装置は,CLK周波数に関係してI/O端子の論理的な“低”レベル状態及び“高”レベル状態の

11

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

タイミングを測定し,監視することができなければならない。

表30−タイミング特性

特性

精度

全てのタイミング特性

±2クロック周期

4.7.2.17 プロトコル分析

IFD試験装置は,JIS X 6320-3に適合したT=0プロトコル及びT=1プロトコルに一致するビット列の分

析のため,並びに上位のプロトコル及びアプリケーションの確認のために論理的なデータフローを抽出で

きなければならない。

注記 特定の機能がICカードに実装されていない場合には,IFD試験装置に,対応する試験能力を備

えていることを要求しない(例えば,ICカードで実装されないT=0プロトコル)。

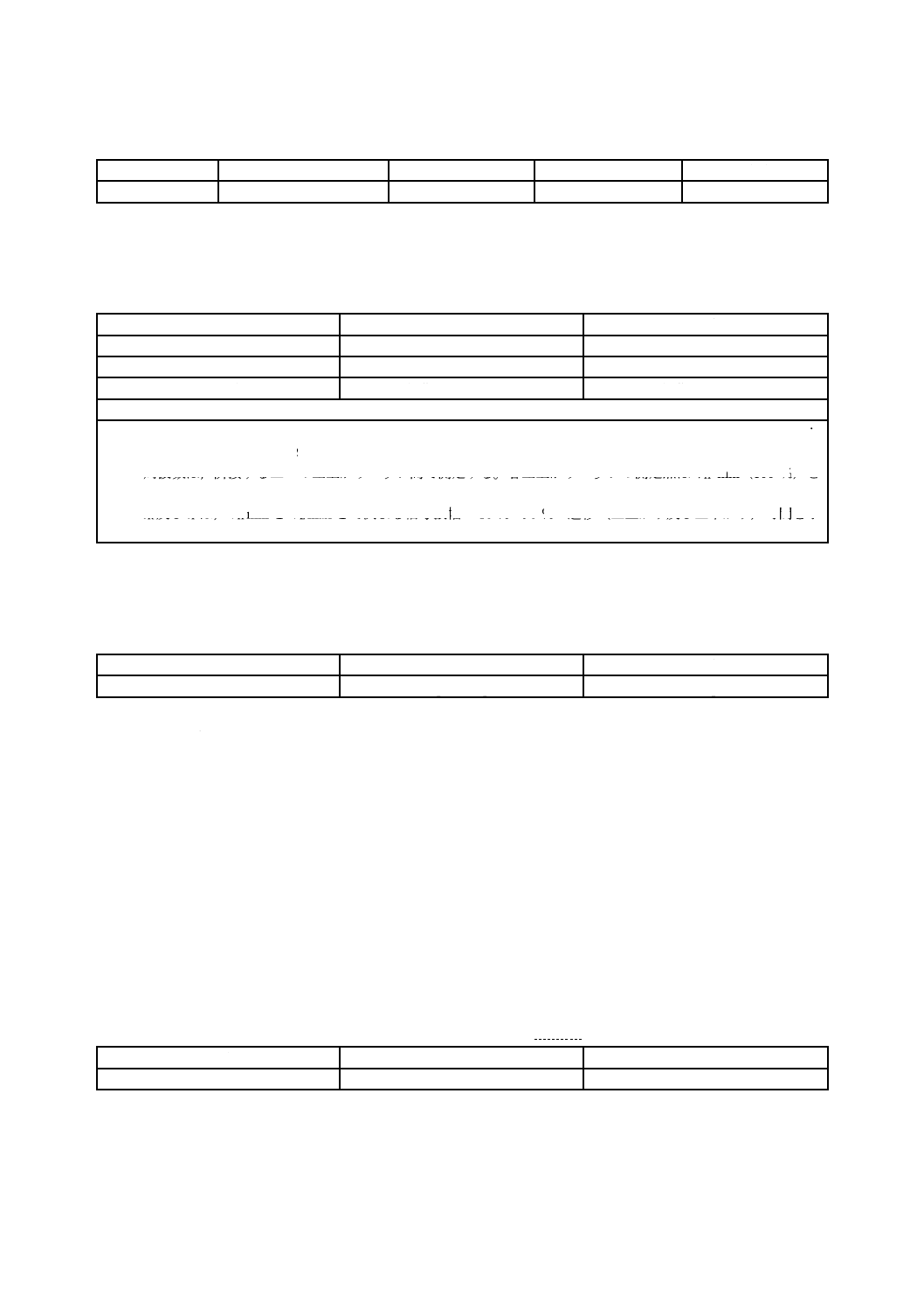

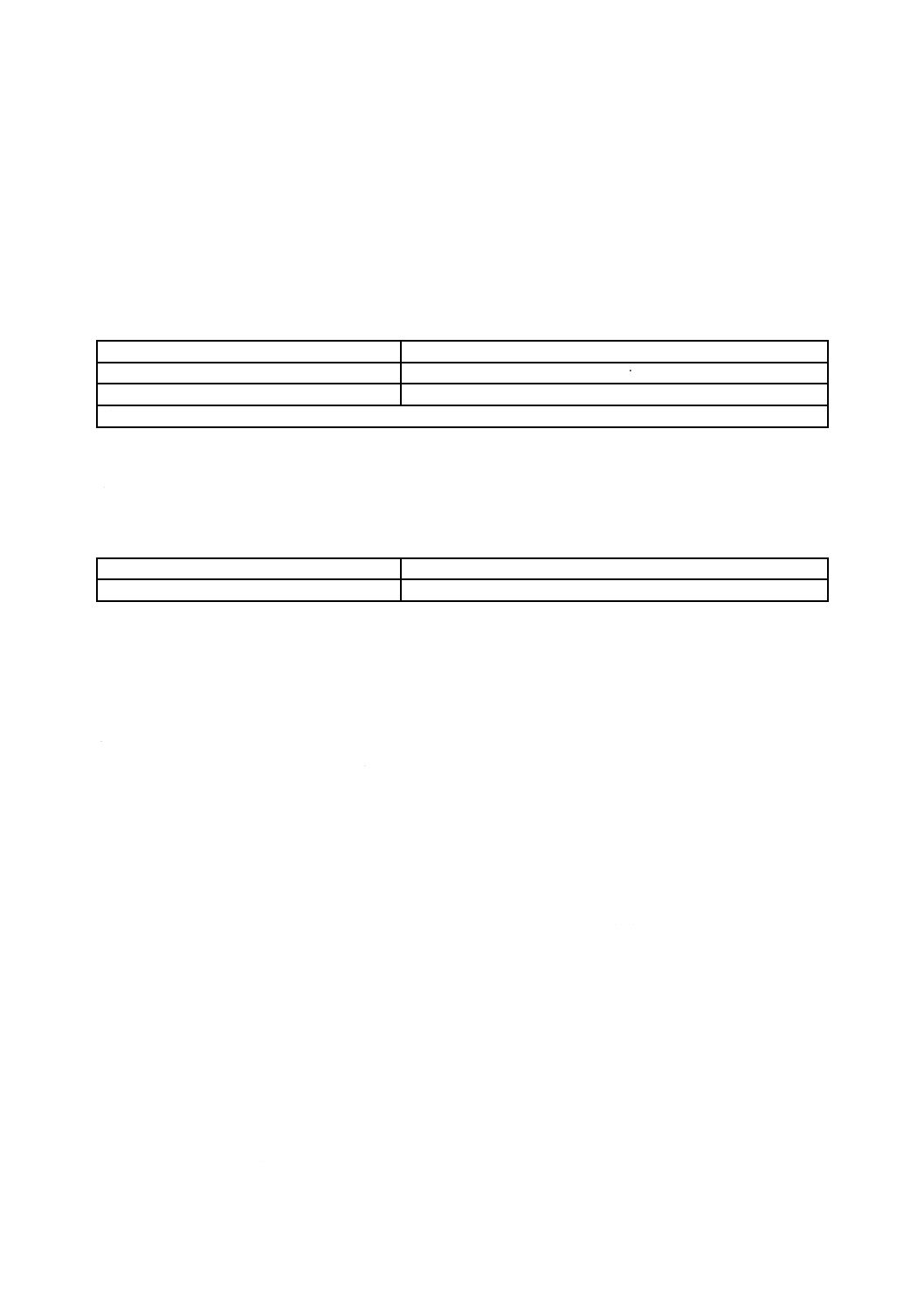

4.7.2.18 各端子のインピーダンス(非活性化状態)

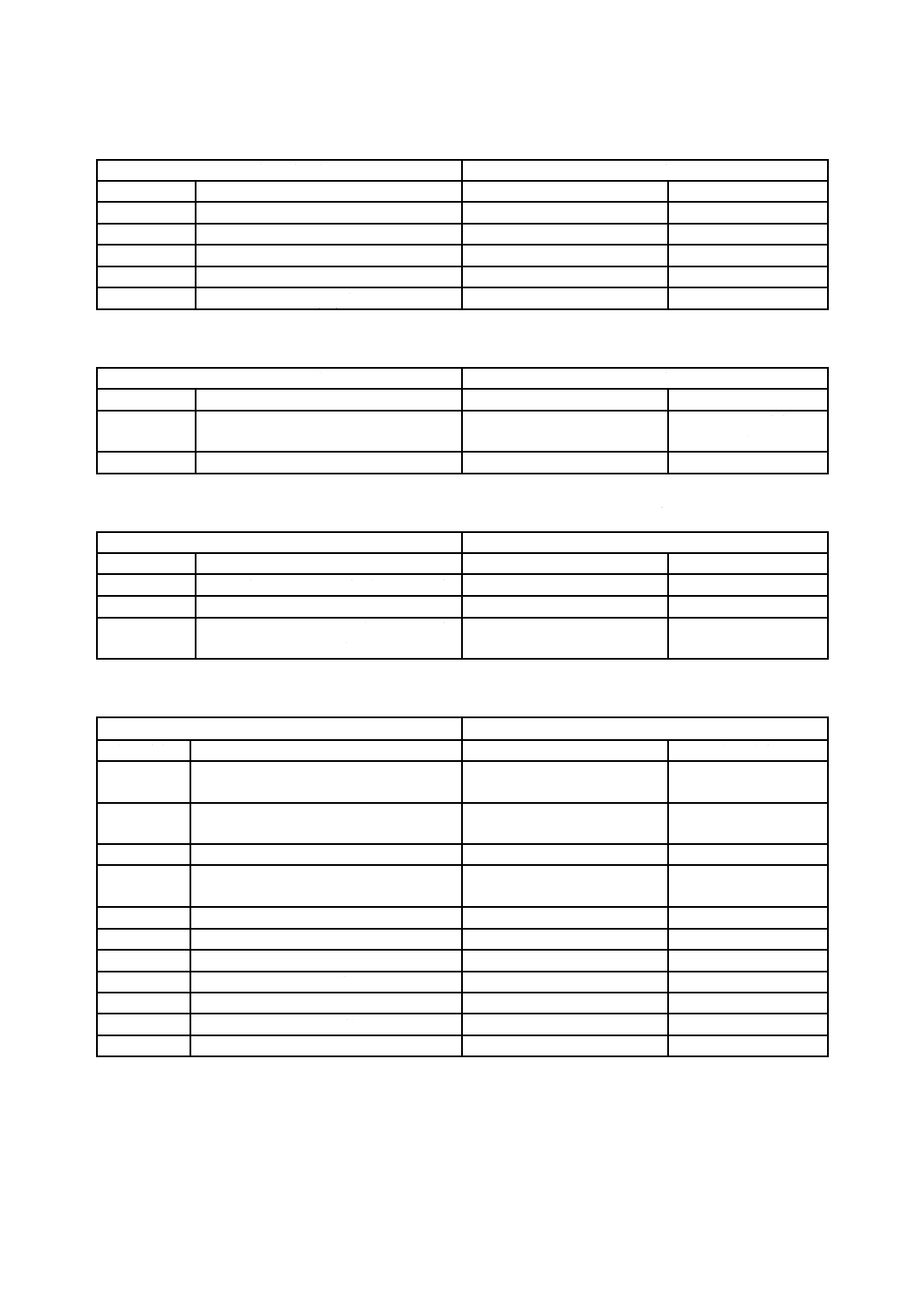

表31−インピーダンス

端子

抵抗

精度

容量

精度

VCC

10 kΩ

±1 kΩ

30 pF

±6 pF

I/O

50 kΩ

±5 kΩ

30 pF

±6 pF

RST

50 kΩ

±5 kΩ

30 pF

±6 pF

CLK

50 kΩ

±5 kΩ

30 pF

±6 pF

4.7.3

試験シナリオ

この規格の箇条5,箇条6,箇条7及び箇条8で定義するDUTの試験は,実行のための試験シナリオを

必要とする。この試験シナリオは,“代表的プロトコル及びアプリケーション固有通信”であり,DUTの

通常使用のために想定されDUTに実装される,プロトコル及びアプリケーション固有の機能に依存する。

これらの試験の実施者は試験シナリオを定義し,その試験結果を記録する。試験シナリオは,実際に利

用される場合に想定されるDUTの全機能又は代表的なサブセットを取り込まなければならず,もし全機

能を取り込むことが実際的であれば,それが望ましい。試験シナリオは,少なくとも1秒の持続期間がな

ければならない。

注記 試験の実施者が試験シナリオを定義するためには,実装されたプロトコル及び機能についての

情報だけでなく,DUTの想定使用法についての情報も必要とすることがある。

4.8

試験方法と基本規格の要求項目との関係

全ての相対的な電圧定義(例えば,0.7×UCC,0.15×UCC又はUCC+0.3 V)は,GND端子を基準にして

決めなければならない。そして同時に測定したUCCの電圧値に対して検査しなければならない。

12

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

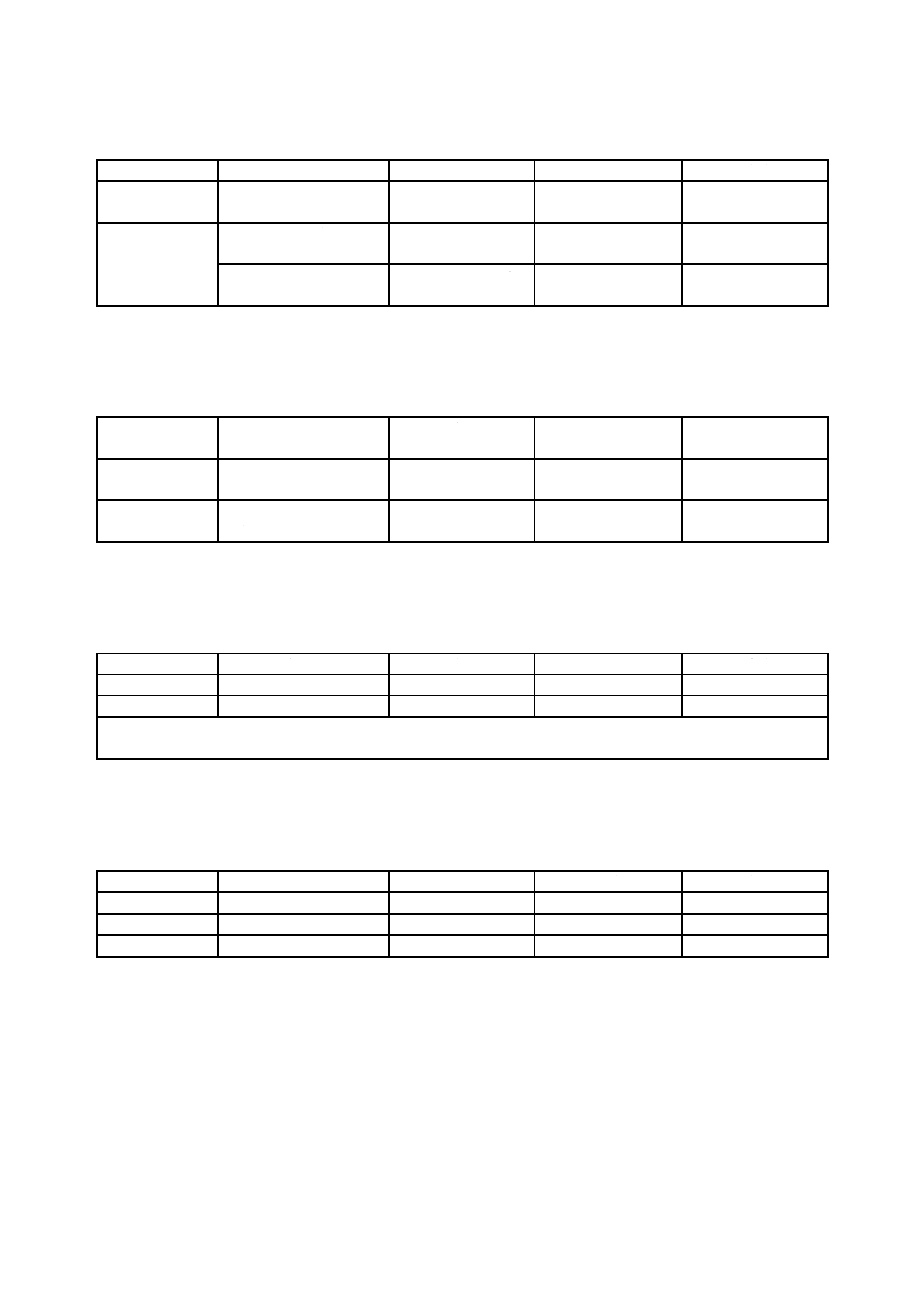

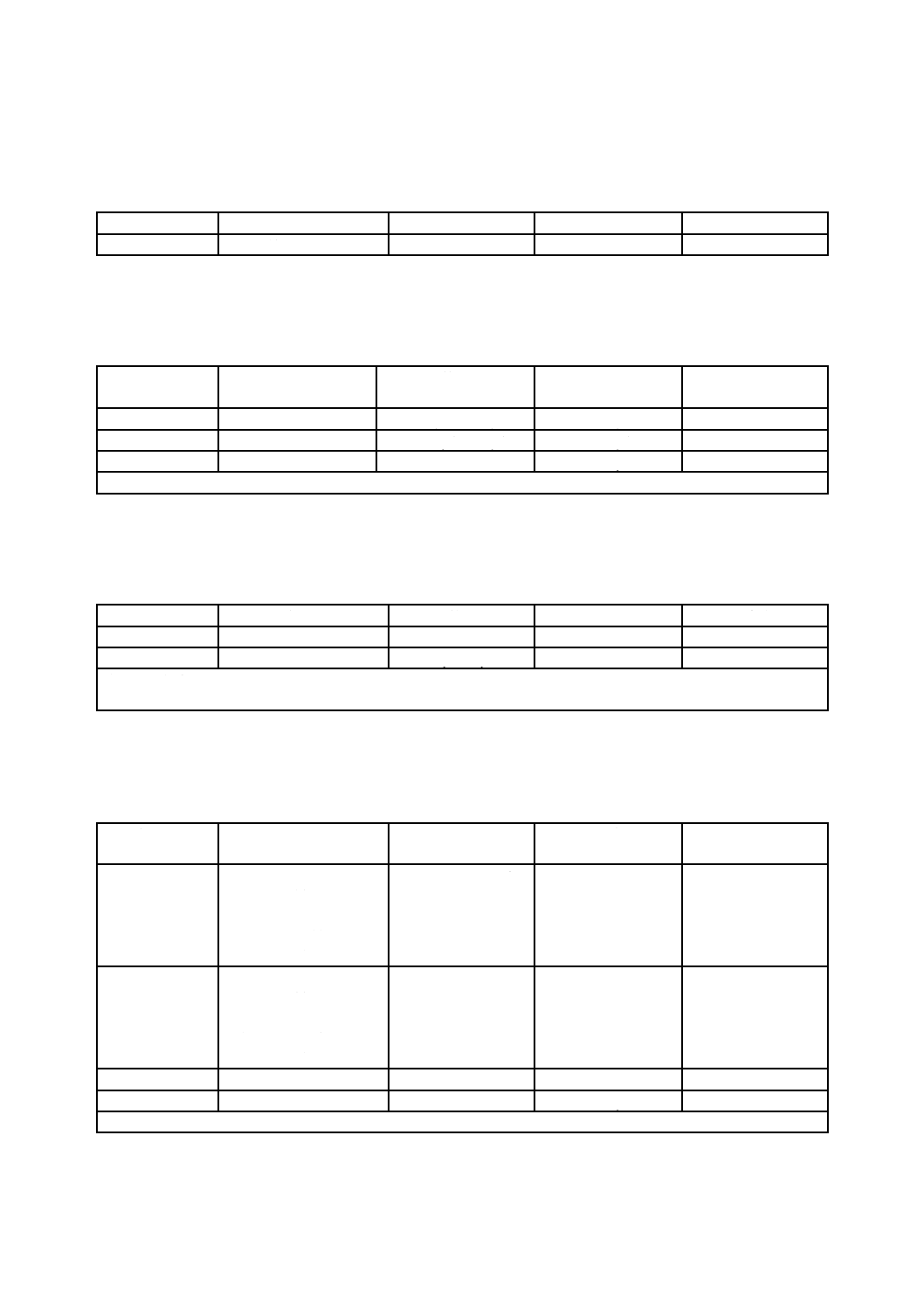

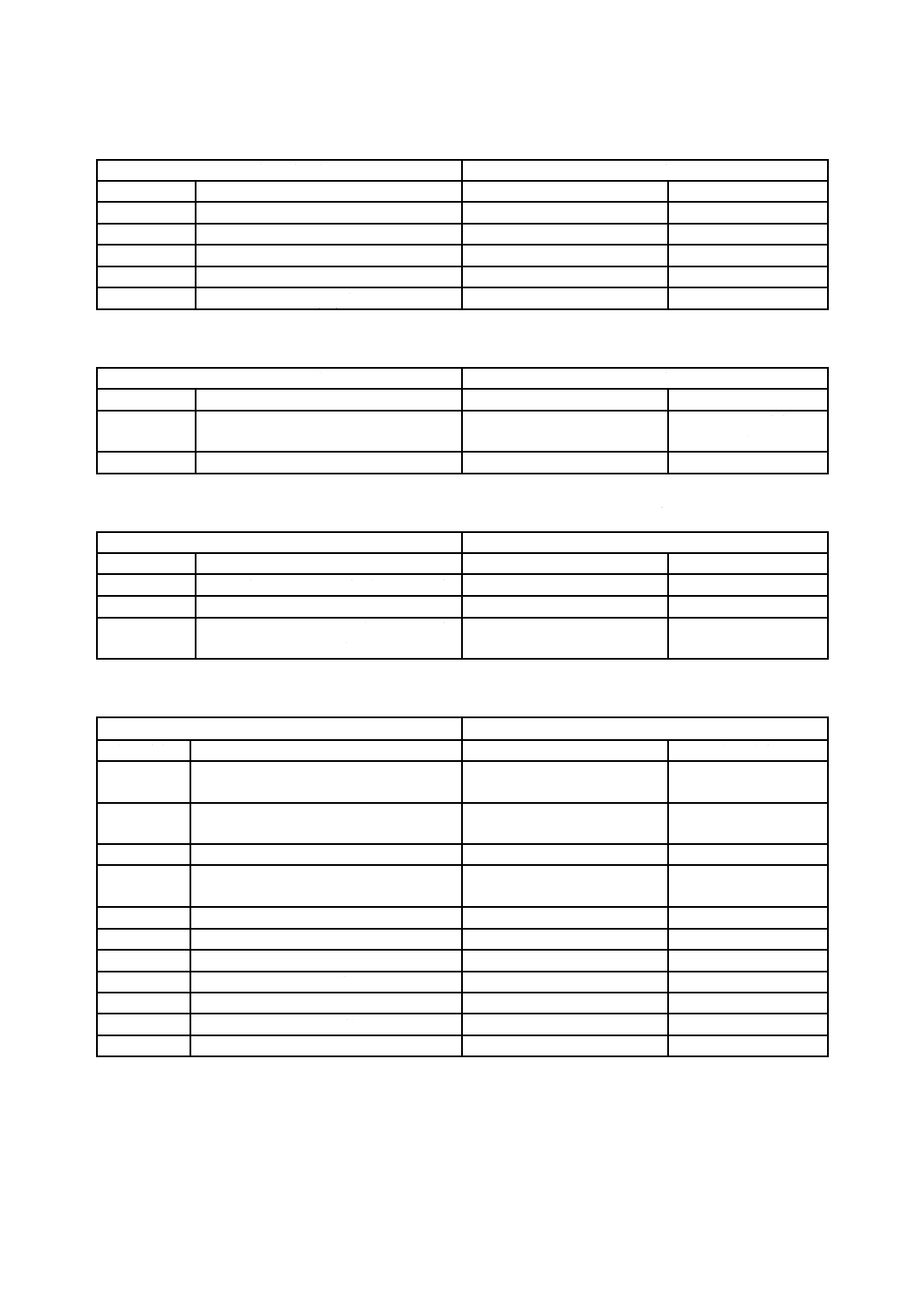

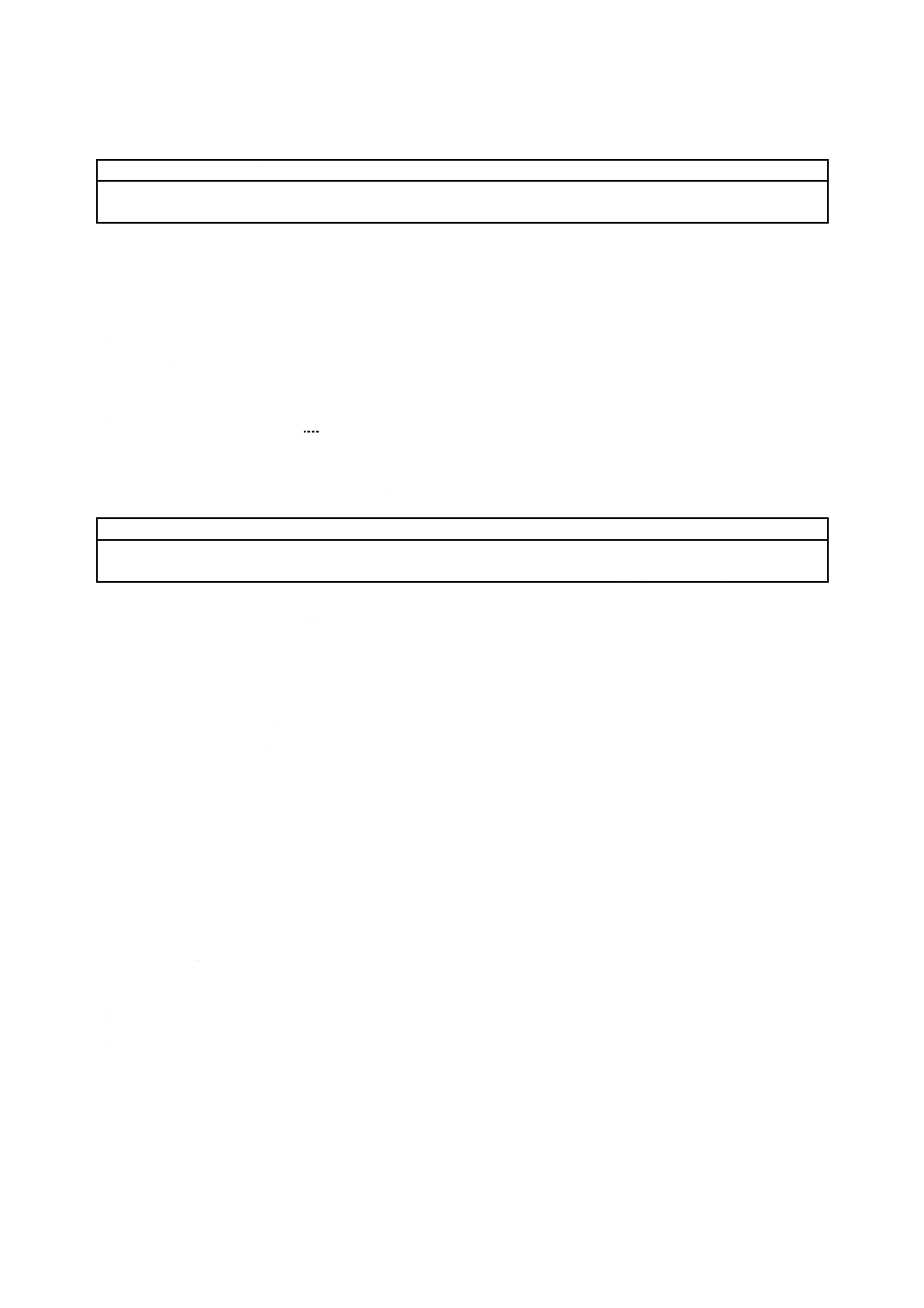

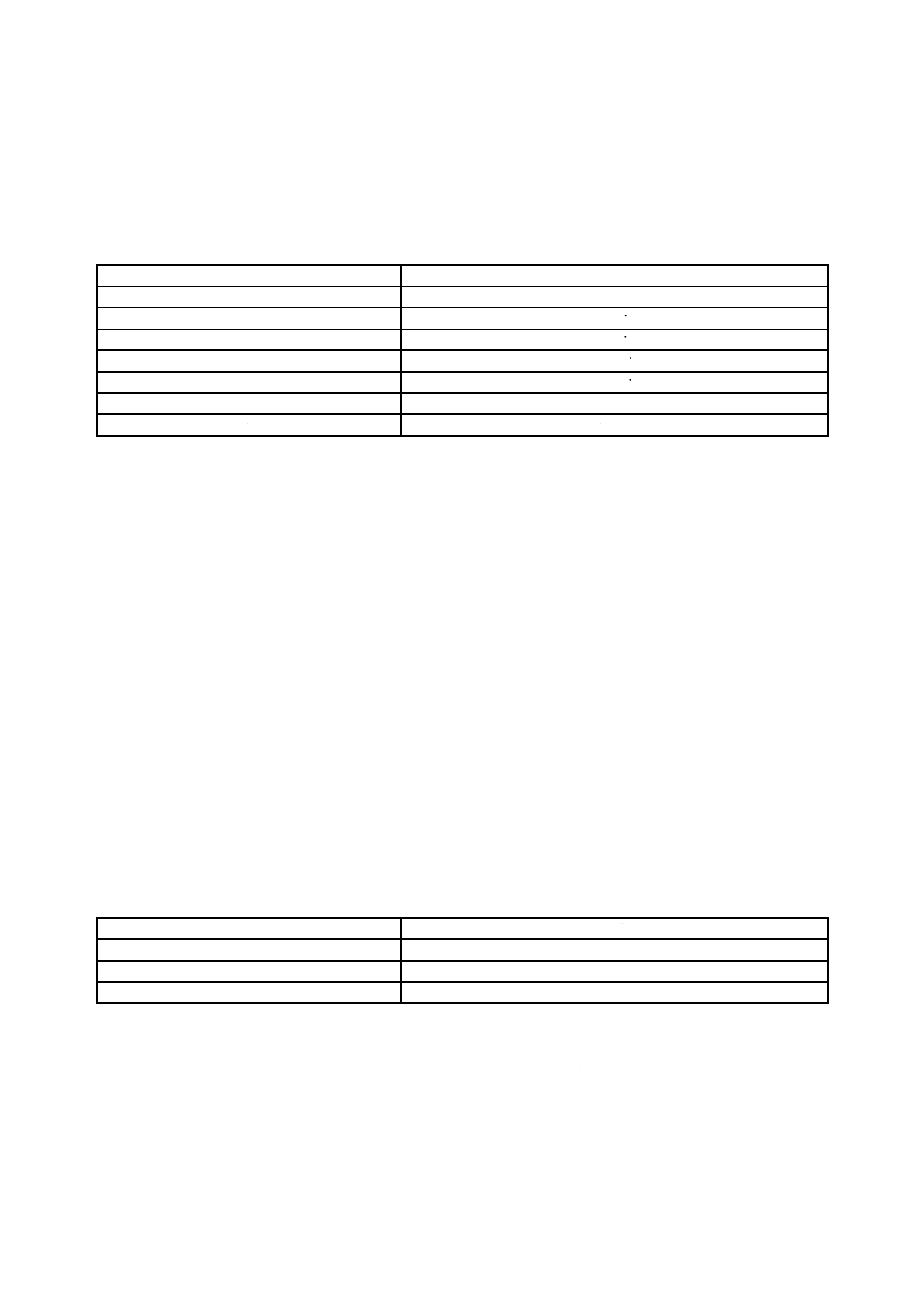

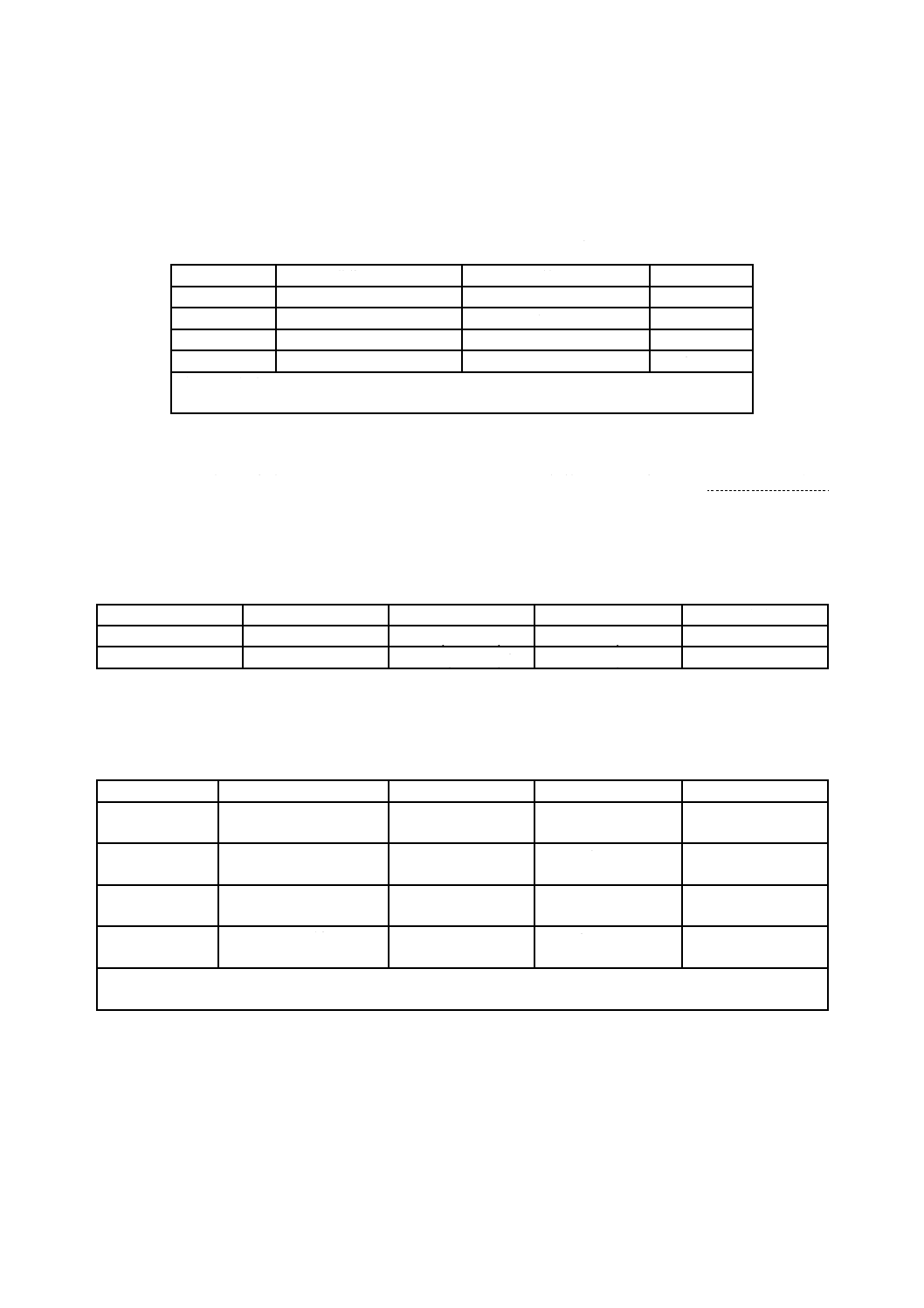

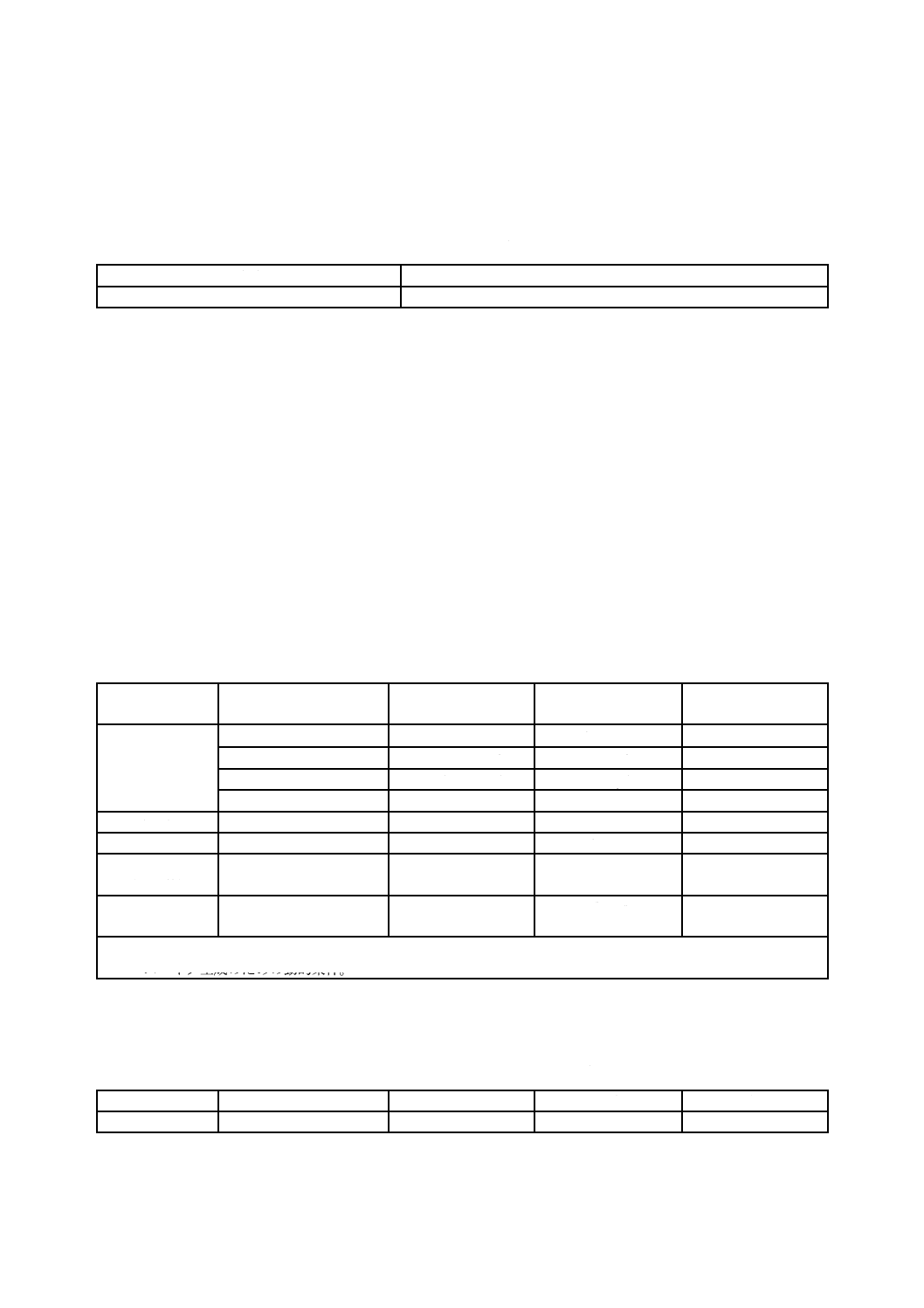

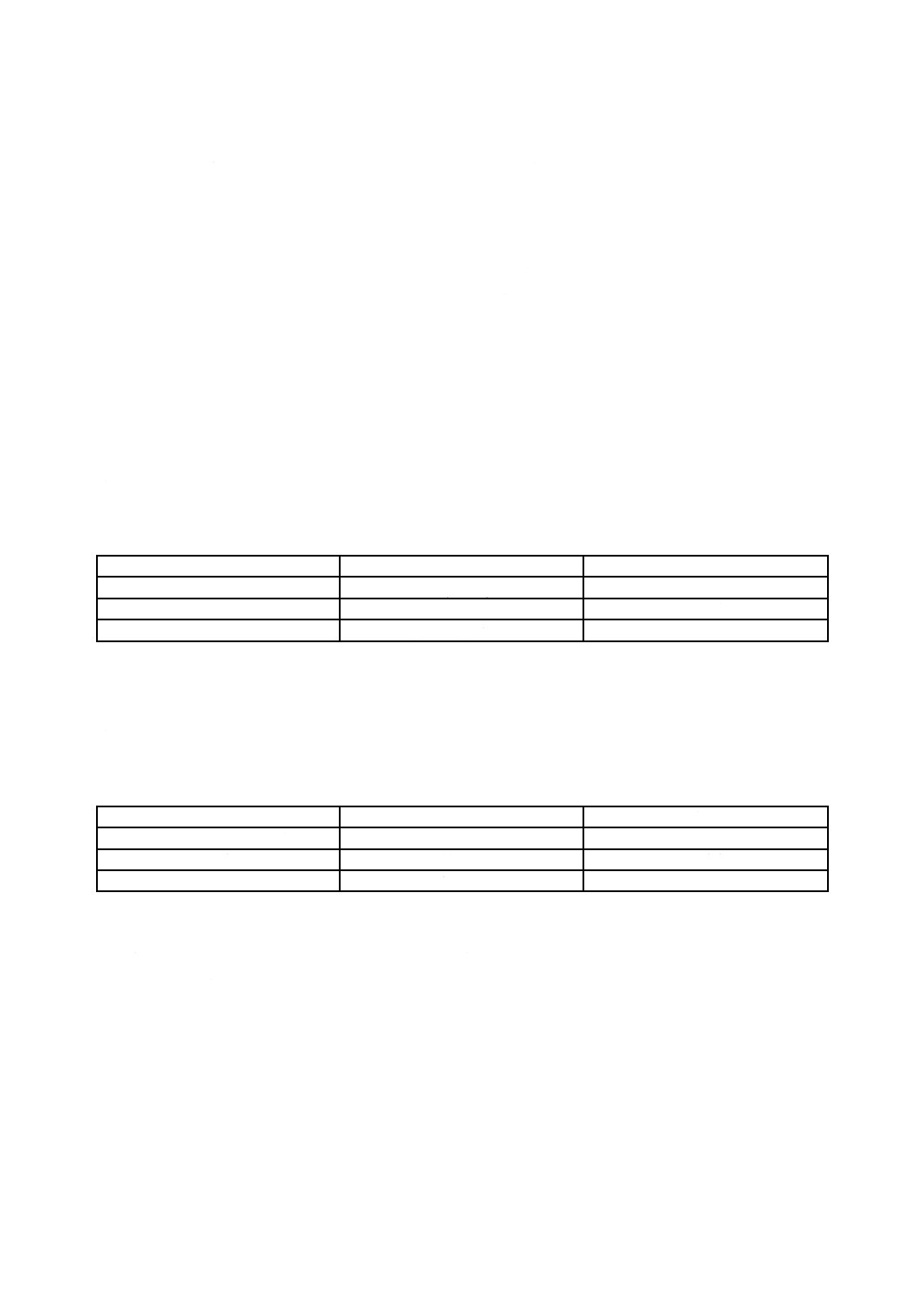

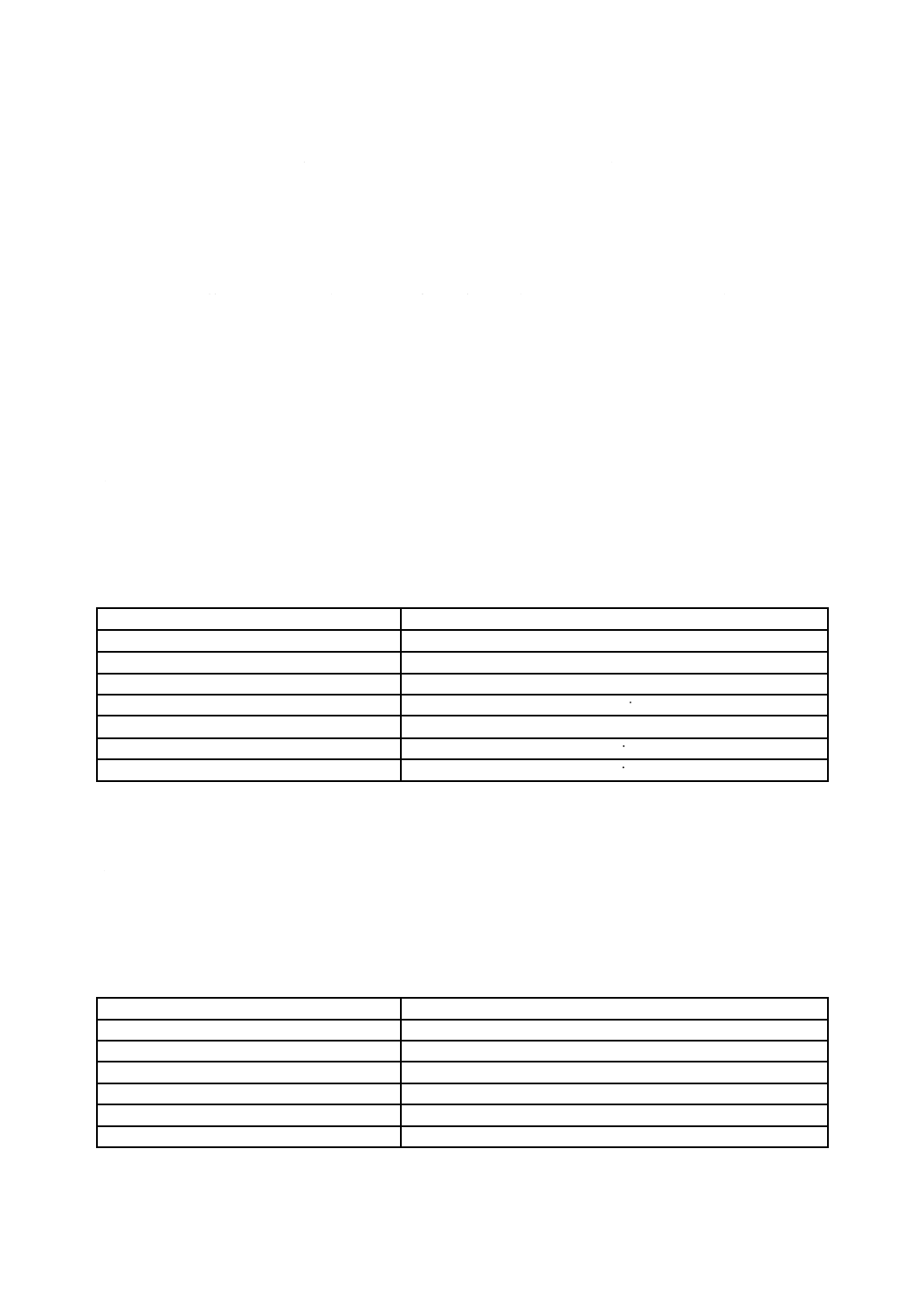

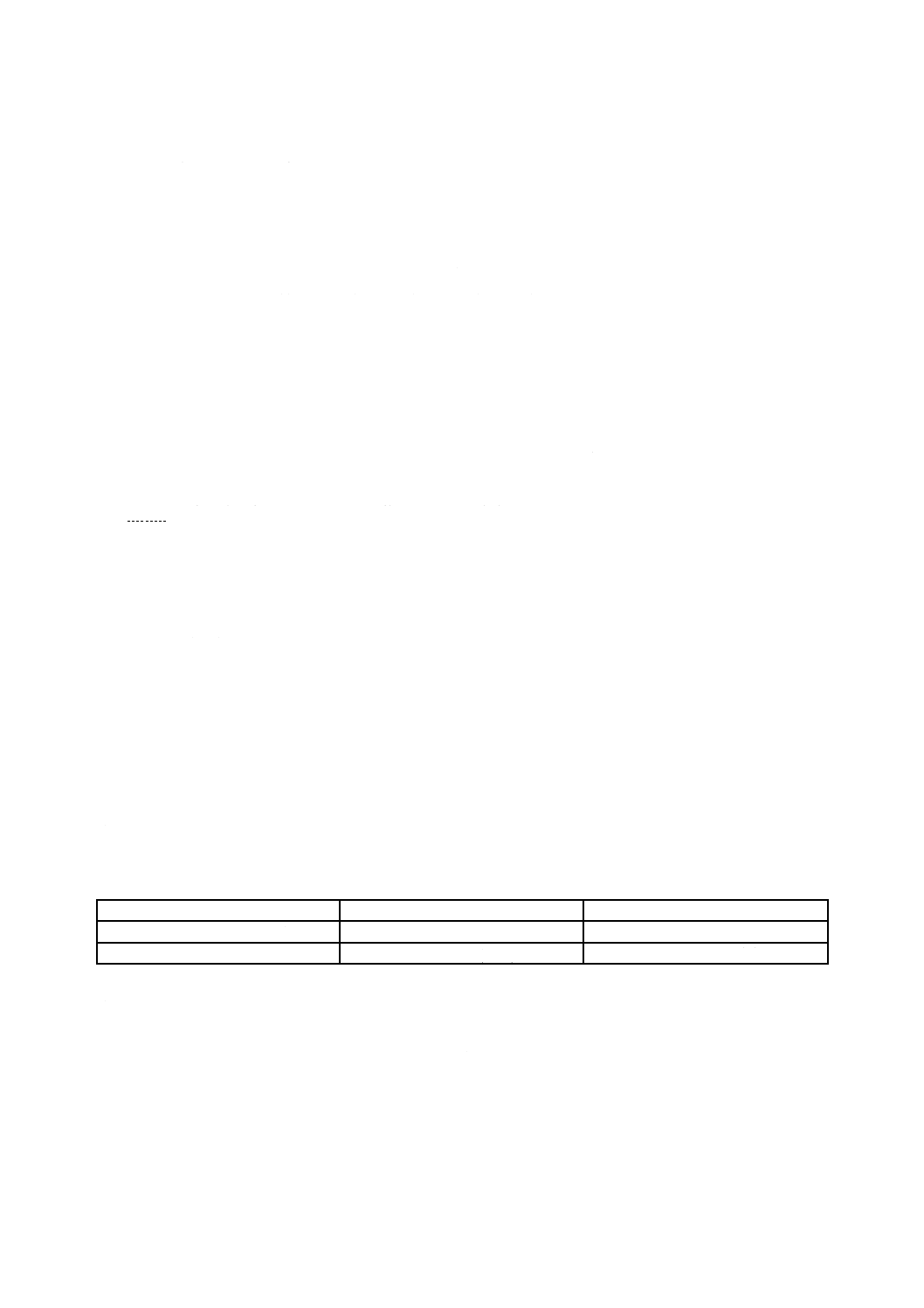

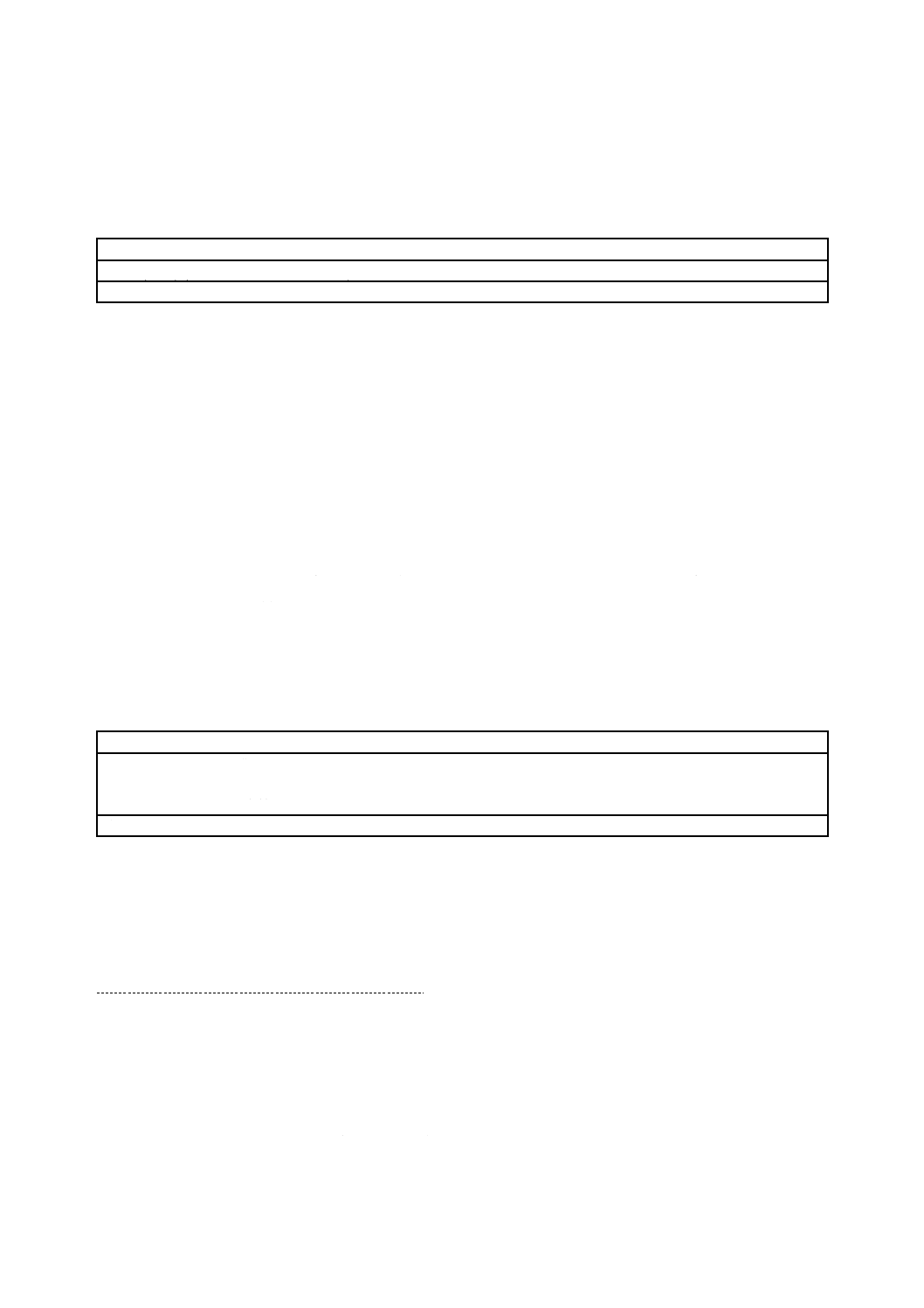

表32−外部端子付きICカードの電気的特性の試験方法

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

5.1

VCC端子

JIS X 6320-3

5.2.1

5.2

I/O端子

JIS X 6320-3

5.2.5

5.3

CLK端子

JIS X 6320-3

5.2.3

5.4

RST端子

JIS X 6320-3

5.2.2

5.5

SPU(C6)端子

JIS X 6320-3

5.2.4

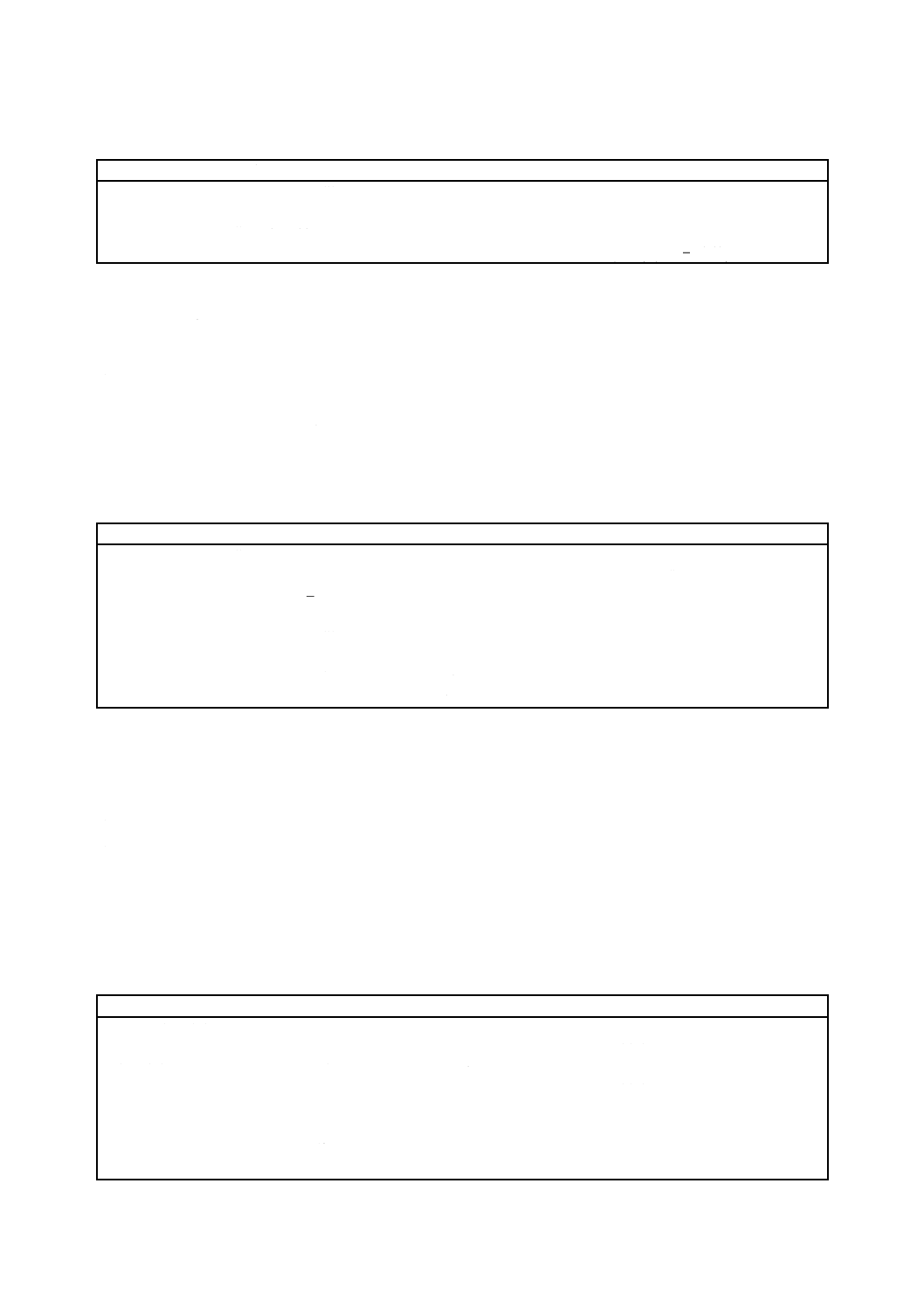

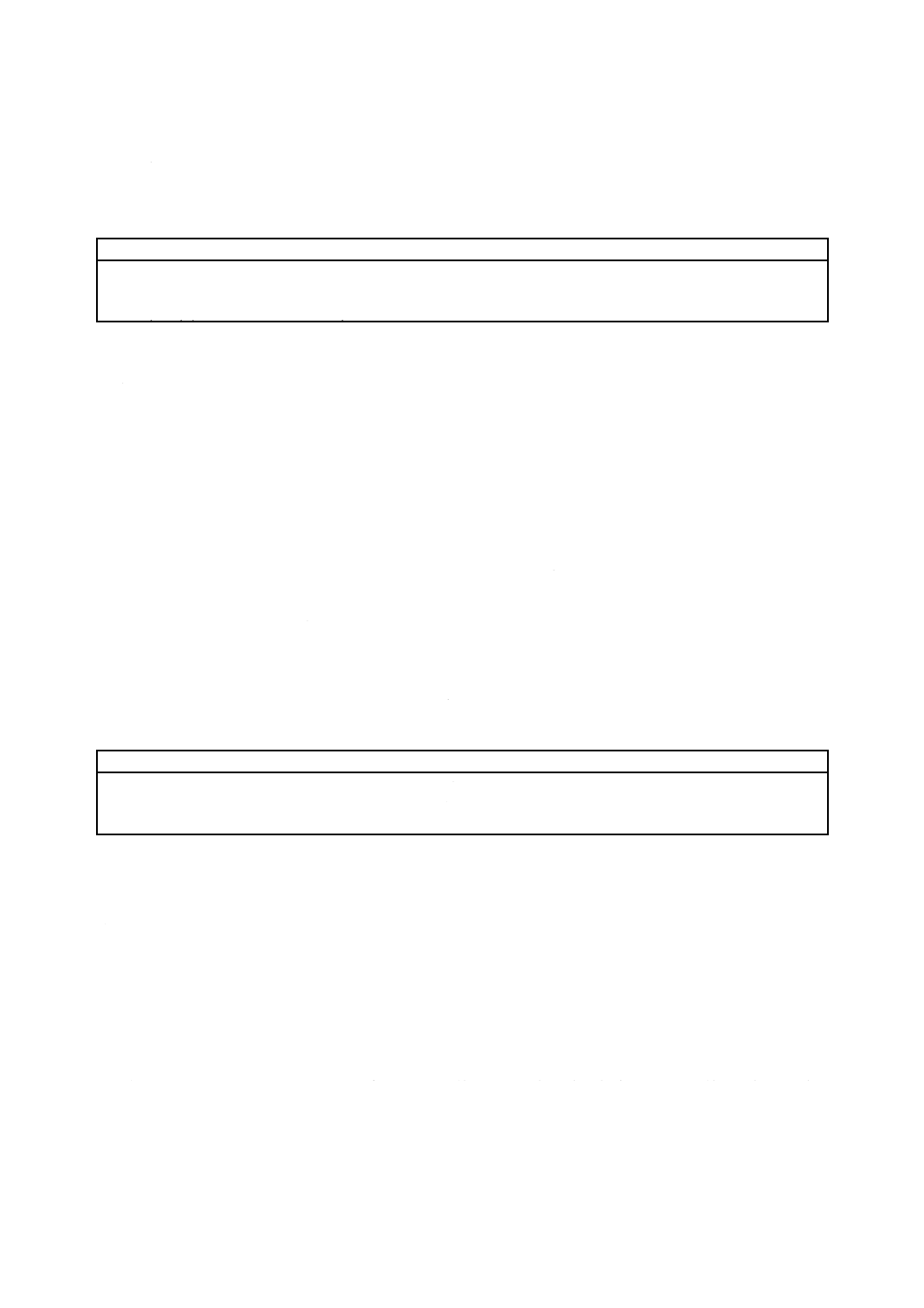

表33−外部端子付きICカードの論理的な操作の試験方法−リセット応答(ATR)

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

6.1.1

コールドリセット及びリセット応答

(ATR)

JIS X 6320-3

6.2.1,6.2.2,箇条7,

箇条8

6.1.2

ウォームリセット

JIS X 6320-3

6.2.3

表34−外部端子付きICカードの論理的な操作の試験方法−T=0プロトコル

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

6.2.1

T=0プロトコルのI/O伝送タイミング

JIS X 6320-3

7.1,7.2,10.2

6.2.2

T=0プロトコルのI/Oキャラクタ再送

JIS X 6320-3

7.3,10.2

6.2.3

T=0プロトコルのI/O受信タイミング

及び誤り信号

JIS X 6320-3

7.1,7.2,7.3,10.2

表35−外部端子付きICカードの論理的な操作の試験方法−T=1プロトコル

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

6.3.1

T=1プロトコルのI/O送信タイミング

JIS X 6320-3

7.1,7.2,8.3,11.2,11.3,

11.4.2,11.4.3

6.3.2

T=1プロトコルのI/O受信タイミング

JIS X 6320-3

7.1,7.2,8.3,11.2,11.3,

11.4.2,11.4.3

6.3.3

キャラクタ待ち時間(CWT)の動作

JIS X 6320-3

11.4.3

6.3.4

キャラクタ待ち時間(CWT)を超えた

ときのIFDへのICカードの動作

JIS X 6320-3

11.4.3

6.3.5

ブロック保護時間(BGT)

JIS X 6320-3

11.4.3

6.3.6

ICカードによるブロックシーケンス

JIS X 6320-3

11.6.3

6.3.7

プロトコル誤りに対するICカードの動作

JIS X 6320-3

11.6.3

6.3.8

ICカードによる送信誤りの回復

JIS X 6320-3

11.6.3

6.3.9

再同期

JIS X 6320-3

11.6.3

6.3.10

IFSD調整

JIS X 6320-3

11.4.2

6.3.11

IFDによる打切り

JIS X 6320-3

11.6.3

13

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

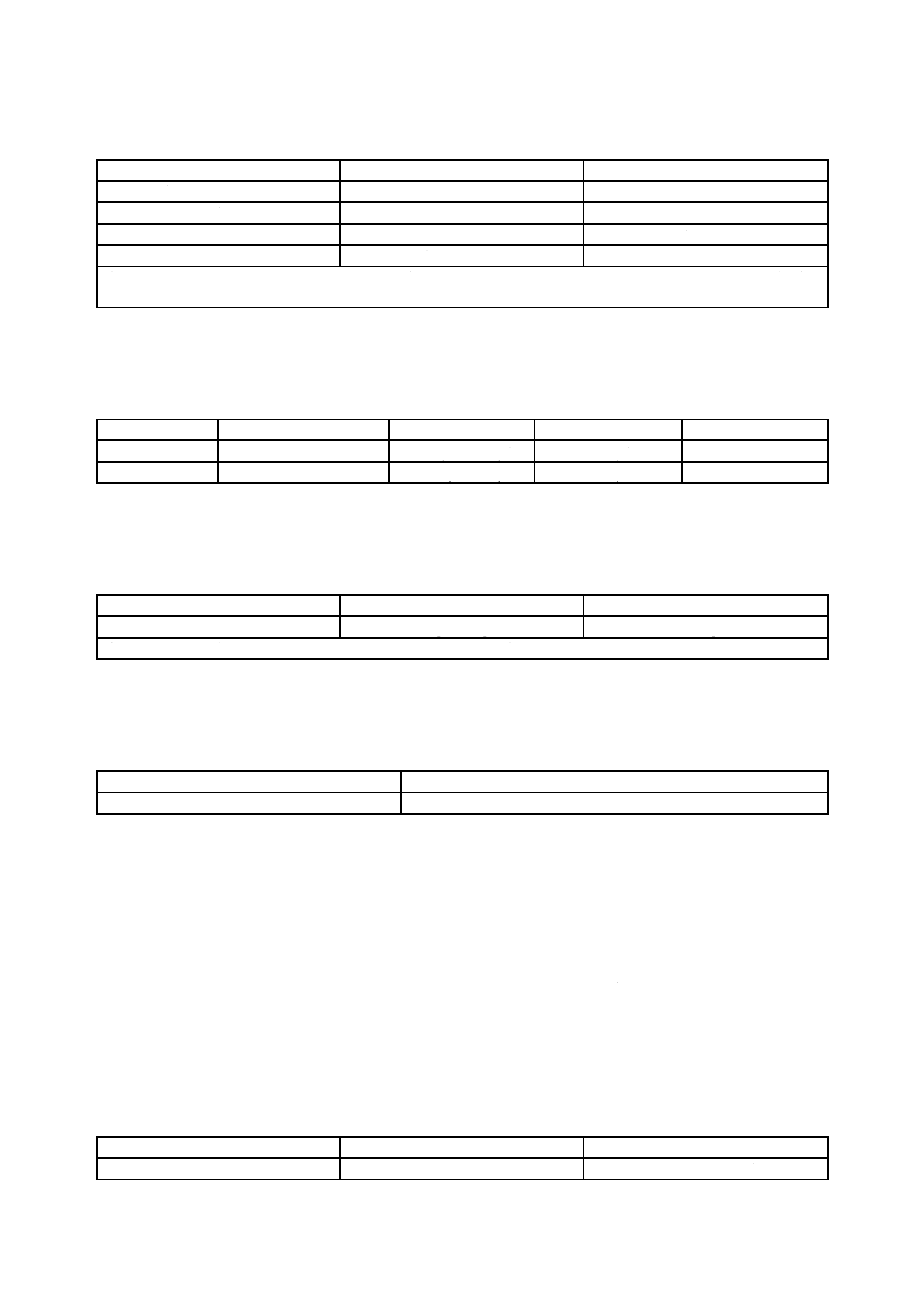

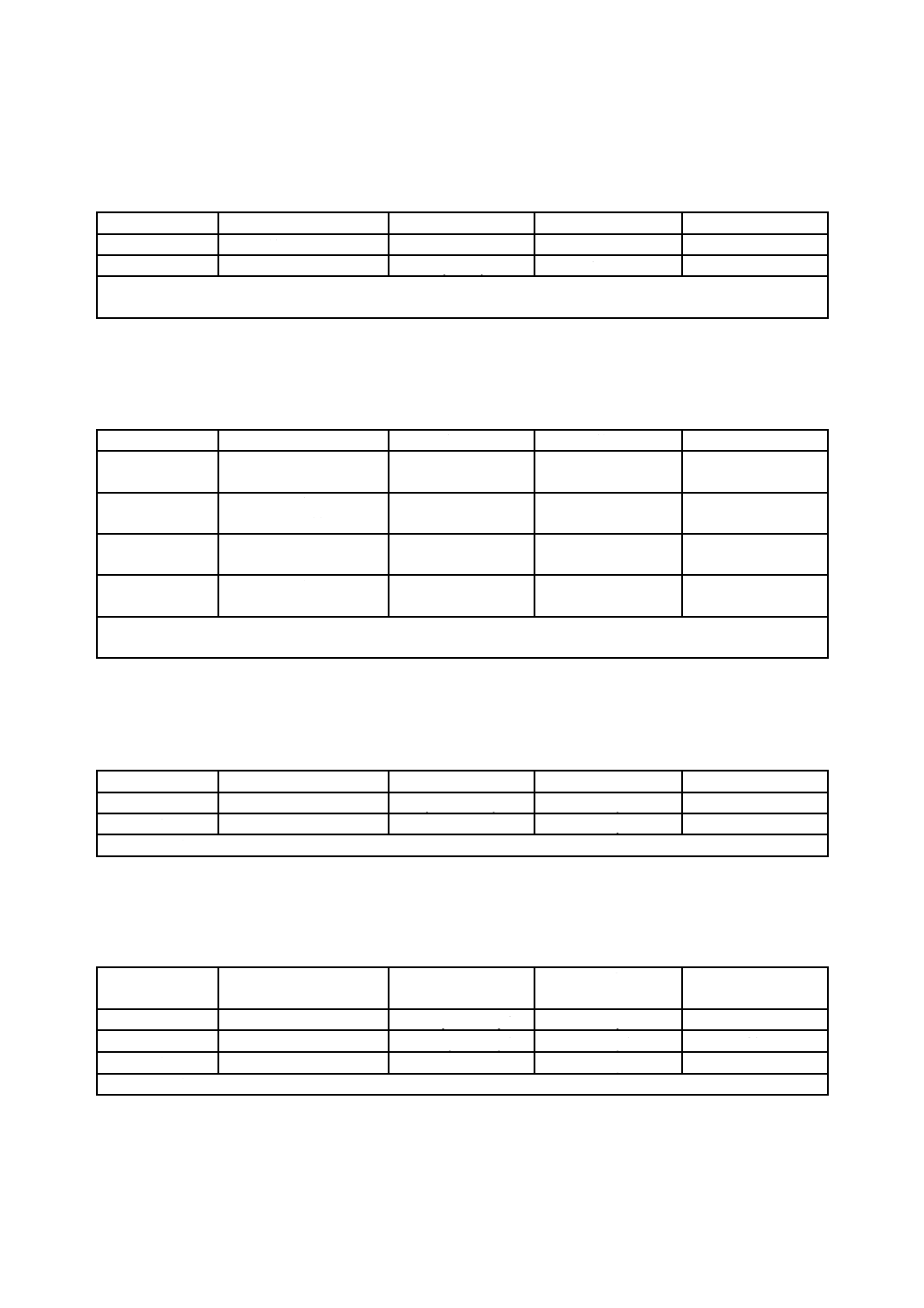

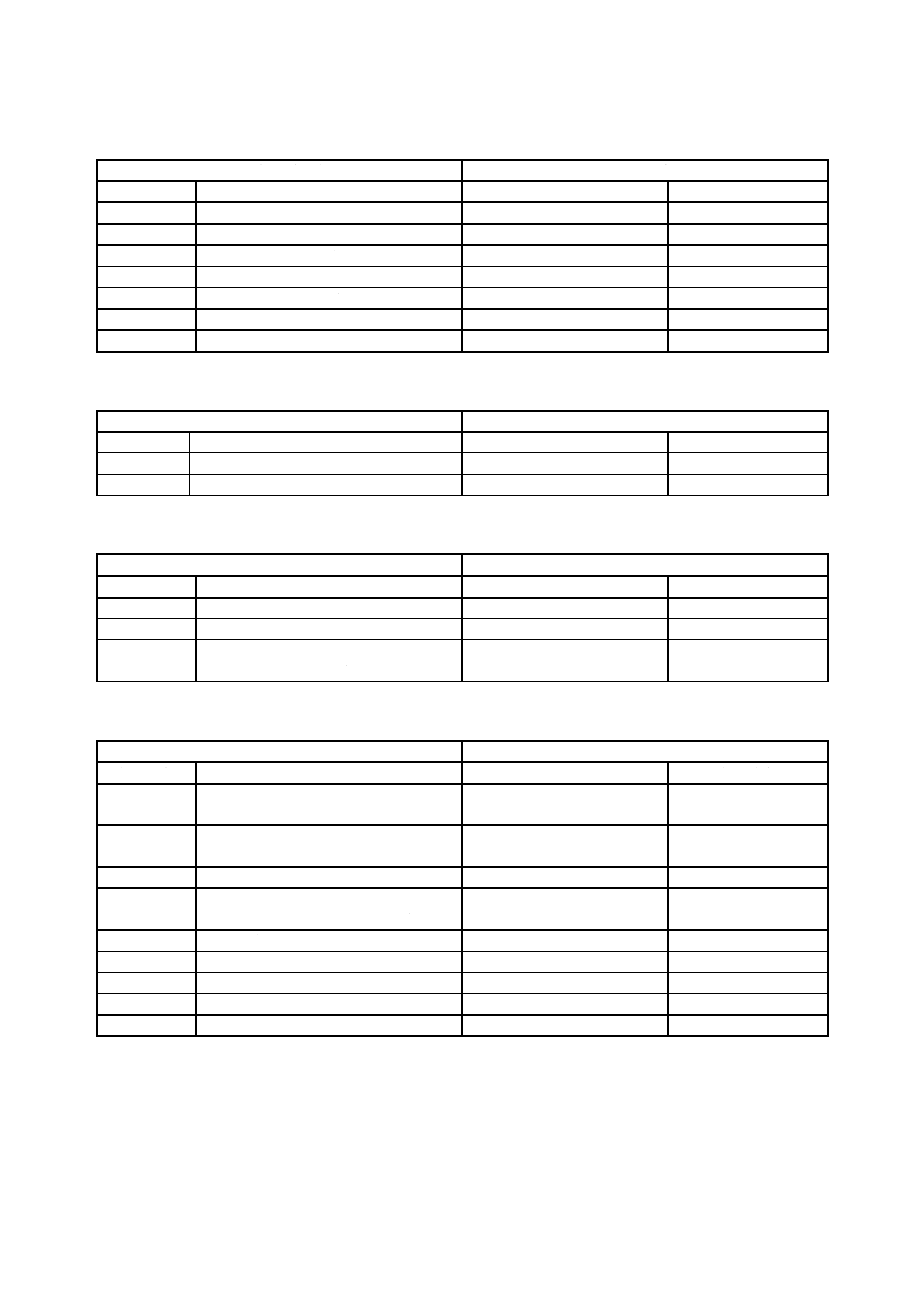

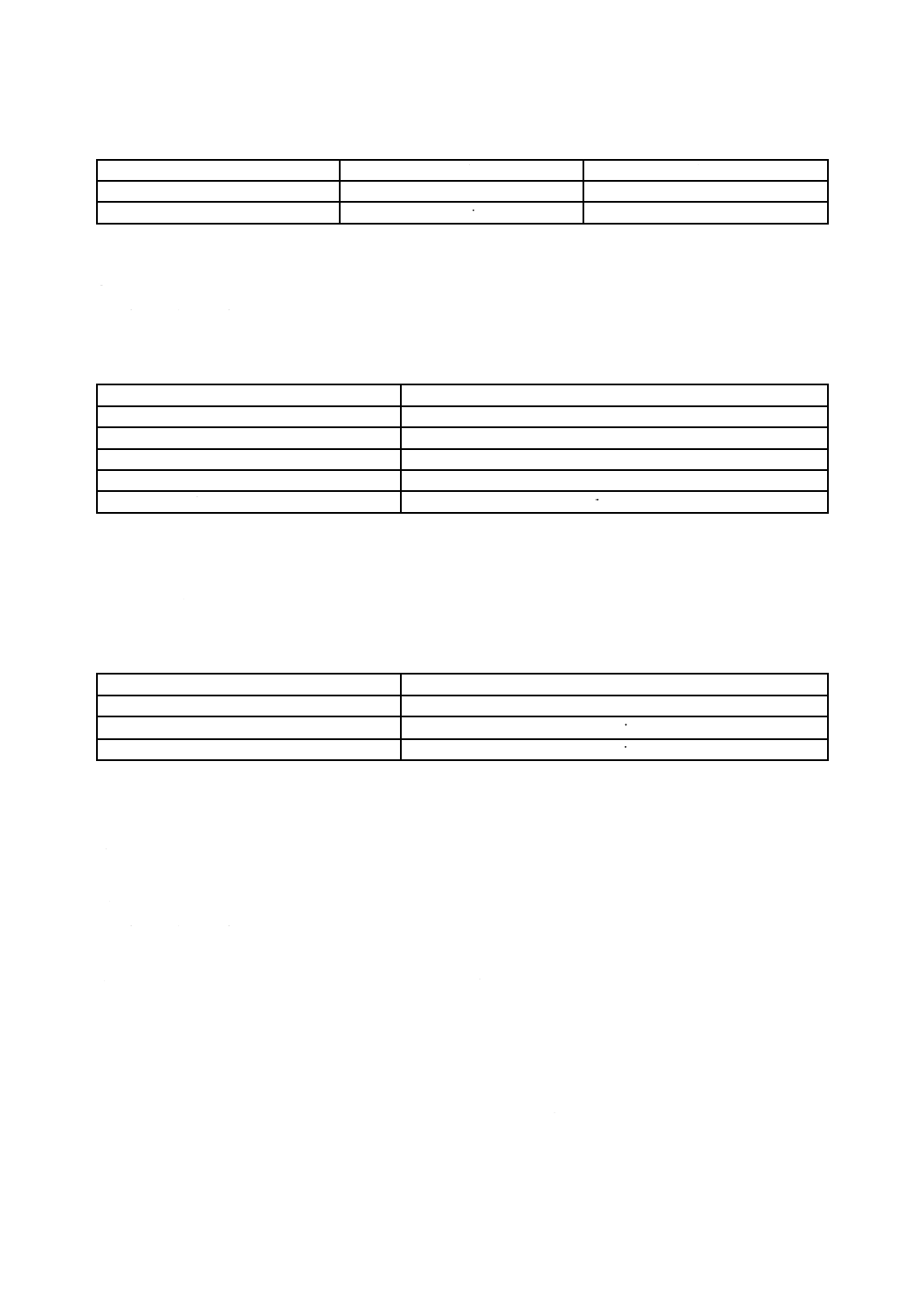

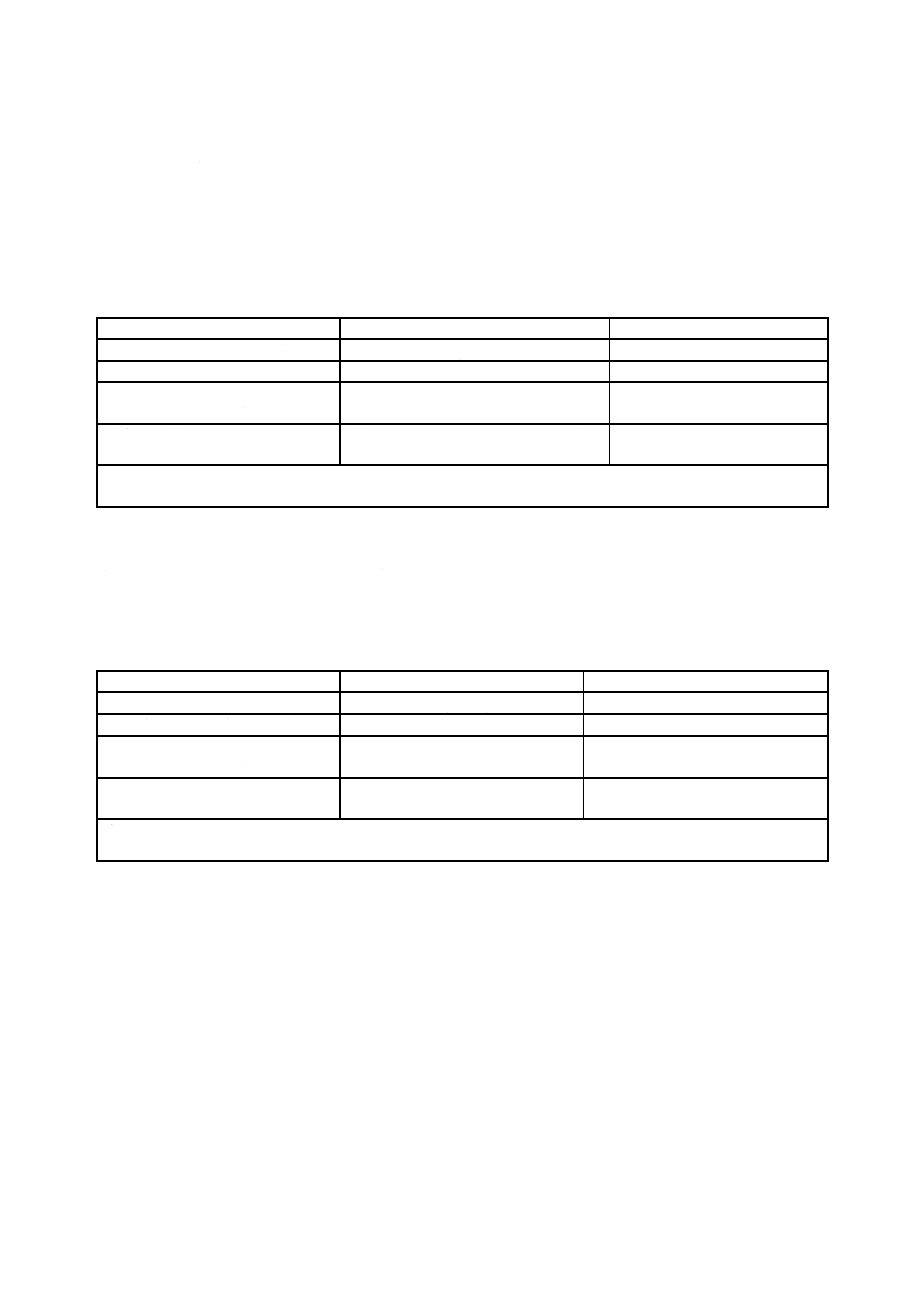

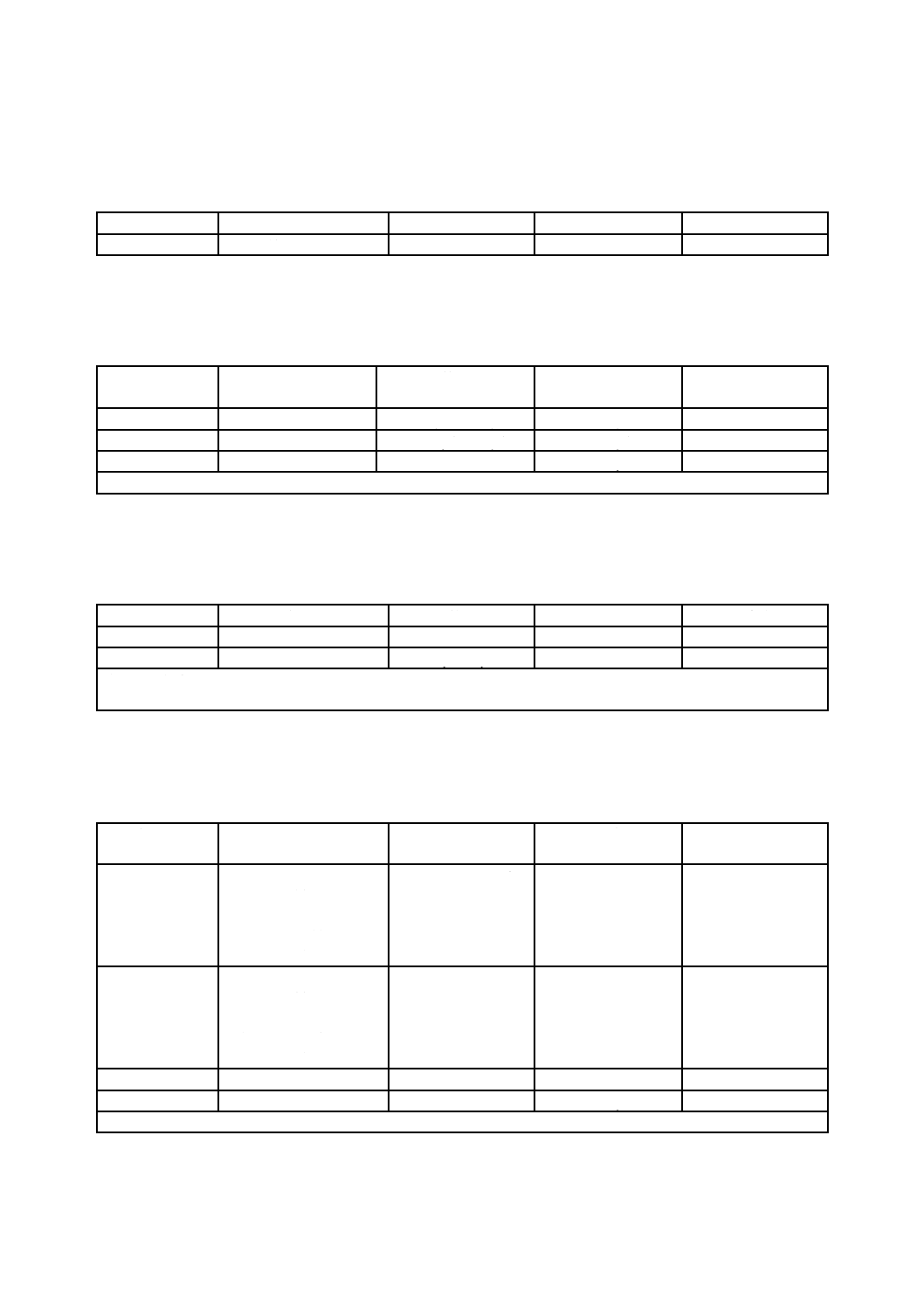

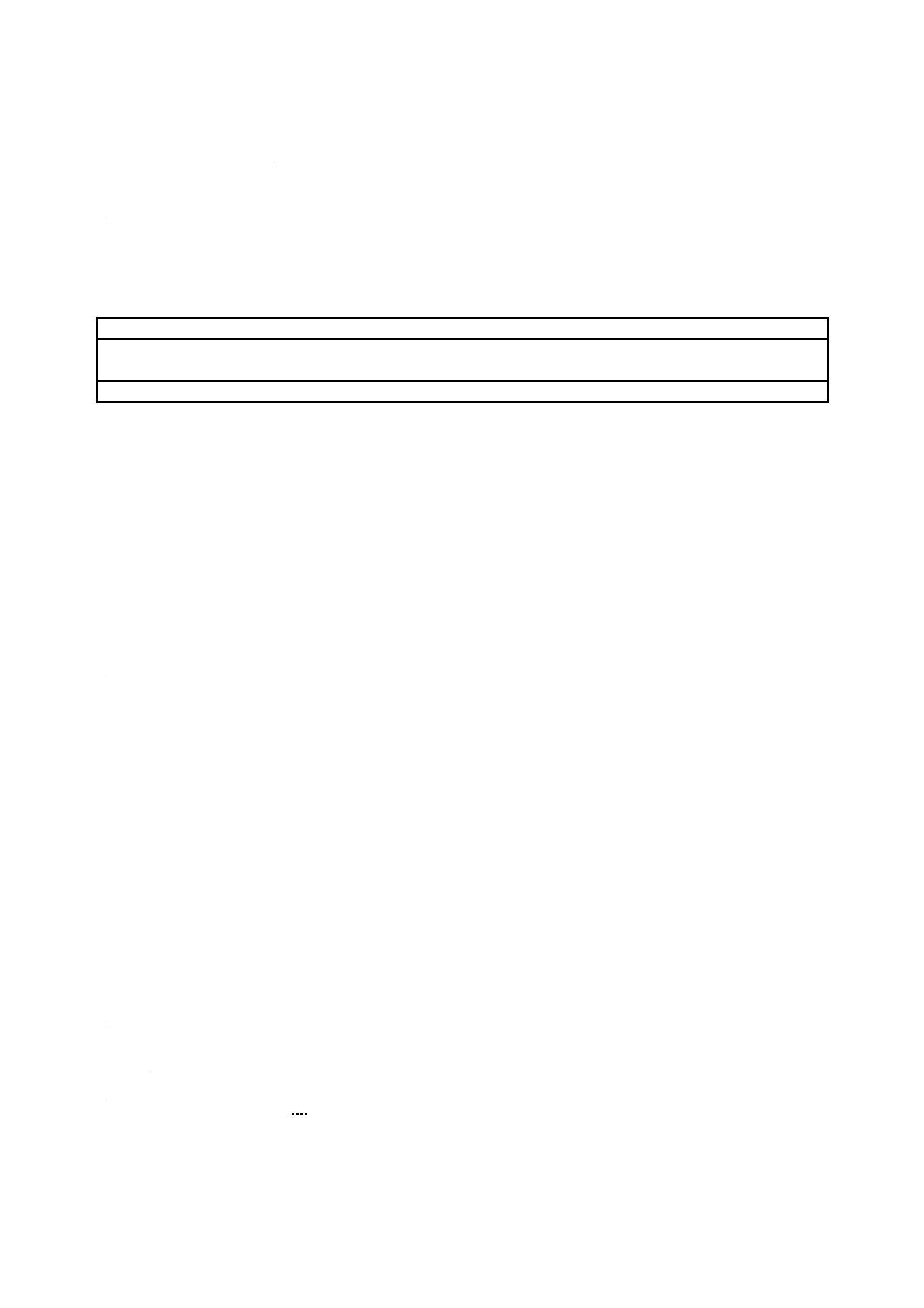

表36−IFDの物理的特性及び電気的特性の試験方法

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

7.1

外部端子の活性化

JIS X 6320-3

6.1,6.2.1,6.2.2

7.2

VCC端子

JIS X 6320-3

5.2.1

7.3

I/O端子

JIS X 6320-3

5.2.5

7.4

CLK端子

JIS X 6320-3

5.2.3

7.5

RST端子

JIS X 6320-3

5.2.2

7.6

SPU(C6)端子

JIS X 6320-3

5.2.4

7.7

外部端子の非活性化

JIS X 6320-3

6.4

表37−IFDの論理的な操作の試験方法−リセット応答(ATR)

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

8.1.1

ICカードのリセット(コールドリセット)

JIS X 6320-3

6.2.2

8.1.2

ICカードのリセット(ウォームリセット)

JIS X 6320-3

6.2.3

表38−IFDの論理的な操作の試験方法−T=0プロトコル

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

8.2.1

T=0プロトコルのI/O送信タイミング

JIS X 6320-3

7.1,7.2,10.2

8.2.2

T=0プロトコルのI/Oキャラクタ再送

JIS X 6320-3

7.3,10.2

8.2.3

T=0プロトコルのI/O受信タイミング

及び誤り信号

JIS X 6320-3

7.1,7.2,7.3,10.2

表39−IFDの論理的な操作の試験方法−T=1プロトコル

この規格の試験方法

対応する要求項目

細分箇条

試験項目名

基本規格

細分箇条

8.3.1

T=1プロトコルのI/O送信タイミング

JIS X 6320-3

7.1,7.2,8.3,11.2,11.3,

11.4.2,11.4.3

8.3.2

T=1プロトコルのI/O受信タイミング

JIS X 6320-3

7.1,7.2,8.3,11.2,11.3,

11.4.2,11.4.3

8.3.3

IFDのキャラクタ待ち時間(CWT)動作

JIS X 6320-3

11.4.3

8.3.4

キャラクタ待ち時間(CWT)を超えた

ICカードに対するIFD動作

JIS X 6320-3

11.4.3

8.3.5

ブロック保護時間(BGT)

JIS X 6320-3

11.4.3

8.3.6

IFDによるブロックシーケンス

JIS X 6320-3

11.6.3

8.3.7

IFDによる送信誤りの回復

JIS X 6320-3

11.6.3

8.3.8

IFSC調整

JIS X 6320-3

11.4.2

8.3.9

ICカードによる打切り

JIS X 6320-3

11.6.3

5

外部端子付きICカードの電気的特性の試験方法

5.1

VCC端子

この試験の目的は,VCC端子でICカードが消費する電流を測定すること,及びUCCの規定の範囲(JIS

X 6320-3の5.2.1参照)内でICカードが動作するかを確認することである。

14

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.1.1

試験装置

4.7.1に示す。

5.1.2

試験手順

ICカードをICカード試験装置に接続する。

a) ICカード試験装置に表40に示すパラメタを設定する(ICカードがサポートしている最低電圧の動作

クラスから始める。)。

表40−ICカード試験装置パラメタ

パラメタ

設定

UCC

UCC min

fCLK

fCLK max a)

注a) JIS X 6320-3の8.3に従ったfCLK max

b) ICカードをリセットする。

c) 試験シナリオを実行する。通信の間,表41で示される特性を継続的に監視し,値を測定する。

表41−測定信号

特性

値

ICC

ICC max

d) ICカードがJIS X 6320-3の6.3.2に従ったクロック停止をサポートしている場合,これを実行する。

クロック停止期間中,表41で示される信号及び値を継続的に監視し,値を測定する。

e) JIS X 6320-3の6.3.2に従いfCLKを再起動する。

注記 対応国際規格では5.3.4となっているが,6.3.2の間違いである。

f)

試験シナリオを実行する。通信の間,表41で示される特性及び値を継続的に監視し,値を測定する。

g) UCC=UCC maxでb) からf) までを繰り返す。

h) ICカードがサポートしている全ての動作クラスに対して,a) からg) までを繰り返す。

5.1.3

試験成績書

試験の間に測定された値,及び全ての通信がJIS X 6320-3に適合していたかどうかを試験成績書に記載

する。

5.2

I/O端子

この試験の目的は,I/O端子の静電容量,通常動作条件下(IOL max/min及びIOH max /min)のI/O端子の

出力電圧(UOH,UOL),ICカードの送信モードでのI/O端子のtR及びtF,並びにICカードの受信モードで

のI/O端子入力電流(IIL)を測定することである。

5.2.1

試験装置

4.7.1に示す。

5.2.2

試験手順

ICカードをICカード試験装置に接続する。

a) I/O端子の静電容量CIOを測定する。

b) ICカード試験装置に表42に示すパラメタを設定する(ICカードがサポートしている最低電圧の動作

クラスから始める。)。

15

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表42−ICカード試験装置パラメタ

パラメタ

設定

UCC

UCC max

UIH

UIH min

UIL

UIL min

IOH

a)

IOL

IOL max

tR

tR max

tF

tF max

注a) ICカードへの過電圧による損傷を防止するために,IOHの電流源の代わりに,VCC端子への20 kΩの抵抗(又

はその等価回路)を使用しなければならない。

c) ICカードをリセットする。

d) 試験シナリオを実行する。通信の間,表43で示される特性を継続的に監視し,値を測定する。

表43−測定すべき値

特性

値

IIH

IIH max

IIL

IIL max

UOH

UOH min,UOH max

UOL

UOL min,UOL max

tR

tR max

tF

tF max

e) ICカードへの電力供給を停止する。

f)

ICカード試験装置に表42に示すパラメタを設定する。

g) ICカードをリセットする。

h) 試験シナリオを実行する。通信の間,表43で示される特性及び値を継続的に監視し,値を測定する。

i)

ICカードへの電力供給を停止する。

j)

ICカードがサポートしている全ての動作クラスに対してb) からi) までを繰り返す。

5.2.3

試験成績書

I/O端子の静電容量の値,試験の間に測定された値,及び全ての通信がJIS X 6320-3に適合していたか

どうかを試験成績書に記載する。

5.3

CLK端子

この試験の目的は,ICカードのCLK端子消費電流を測定すること,並びに規定のクロック周期及びク

ロック波形(JIS X 6320-3の5.2.3及び8.3参照)内でICカードが動作するかを確認することである。

5.3.1

試験装置

4.7.1に示す。

5.3.2

試験手順

ICカードをICカード試験装置に接続する。

a) CLK端子の静電容量CCLKを測定する。

b) ICカード試験装置に表44に示すパラメタを設定する(ICカードがサポートしている最低電圧の動作

クラスから始める。)。

16

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表44−ICカード試験装置パラメタ

パラメタ

設定

UCC

UCC max

UIH

UIH min

UIL

UIL min

fCLK

fCLK min

デューティサイクル

40 %状態H

c) ICカードをリセットする。

d) fCLKをJIS X 6320-3の5.2.3及び8.3に従ったfCLK maxに設定する。

e) 試験シナリオを実行する。通信の間,表45で示される特性を継続的に監視し,値を測定する。

表45−測定すべき値

特性

値

IIH

IIH max

IIL

IIL max

f)

ICカードへの電力供給を停止する。

g) ICカード試験装置に表44に示すパラメタを設定する。

h) ICカードをリセットする。

i)

試験シナリオを実行する。通信の間,表45で示される特性及び値を継続的に監視し,値を測定する。

j)

ICカードへの電力供給を停止する。

k) ICカードがサポートしている全ての動作クラスに対してb) からj) までを繰り返す。

5.3.3

試験成績書

CLK端子の静電容量の値,試験の間に測定された値,及び全ての通信がJIS X 6320-3に適合していたか

どうかを試験成績書に記載する。

5.4

RST端子

この試験の目的は,ICカードのRST端子消費電流を測定すること,並びに許容されるRST信号の最小

及び最大のタイミングと電圧とでICカードが動作するかを確認することである(JIS X 6320-3の5.2.2参

照)。

5.4.1

試験装置

4.7.1に示す。

5.4.2

試験手順

ICカードをICカード試験装置に接続する。

a) RST端子の静電容量CRSTを測定する。

b) ICカード試験装置に表46に示すパラメタを設定する(ICカードがサポートしている最低電圧の動作

クラスから始める。)。

17

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表46−ICカード試験装置パラメタ

パラメタ

設定

UCC

UCC max

UIH

UIH min

UIL

UIL min

fCLK

fCLK min

c) ICカードをリセットする。

d) 試験シナリオを実行する。通信の間,表47で示される特性を継続的に監視し,値を測定する。

表47−測定すべき値

特性

値

IIH

IIH max

IIL

IIL max

e) ICカードへの電力供給を停止する。

f)

ICカード試験装置に表46に示すパラメタを設定する。

g) ICカードをリセットする。

h) 試験シナリオを実行する。通信の間,表47で示される特性及び値を継続的に監視し,値を測定する。

i)

ICカードへの電力供給を停止する。

j)

ICカードがサポートしている全ての動作クラスに対してb) からi) までを繰り返す。

5.4.3

試験成績書

RST端子の静電容量の値,試験の間に測定された値,及び全ての通信がJIS X 6320-3に適合していたか

どうかを試験成績書に記載する。

5.5

SPU(C6)端子

SPU(C6)端子に適用する標準試験は,存在しない。この端子が専用のアプリケーションで使われる場合

は,アプリケーション固有の試験を適用することが望ましい。

6

外部端子付きICカードの論理的な操作の試験方法

6.1

リセット応答

6.1.1

コールドリセット及びリセット応答(ATR)

この試験の目的は,JIS X 6320-3の6.2.2に従ったコールドリセット手順中のICカードの動作を測定す

ることである。

6.1.1.1

試験装置

4.7.1に示す。

6.1.1.2

試験手順

ICカードをICカード試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

注記 “全ての信号遷移(レベル及びタイミング)を記録する。”とは,クロック信号の毎回の遷移ま

で記録することを求めているのではなく,各端子の信号遷移(レベルとタイミングとの相関関

18

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

係)が確認できる内容で十分であり,グラフ化した場合,JIS X 6320-3の図1のようになるも

のを求めている。

a) JIS X 6320-3の6.2.1に従い,ICカードを活性化する。

b) CLK端子を活性化し,400クロックサイクルの後,RST端子を状態Hに設定する。

c) ICカードがATRを送信中に,少なくともATRの1キャラクタ(無作為に選ばれる。)に対してJIS X

6320-3の7.3に従った送信誤り信号を送る。

d) ICカードを用いて試験シナリオを実行する。

e) ICカードへの電力供給を停止する。

6.1.1.3

試験成績書

信号の記録及びATRを試験成績書に記載する。

6.1.2

ウォームリセット

この試験の目的は,JIS X 6320-3の6.2.3に従ったウォームリセット手順中のICカードの動作を測定す

ることである。

6.1.2.1

試験装置

4.7.1に示す。

6.1.2.2

試験手順

ICカードをICカード試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) JIS X 6320-3の6.2.1及び6.2.2に従いICカードを活性化し,リセットする。

b) ICカードを用いて試験シナリオを実行する。

c) JIS X 6320-3の6.2.3に従い,400クロックサイクルの間,RST端子を状態Lにしてウォームリセット

を開始する。

d) ICカードがATRを送信中に,少なくともATRの1キャラクタ(無作為に選ばれる。)に対してJIS X

6320-3の7.3に従った送信誤り信号を送る。

e) ICカードを用いて試験シナリオを実行する。

f)

ICカードへの電力供給を停止する。

6.1.2.3

試験成績書

信号の記録及びATRを試験成績書に記載する。

6.2

T=0プロトコル

ICカードがT=0プロトコルをサポートしている場合だけ,次の試験を行う。

注記 εtは,“表14−I/Oキャラクタの生成タイミングの精度(受信モード)”で定義する。

6.2.1

T=0プロトコルのI/O伝送タイミング

この試験の目的は,ICカードによって送信されるデータのタイミングを測定することである(JIS X

6320-3の7.1,7.2及び10.2参照)。

6.2.1.1

試験装置

4.7.1に示す。

6.2.1.2

試験手順

ICカードをICカード試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

19

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) 規定のビットタイミングパラメタでICカードの試験シナリオを実行する(JIS X 6320-3の10.2参照)。

b) 全ての実行可能なETU因子でa) を繰り返す。

c) 対応すべき全てのアプリケーションに対して,a) からb) までを繰り返す。

6.2.1.3

試験成績書

プロトコルの記録を試験成績書に記載する。

6.2.2

T=0プロトコルのI/Oキャラクタ再送

この試験の目的は,ICカードによるキャラクタ再送の実行とタイミングとを測定することである(JIS X

6320-3の7.3参照)。

6.2.2.1

試験装置

4.7.1に示す。

6.2.2.2

試験手順

ICカードをICカード試験装置に接続する。

a) 規定のキャラクタタイミングでICカードの試験シナリオを実行する(JIS X 6320-3の7.2参照)。

b) 次のc)〜e) の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な

内容だけでなく,全ての信号遷移(レベル及びタイミング)を記録する。

c) ICカードから送信される各バイトに対して5回連続して最小時間の誤り状況を生成する。その条件と

はJIS X 6320-3の7.3に従い,開始ビットの先端と誤り信号の先端との時間差を,規定された最小値

[(10.5−0.2) etu+εt]にして,最小期間(1 etu+εt)の誤り信号を送出することである。

d) ICカードから送信される各バイトに対して5回連続して最大時間の誤り状況を生成する。その条件と

はJIS X 6320-3の7.3に従い,開始ビットの先端と誤り信号の先端との時間差を,規定された最大値

[(10.5+0.2) etu−εt]にして,最大期間(2 etu−εt)の誤り信号を送出することである。

e) ICカードがもつ全てのATRに対して,c) からd) までを繰り返す(JIS X 6320-3の6.2.4参照)。

6.2.2.3

試験成績書

プロトコルの記録を試験成績書に記載する。

6.2.3

T=0プロトコルのI/O受信タイミング及び誤り信号

この試験の目的は,ICカードの受信タイミング及び誤り信号を測定することである(JIS X 6320-3の7.1,

7.2,7.3及び10.2参照)。

6.2.3.1

試験装置

4.7.1に示す。

6.2.3.2

試験手順

ICカードをICカード試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) ICカード試験装置に,表48に示すビットタイミングパラメタを設定する。

20

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表48−ICカード試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最大[tn = (n+0.2) etu−εt]

JIS X 6320-3の箇条7

連続する二つのキャラクタ間の遅延

9 600 etu

注記 JIS X 6320-3のICカードは,

最大値を定義していない。

b) ICカードを用いて試験シナリオを実行する。

c) 1バイトに対して5回連続するパリティ誤りを生成し,その後,有効な1バイトを送信する。引き続

き次に送信する1バイトに対して5回連続するパリティ誤りを生成する。

d) 全ての実行可能なETU因子でa) からc) までを繰り返す。

e) ICカード試験装置に,表49に示すビットタイミングパラメタを設定する。

表49−ICカード試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最小[tn = (n−0.2) etu+εt]

JIS X 6320-3の箇条7

連続する二つのキャラクタ間の遅延

12 etu+R×N / f+εt

JIS X 6320-3の箇条7

f)

b) からd) までを繰り返す。

g) 対応すべき全てのアプリケーションで,a) からf) までを繰り返す。

6.2.3.3

試験成績書

プロトコルの記録を試験成績書に記載する。

6.3

T=1プロトコル

ICカードがT=1プロトコルをサポートしている場合だけ,次の試験を行う。

試験中に偶然の伝送エラーが発生する場合,エラー回復手続は,JIS X 6320-3の11.6.2に従って行われ

なければならない。

注記 この6.3の試験方法の記述では,図で示される試験シナリオを含んでいるものがある。これら

のシナリオは,ICカードが,長さ36バイトであり,データとして“31 32 33 34 … 54”が記録

される透過ファイルをもち,2バイト読出しのREAD BINARYコマンド[I(0,0) (INF =“00 B0

00 00 02”)]が実行可能であることを想定している。

6.3.1

T=1プロトコルのI/O送信タイミング

この試験の目的は,ICカードによって送信されるデータのタイミングを測定することである(JIS X

6320-3の7.1,7.2,8.3,11.2,11.3,11.4.2及び11.4.3参照)。

6.3.1.1

試験装置

4.7.1に示す。

6.3.1.2

試験手順

ICカードをICカード試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) 規定のビットタイミングパラメタ(JIS X 6320-3の11.2参照),及びATRのN(JIS X 6320-3の8.3参

照)によって定義される連続する二つのキャラクタ間の最小遅延で,少なくとも1秒の間,代表的な

プロトコルT=1及びICカードアプリケーション固有通信を実行する。

21

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

b) 全ての実行可能なETU因子でa) を繰り返す。

c) 対応すべき全てのアプリケーションで,a) からb) までを繰り返す。

6.3.1.3

試験成績書

プロトコルの記録を試験成績書に記載する。

6.3.2

T=1プロトコルのI/O受信タイミング

この試験の目的は,T=1プロトコルのもとでICカードの受信タイミングを測定することである(JIS X

6320-3の7.1,7.2,8.3,11.2,11.3,11.4.2及び11.4.3参照)。

6.3.2.1

試験装置

4.7.1に示す。

6.3.2.2

試験手順

ICカードをICカード試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) ICカード試験装置に,表50に示すビットタイミングパラメタを設定する。

表50−ICカード試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最大[tn = (n+0.2) etu−εt]

JIS X 6320-3の箇条7

保護時間

最大値

JIS X 6320-3の箇条7及び11.4.3

連続する二つのキャラクタ間の遅延

(11+2CWI) etu−εt

JIS X 6320-3の11.4.3

b) 少なくとも1秒の間,代表的なプロトコルT=1及びICカードアプリケーション固有通信を実行する。

c) 全ての実行可能なETU因子でa) からb) までを繰り返す。

d) ICカード試験装置に,表51に示すビットタイミングパラメタを設定する。

表51−ICカード試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最小[tn = (n−0.2) etu+εt]

JIS X 6320-3の箇条7

保護時間

最小値

JIS X 6320-3の箇条7及び11.4.3

連続する二つのキャラクタ間の遅延

12 etu+R×N / f+εt

JIS X 6320-3の8.3

e) 少なくとも1秒の間,代表的なプロトコルT=1及びICカードアプリケーション固有通信を実行する。

f)

全ての実行可能なETU因子でd) からe) までを繰り返す。

6.3.2.3

試験成績書

プロトコルの記録を試験成績書に記載する。

6.3.3

キャラクタ待ち時間(CWT)の動作

この試験の目的は,CWTに関してICカードの応答を測定することである(JIS X 6320-3の箇条7及び

11.4.3参照)。

注記 次の試験手順の説明で使用される表記法は,JIS X 6320-4で定義される。

6.3.3.1

試験装置

4.7.1に示す。

22

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

6.3.3.2

試験手順

ICカードをICカード試験装置に接続する。

a) 少なくとも2バイトのデータがある透過ファイルを選択する。

b) ATRで通知されたCWTでnバイトのブロックをICカードへ送信する。

c) ICカードの応答の有無,内容及びタイミングを記録する。

シナリオ1−キャラクタ待ち時間(CWT)の動作

ICカード試験装置

ICカード

I(0,0) (INF a) =“00 B0 00 00 02”)

→

←

ICカードの応答

注a) コマンドを示すINFフィールドは,READ BINARY2バイトである。

6.3.3.3

試験成績書

ICカードの応答の有無,内容及びタイミングを試験成績書に記載する。

6.3.4

キャラクタ待ち時間(CWT)を超えたときのIFDへのICカードの動作

この試験の目的は,CWTを超えたときの,IFDへのICカードの応答を測定することである(JIS X 6320-3

の5.2.5,箇条7及び11.2参照)。

6.3.4.1

試験装置

4.7.1に示す。

6.3.4.2

試験手順

ICカードをICカード試験装置に接続する。

a) nバイトブロックのnバイト未満のデータをICカードへ送信する。

b) ICカードの応答の有無,内容及びタイミングを記録する。

注記 中断によって起こり得る衝突においてICカードの応答を調査するのが望ましい。

6.3.4.3

試験成績書

ICカードの応答の有無,内容及びタイミングを試験成績書に記載する。

6.3.5

ブロック保護時間(BGT)

この試験の目的は,対向する方向へ送信される連続する二つのキャラクタの先端間の時間(BGT)を測

定することである(JIS X 6320-3の11.4.3参照)。

6.3.5.1

試験装置

4.7.1に示す。

6.3.5.2

試験手順

ICカードをICカード試験装置に接続する。

6.3.5.2.1

試験手順1

a) 少なくとも2バイトのデータがある透過ファイルを選択する。

b) 正常なIブロックを組み立てる。

c) IブロックをICカードへ送信する。

d) ICカードが,規則1(JIS X 6320-3の11.6.2.3参照)に従って,正常なIブロックで応答するのを待つ。

23

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

シナリオ2−ブロック保護時間(BGT),試験手順1

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF =“31 32 90 00”)

e) ICカード試験装置からの最終キャラクタのスタートビットの先端から,ICカード応答の先頭キャラク

タのスタートビットの先端までのタイミングを記録する。

6.3.5.2.2

試験手順2

a) 少なくとも2バイトのデータがある透過ファイルを選択する。

b) EDC(error detection character)が誤っているIブロックを組み立てる。

c) IブロックをICカードへ送信する。

d) ICカードは,規則7.1(JIS X 6320-3の11.6.3.2参照)に従って,プロトコル制御バイト(PCB)でEDC

誤りを示すRブロックを正確に送信する。

シナリオ3−ブロック保護時間(BGT),試験手順2

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”) (EDC = 誤り)

→

←

R(0) (PCB =“81”)

e) ICカード試験装置からの最終キャラクタのスタートビットの先端から,ICカード応答の先頭キャラク

タのスタートビットの先端までのタイミングを記録する(JIS X 6320-3の11.4.3参照)。

6.3.5.3

試験成績書

記録されたタイミングを試験成績書に記載する。

6.3.6

ICカードによるブロックシーケンス

この試験の目的は,送信誤りに対するICカードの応答を測定することである(JIS X 6320-3の11.6.3参

照)。

誤りを含むブロックとは,送信誤り(すなわち,パリティが誤っている一つ以上のキャラクタ)又は最

終フィールドに誤りがあるブロックである。

6.3.6.1

試験装置

4.7.1に示す。

6.3.6.2

試験手順

ICカードをICカード試験装置に接続する。

6.3.6.2.1

試験手順1

a) ICカードをリセットする。

b) ICカードへ誤りを含むブロックを送信する。

c) ICカードが,BWT以内にブロックを送り始めないか,又はR(0)を送った場合,ICカードへ正常なブ

ロックを再送信する。

24

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

シナリオ4−ICカードによるブロックシーケンス,試験手順1

ICカード試験装置

ICカード

I(0,0) (INF =“00”) (EDC = 誤り)

→

←

R(0) (PCB =“81”)

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF = 応答)

d) ICカードの応答を記録する。

6.3.6.2.2

試験手順2

a) ICカードをリセットする。

b) ICカードへICカードがサポートしているコマンドを含むブロックI(0,0)を送信する。

c) ICカードの応答を待ってからICカードへ誤りを含むブロックを送信する。

d) ICカードが,BWT以内にブロックを送り始めないか,又はPCBのビットb1に1を設定したR(1)を送

った場合,ICカードへ誤りを含むブロックを3回まで再送信する。

シナリオ5−ICカードによるブロックシーケンス,試験手順2

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF =“31 32 90 00”)

I(1,0) (INF =“00”) (EDC = 誤り)

→

←

R(1) (PCB =“91”)

I(1,0) (INF =“00”) (EDC = 誤り)

→

←

R(1) (PCB =“91”)

I(1,0) (INF =“00”) (EDC = 誤り)

→

←

ICカードの応答

e) 最後のブロックを受け取った後,ICカードが無応答のままであったか否かを含め,ICカードの応答を

記録する。

6.3.6.2.3

試験手順3(ブロック連鎖)

a) ICカードをリセットする。

b) ブロック連鎖を必要とするコマンドを含むINFをもつブロックI(0,1)をICカードへ送信する。

c) ICカードの応答を待ってから誤りを含むブロックをICカードへ送信する。

d) ICカードが,BWT以内にブロックを送り始めないか,又はPCBのビットb1に“1”を設定したR(1)

を送った場合,ICカードへ誤りを含むブロックを再送信する。

シナリオ6−ICカードによるブロックシーケンス,試験手順3(ブロック連鎖)

ICカード試験装置

ICカード

I(0,1) (INF = コマンドの始まり)

→

←

R(1) (PCB =“90”)

I(1,0) (INF = コマンドの終わり) (EDC = 誤り)

→

←

R(1) (PCB =“91”)

I(1,0) (INF = コマンドの終わり) (EDC = 誤り)

→

←

R(1) (PCB =“91”)

I(1,0)(INF = コマンドの終わり)

→

←

ICカード応答

25

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

e) ICカードの応答を記録する。

6.3.6.3

試験成績書

各々の試験手順に対してICカードの応答を試験成績書に記載する。

6.3.7

プロトコル誤りに対するICカードの動作

この試験の目的は,プロトコル誤りに対するICカードの応答(JIS X 6320-3の11.6.3参照)を分析する

ことである。

欠陥ブロックとは,次のいずれかをいう。

− 未定義のPCB符号化がある無効ブロック

− 誤ったN(S),N(R),又はMがあるPCB符号化を含む無効ブロック

− 予期されたブロックと一致しないPCBがある無効ブロック

6.3.7.1

試験装置

4.7.1に示す。

6.3.7.2

試験手順

ICカードをICカード試験装置に接続する。

a) ICカードをリセットする。

b) ICカードへ欠陥ブロックを送信する。

c) ICカードが,BWT以内にブロックを送り始めないか,又はPCBのビットb2に1を設定したR(0)を送

った場合,ICカードへ正しいブロックを送信する。ICカードが無応答の場合,この時点で試験を終了

する。

シナリオ7−プロトコル誤りに対するICカードの応答

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”) (PCB = 誤り)

→

←

R(0) (PCB =“82”) 又はICカード無応答

I(0,0) (INF =“00 B0 00 00 02”)

→

←

ICカード応答

この試験は,誤りが異なるタイプのPCBで繰り返してもよい。

6.3.7.3

試験成績書

ICカードの応答を試験成績書に記載する。

6.3.8

ICカードによる送信誤りの回復

この試験の目的は,否定応答に対するICカードの応答(JIS X 6320-3の11.6.3参照)を分析することで

ある。否定応答とは,シーケンス番号がずれたN(R)の付いたRブロックである。

6.3.8.1

試験装置

4.7.1に示す。

6.3.8.2

試験手順

ICカードをICカード試験装置に接続する。

a) ICカードをリセットする。

b) ICカードが,サポートしているコマンド(オフセットなしで2バイトを読み出すREAD BINARYコマ

ンド)を含むINFのあるブロックI(0,0)を送信し,ブロックI(0,0)又はI(1,0)の応答を待つ。

26

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

c) ICカードへR(0),又はR(1)を送信する。ICカードからの応答を得る。

d) ICカードは,Iブロックを再送する。

シナリオ8−ICカードによる送信誤りの回復

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF =“31 32 90 00”)

R(0) (PCB =“81”)

→

←

I(0,0) (INF =“31 32 90 00”)

I(1,0) (INF =“00 B0 00 00 02”)

→

←

I(1,0) (INF =“31 32 90 00”)

R(1) (PCB =“91”)

→

←

I(1,0) (INF =“31 32 90 00”)

6.3.8.3

試験成績書

ICカードの応答を試験成績書に記載する。

6.3.9

再同期

この試験の目的は,再同期後のICカードの動作(JIS X 6320-3の11.6.3参照)を確認することである。

6.3.9.1

試験装置

4.7.1に示す。

6.3.9.2

試験手順

ICカードをICカード試験装置に接続する。

a) ICカードをリセットする。

b) ICカードがサポートしているコマンドで,双方向に二つのIブロックを交換する。

c) 否定応答ブロックを2回送り,ICカードへS(RESYNCH request)ブロックを送信する。

d) ICカードの応答を記録する。

e) ICカードがS(RESYNCH response)を送信した場合,ICカードへI(0,0)ブロックを送信する。

f)

ICカードの応答を記録する。

シナリオ9−再同期

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF =“31 32 90 00”)

I(1,0) (INF =“00 B0 00 00 03”)

→

←

I(1,0) (INF =“31 32 33 90 00”)

R(1) (PCB =“91”)

→

←

I(1,0) (INF =“31 32 33 90 00”)

R(1) (PCB =“91”)

→

←

I(1,0) (INF =“31 32 33 90 00”)

S(RESYNCH request)

→

←

S(RESYNCH response)

I(0,0)

→

←

ICカード応答

27

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

6.3.9.3

試験成績書

ICカードの応答を試験成績書に記載する。

6.3.10 IFSD調整

この試験の目的は,IFSD調整(JIS X 6320-3の11.4.2参照)を確認することである。

6.3.10.1 試験装置

4.7.1に示す。

6.3.10.2 試験手順

ICカードをICカード試験装置に接続する。

a) ICカードをリセットする。

b) ICカードがサポートしているコマンドで,双方向に一つのIブロックを交換する。

c) ICカードへブロックS(IFS request)を送信する。

シナリオ10−IFSD調整

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF =“31 32 90 00”)

S(IFS request)

→

←

ICカード応答

d) ICカードの応答を記録する。

6.3.10.3 試験成績書

ICカードの応答を試験成績書に記載する。

6.3.11 IFDによる打切り

この試験の目的は,ICカードのブロック連鎖打切りの動作(JIS X 6320-3の11.6.3参照)を確認するこ

とである。

6.3.11.1 試験装置

4.7.1に示す。

6.3.11.2 試験手順

a) ICカードをリセットする。

b) ICカードがサポートしているコマンドで,双方向に一つのIブロックを交換する。

c) ICカードがサポートしているブロック連鎖を必要としているコマンドを含むINFのあるブロックI(1,

1)をICカードに送信する。

d) ICカードの応答を待ち,S(ABORT request)を送信する。

シナリオ11−IFDによる打切り

ICカード試験装置

ICカード

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (INF =“31 32 90 00”)

I(1,1) (INF =“00 B0”)

→

←

R(0) (PCB =“80”)

S(ABORT request)

→

←

ICカード応答

28

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

e) ICカードの応答の有無及び内容を記録する。

6.3.11.3 試験成績書

ICカードの応答の有無及び内容を試験成績書に記載する。

7

IFDの物理的特性及び電気的特性の試験方法

7.1

外部端子の活性化

この試験の目的は,ICカードを活性化するときの外部端子の活性化シーケンス(JIS X 6320-3の6.1,6.2.1

及び6.2.2参照)を測定することである。

7.1.1

試験装置

4.7.2に示す。

7.1.2

試験手順

IFDをIFD試験装置に接続する。

a) 少なくとも1秒の間,IFDの外部端子上で信号のレベル及びタイミングを測定する。

b) IFDを活性化する。

c) 少なくとも1秒の間,IFDの外部端子上で信号のレベル及びタイミングを測定する。

“IFDの活性化”で必要な活性化手順は,IFDの構造に依存している。“IFDの活性化”で必要な活性化

手順は,“カードのコールドリセット”をIFDが実行するまでの必要な全ての手順を含まなければならな

い(JIS X 6320-3の6.2.1参照)。

20 nsの値は,JIS X 6320-3で異なる値が定義されるまで,外部端子活性化期間の二つの信号を遷移させ

る間の最小時間として使用されなければならない。

注記 対応国際規格では7.1.3に記載があるが,試験手順に関する説明のため7.1.2に移動した。

7.1.3

試験成績書

全てのIFDの外部端子信号のレベル及びタイミングの記録を試験成績書に記載する。

7.2

VCC端子

この試験の目的は,IFDのVCC端子の電圧(JIS X 6320-3の5.2.1参照)を測定することである。

7.2.1

試験装置

4.7.2に示す。

7.2.2

試験手順

IFDをIFD試験装置に接続する。

a) IFD試験装置に表52に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスで始

める。)。

表52−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC min

b) IFDを活性化する。

c) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2)。

d) 表53に示すパラメタでATRを発生させる。

29

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表53−ATRパラメタ

パラメタ

設定

参照

Fi

利用可能な最小値

JIS X 6320-3の8.3

X

"11"

JIS X 6320-3の8.3

e) IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

f)

IFDで,IFD試験装置を用いて試験シナリオを実行する。全ての通信期間中,JIS X 6320-3の5.2.1で

定義された範囲内のスパイク電流を,1 kHzから100 kHzまでの間でランダムに選んだ周波数で発生

させる。この通信期間中,表54で示される信号を継続して監視し,値を測定する。

表54−測定すべき値

特性

値

UCC

UCC min,UCC max

g) IFDがクロック停止(JIS X 6320-3の6.3.2参照)を発生させる場合,IFD試験装置のパラメタICCを

クロック停止期間中ICC maxに設定する。クロック停止期間中,表54で示される信号を継続して監視

し,値を測定する。

h) IFDを非活性化する。

i)

IFD試験装置に表55に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表55−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

j)

IFDを活性化する。

k) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2)。

l)

表56に示すパラメタでATRを発生させる。

表56−ATRパラメタ

パラメタ

設定

参照

Fi

利用可能な最大値

JIS X 6320-3の8.3

X

"11"

JIS X 6320-3の8.3

m) IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

n) IFDで,IFD試験装置を用いて試験シナリオを実行する。全ての通信期間中,JIS X 6320-3の5.2.1で

定義された範囲内のスパイク電流を,1 kHzから100 kHzまでの間でランダムに選んだ周波数で発生

させる。この通信期間中,表54で示される信号を継続して監視し,測定する。

o) IFDがクロック停止(JIS X 6320-3の6.3.2参照)を発生させる場合,IFD試験装置のパラメタICCを

クロック停止期間中ICC maxに設定する。クロック停止期間中,表54で示される信号を継続して監視

し,値を測定する。

30

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

p) IFDを非活性化する。

q) IFDがサポートしている全ての動作クラスに対し,a) からp) までを繰り返す。

7.2.3

試験成績書

測定条件(ICC及びF)と一緒に上記全てのシナリオで測定したUCC max及びUCC minを試験成績書に記

載する。

7.3

I/O端子

この試験の目的は,I/O端子の静電容量,通常操作条件下(IOL max/min及びIOH max /min)のI/O端子出

力電圧(UOH,UOL),IFDの送信モード期間中のI/O端子のtR及びtF,並びにIFDの受信モード期間中のI/O

端子入力電流(IIL)を測定することである。

7.3.1

試験装置

4.7.2に示す。

7.3.2

試験手順

IFDをIFD試験装置に接続する。

a) I/O端子の静電容量CIOを測定する。

b) IFD試験装置に表57に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表57−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

IIH

IIH max

IIL

IIL max

UOH

UOH min

UOL

UOL max

tR

tR min

tF

tF min

c) IFDを活性化する。

d) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2)。

e) ATRを発生させる。

f)

IFD試験装置を用いて試験シナリオを実行する。この通信期間中,表58で示される特性を継続して監

視し,値を測定する。

表58−測定すべき値

特性

値

UIH

UIH min,UIH max

UIL

UIL min,UIL max

IOH

IOH max

IOL

IOL max

tR

tR max

tF

tF max

31

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

g) IFDを非活性化する。

h) IFD試験装置に表59に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表59−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

IIH

IIH min

IIL

IIL min

UOH

UOH min

UOL

UOL min

tR

tR max

tF

tF max

i)

ICカードをリセットする。

j)

試験シナリオを実行する。この通信期間中,表58で示される特性を継続して監視し,測定する。

k) IFDを非活性化する。

l)

IFDがサポートしている動作クラスに対し,b) からk) までを繰り返す。

7.3.3

試験成績書

I/O端子の静電容量,試験手順に従って測定された値,及び全ての通信がJIS X 6320-3に適合している

かを試験成績書に記載する。

7.4

CLK端子

この試験の目的は,CLK信号の特性を測定することである(JIS X 6320-3の5.2.3参照)。

7.4.1

試験装置

4.7.2に示す。

7.4.2

試験手順

IFDをIFD試験装置に接続する。

a) IFD試験装置に表60に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表60−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

IIH

IIH max

IIL

IIL max

b) IFDを活性化する。

c) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2参照)。

d) 表61に示すパラメタでATRを発生させる。

32

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表61−ATRパラメタ

パラメタ

設定

参照

Fi

Fi max

JIS X 6320-3の8.3

Di

Di min

JIS X 6320-3の8.3

e) IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

f)

IFD試験装置を用いて試験シナリオを実行する。この通信期間中,表62で示される特性を継続して監

視し,値を測定する。

表62−測定すべき値

特性(CLK)

値

UIH

UIH min,UIH max

UIL

UIL min,UIL max

tR

tR max

tF

tF max

デューティサイクル

min,max

g) IFDを非活性化する。

h) IFD試験装置に表63に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表63−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

IIH

IIH min

IIL

IIL min

i)

IFDを活性化する。

j)

IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2)。

k) 表61に示すパラメタでATRを発生させる。

l)

IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

m) IFD試験装置を用いて試験シナリオを実行する。この通信期間中,表62で示される特性を継続して監

視し,値を測定する。

n) IFDを非活性化する。

o) サポートしている全ての動作クラスに対し,a) からn) までを繰り返す。

7.4.3

試験成績書

試験手順に従って測定された値,各パラメタ,及び全ての通信がJIS X 6320-3に適合しているかを試験

成績書に記載する。

7.5

RST端子

この試験の目的は,RST信号の特性を測定することである(JIS X 6320-3の5.2.2参照)。

7.5.1

試験装置

4.7.2に示す。

33

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

7.5.2

試験手順

IFDをIFD試験装置に接続する。

a) IFD試験装置に表64に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表64−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

IIH

IIH max

IIL

IIL max

b) IFDを活性化する。

c) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2参照)。

d) ATRを発生させる。

e) IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

f)

IFD試験装置を用いて試験シナリオを実行する。この通信期間中,表65で示される特性を継続して監

視し,値を測定する。

表65−測定すべき値

特性 (RST)

値

UIH

UIH min,UIH max

UIL

UIL min,UIL max

tR

tR max

tF

tF max

g) IFDを非活性化する。

h) IFD試験装置に表66に示すパラメタを設定する(IFDがサポートしている最低電圧の動作クラスから

始める。)。

表66−IFD試験装置パラメタ

パラメタ

設定

ICC

ICC max

IIH

IIH min

IIL

IIL min

i)

IFDを活性化する。

j)

IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2)。

k) ATRを発生させる。

l)

IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

m) IFD試験装置を用いて試験シナリオを実行する。この通信期間中,表65で示される特性を継続して監

視し,値を測定する。

34

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

n) IFDを非活性化する。

o) IFDがサポートしている全ての動作クラスに対し,a) からn) までを繰り返す。

7.5.3

試験成績書

試験手順で定められた値及び対応するパラメタを試験成績書に記載する。

7.6

SPU(C6)端子

ICカードのSPU(C6)が電気的に絶縁されないときだけ,この試験は適用される。この試験の目的は,

SPU(C6)端子に関してIFDによって提供される電圧を測定することである(JIS X 6320-3の5.2.4参照)。

7.7

外部端子の非活性化

この試験の目的は,IFDによる外部端子の非活性化シーケンスを測定することである(JIS X 6320-3の

6.4参照)。

7.7.1

試験装置

4.7.2に示す。

7.7.2

試験手順

IFDをIFD試験装置に接続する。

a) IFDを活性化する。

b) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2参照)。

c) ATRを発生させる。

d) IFDがPPSを発生させる場合,要求パラメタのPPS応答を送信する。

e) IFD試験装置を用いて試験シナリオを実行する。通信の間又は終わりでRST信号の立下がりエッジで

始まる全ての非活性化の手順に対して,VCC端子,RST端子,CLK端子及びI/O端子を継続して監視

し,電圧及び信号遷移のタイミングを記録する。

20 nsの値は,JIS X 6320-3で異なる値が定義されるまで,外部端子活性化期間の二つの信号を遷移させ

る間の最小時間として使用されなければならない。

7.7.3

試験成績書

記録された全てのIFD外部端子の信号のレベル及びタイミングを試験成績書に記載する。

8

IFDの論理的な操作の試験方法

8.1

リセット応答

8.1.1

ICカードのリセット(コールドリセット)

この試験の目的は,IFDによって提供されるコールドリセットの動作を測定することである(JIS X

6320-3の6.2.2参照)。

8.1.1.1

試験装置

4.7.2に示す。

8.1.1.2

試験手順

IFDをIFD試験装置に接続する。

a) IFDを活性化する。

b) RST信号を継続して監視し,少なくとも1秒の間,RST端子のタイミング(CLK信号との関係)及び

電圧の変化を測定する。

8.1.1.3

試験成績書

RST端子の全ての信号のタイミング及び電圧の変化を試験成績書に記載する。

35

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

8.1.2

ICカードのリセット(ウォームリセット)

この試験の目的は,IFDによって提供されるウォームリセットの動作を測定することである(JIS X

6320-3の6.2.3参照)。

8.1.2.1

試験装置

4.7.2に示す。

8.1.2.2

試験手順

IFDをIFD試験装置に接続する。

a) IFDを活性化する。

b) IFDは,IFD試験装置をリセットする(JIS X 6320-3の6.2.2参照)。

c) ATRを生成させる。

d) IFDがPPSを発生させる場合,要求されたパラメタでPPS応答を送信する。

e) IFD試験装置を用いて試験シナリオを実行する。この通信の間,RST信号を継続的に監視し,全ての

信号のタイミング(CLK信号との関係)及び電圧の変化を記録する。

8.1.2.3

試験成績書

IFDによって提供される全てのウォームリセットの電圧及びタイミングを試験成績書に記載する。

8.2

T=0プロトコル

IFDがT=0プロトコルをサポートしている場合だけ次の試験を行う。

注記 εtは,“表14−I/Oキャラクタの生成タイミングの精度(受信モード)”で定義する。

8.2.1

T=0プロトコルのI/O送信タイミング

この試験の目的は,IFDによって送信されるデータのタイミングを測定することである。

8.2.1.1

試験装置

4.7.2に示す。

8.2.1.2

試験手順

IFDをIFD試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) ATRのパラメタNを254に設定することによって,IFDの最大保護時間を設定する(JIS X 6320-3の

8.3参照)。

b) IFDで試験シナリオを実行する。

c) 全ての実行可能なETU因子でa) からb) までを繰り返す。

d) 対応すべき全てのアプリケーションに対して,c) を繰り返す。JIS X 6320-3の6.3.1で定義したよう

にATR及び動作モード選択を変更することによってアプリケーションを選択する。

8.2.1.3

試験成績書

プロトコルの記録を試験成績書に記載する。

8.2.2

T=0プロトコルのI/Oキャラクタ再送

この試験の目的は,IFDによるキャラクタ再送の実行とタイミングとを測定することである(JIS X

6320-3の7.3及び10.2参照)。

8.2.2.1

試験装置

4.7.2に示す。

8.2.2.2

試験手順

36

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

IFDをIFD試験装置に接続する。

a) IFDで試験シナリオを実行する。

b) 次のc)〜f) の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な

内容だけでなく,全ての信号遷移(レベル及びタイミング)を記録する。

c) IFDから受信する各バイトに対して3回連続して最小時間の誤り状況を生成する。その条件とはJIS X

6320-3の7.3に従い,開始ビットの先端と誤り信号の先端との時間差を,規定された最小値[(10.5−

0.2) etu+εt]にして,最小期間(1 etu+εt)の誤り信号を送出することである。

d) IFDから受信される各バイトに対して3回連続して最大時間の誤り状況を生成する。その条件とはJIS

X 6320-3の7.3に従い,開始ビットの先端と誤り信号の先端との時間差を,規定された最大値[(10.5

+0.2) etu−εt]にして,最大期間(2 etu−εt)の誤り信号を送出することである。

e) 全てのサポートしているETU因子でc) からd) までを繰り返す。

f)

誤り信号を3回の代わりに5回連続としてe) を繰り返す。

この規格では,IFDが試験手順f) でICカード(IFD試験装置)を拒絶しなければならない。IFDは無限

に繰り返さないように,上記のように繰返し回数を3回又は5回に設定している。

注記 対応国際規格では8.2.2.3に記載があるが,試験手順に関する説明のため8.2.2.2に移動した。

8.2.2.3

試験成績書

プロトコルの記録を試験成績書に記載する。

8.2.3

T=0プロトコルのI/O受信タイミング及び誤り信号

この試験の目的は,IFDの受信タイミング及び誤り信号を測定することである(JIS X 6320-3の7.1,7.2,

7.3及び10.2参照)。

8.2.3.1

試験装置

4.7.2に示す。

8.2.3.2

試験手順

IFDをIFD試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) IFD試験装置に,表67に示すビットタイミングパラメタを設定する。

表67−IFD試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最大[tn = (n+0.2) etu−εt]

JIS X 6320-3の箇条7

連続する2キャラクタ間の遅延

960×255×(Fi / f)

JIS X 6320-3の箇条7

b) IFDで試験シナリオを実行する。

c) 各々のバイトで三つの連続するパリティ誤りを発生させる。

d) 全ての実行可能なETU因子でa) からc) までを繰り返す。

e) IFD試験装置に,表68に示すビットタイミングパラメタを設定する。

37

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

表68−IFD試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最小[tn = (n−0.2) etu+εt]

JIS X 6320-3の箇条7,8.3

連続する2キャラクタ間の遅延

12 etu+εt

JIS X 6320-3の箇条7,8.3

f)

b) からd) までを繰り返す。

g) 各バイトに対するパリティ誤りを3回の代わりに5回連続としてa) からf) までを繰り返す。

この規格では,IFDが試験手順f) でICカード(IFD試験装置)を拒絶しなければならない。IFDは無限

に繰り返さないように,上記のように繰返し回数を3回又は5回に設定している。

注記 対応国際規格では8.2.3.3に記載があるが,試験手順に関する説明のため8.2.3.2に移動した。

8.2.3.3

試験成績書

プロトコルの記録を試験成績書に記載する。

8.3

T=1プロトコル

IFDがT=1プロトコルをサポートしている場合だけ,次の試験を行う。

注記 この8.3の試験方法の記述は,図で示された試験シナリオを含んでいるものがある。これらの

シナリオは,IFD試験装置が,長さ36バイトであり,データとして“31 32 33 34 … 54”を含

む透過ファイルをもち,2バイト読出しのREAD BINARYコマンド[I(0,0) (INF =“00 B0 00 00

02”)]を実行可能としていることを想定している。

8.3.1

T=1プロトコルのI/O送信タイミング

この試験の目的は,IFDによって送信されるデータのタイミングを測定することである(JIS X 6320-3

の7.1,7.2,8.3及び11.4.3参照)。

8.3.1.1

試験装置

4.7.2に示す。

8.3.1.2

試験手順

IFDをIFD試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) IFDに,ATRのNを254(JIS X 6320-3の8.3参照)に設定した保護時間で代表的なプロトコルT=1

及びアプリケーション固有の通信を実行する。

b) Nを0に設定してa) を実行する。

c) Nを12に設定してa) を実行する。

d) 全てのサポートしているETU因子でa) からc) までを実行する。

e) Nを255に設定してa) 及びd) を実行する。

8.3.1.3

試験成績書

プロトコルの記録を試験成績書に記載する。

8.3.2

T=1プロトコルのI/O受信タイミング

この試験の目的は,T=1プロトコルのもとでIFDの受信タイミングを測定することである(JIS X 6320-3

の箇条7及び11.4.3参照)。

8.3.2.1

試験装置

4.7.2に示す。

38

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

8.3.2.2

試験手順

IFDをIFD試験装置に接続する。

次の試験の間,VCC端子,RST端子,CLK端子及びI/O端子を継続的に監視し,通信の論理的な内容だ

けでなく,全ての信号遷移(レベル及びタイミング)を記録する。

a) IFD試験装置に,表69に示すビットタイミングパラメタを設定する。

表69−IFD試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最大[tn = (n+0.2) etu−εt]

JIS X 6320-3の箇条7

ブロック応答時間(BRT)

最大

JIS X 6320-3の11.4.3

同一ブロック内の連続する2キャラ

クタ間の遅延

最大[(11+2CWI) etu−εt]

JIS X 6320-3の11.4.3

逆方向に送信する2キャラクタの先

端間の遅延

最大(11 etu+2BWI×960×372/f s−εt)

JIS X 6320-3の11.4.3

注記 ブロック応答時間は,受信したブロックの最終キャラクタの先端と,送信する次のブロックの最初のキャラ

クタの先端との間の時間として定義する。

b) IFDで代表的なプロトコルT=1及びアプリケーション固有の通信を実行する。

c) 全ての実行可能なETU因子でa) からb) までを繰り返す。

d) IFD試験装置に,表70に示すビットタイミングパラメタを設定する。

表70−IFD試験装置ビットタイミングパラメタ

パラメタ

値

参照

キャラクタフレーム長

最小[tn = (n−0.2) etu+εt]

JIS X 6320-3の箇条7

ブロック応答時間(BRT)

最小

JIS X 6320-3の11.4.3

同一ブロック内の連続する2キャラ

クタ間の遅延

最小(11 etu+εt)

JIS X 6320-3の11.4.3

逆方向に送信する2キャラクタの先

端間の遅延

最小(22 etu+εt)

JIS X 6320-3の11.4.3

注記 ブロック応答時間は,受信したブロックの最終キャラクタの先端と,送信する次のブロックの最初のキャラ

クタの先端との間の時間として定義される。

e) 少なくとも1秒の間,代表的なプロトコルT=1及びアプリケーション固有の通信を実行する。

f)

全ての実行可能なETU因子でd) からe) までを繰り返す。

8.3.2.3

試験成績書

プロトコルの記録を試験成績書に記載する。

8.3.3

IFDのキャラクタ待ち時間(CWT)動作

この試験の目的は,CWT以内のICカードの応答に対するIFDの応答を測定することである(JIS X 6320-3

の11.4.3参照)。

8.3.3.1

試験装置

4.7.2に示す。

8.3.3.2

試験手順

IFDをIFD試験装置に接続する。

39

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

a) IFDは,Iブロックを送信する。

b) Iブロックを構成する連続する2キャラクタの間の時間を測定する。

シナリオ12−IFDのキャラクタ待ち時間(CWT)動作

IFD

IFD試験装置

I(0,0) (INF a) =“00 B0 00 00 02”)

→

注a) コマンドを示すINFフィールドはREAD BINARY,2バイトである。

8.3.3.3

試験成績書

試験手順b) で得られたIFD応答のタイミングを試験成績書に記載する。

8.3.4

キャラクタ待ち時間(CWT)を超えたICカードに対するIFD動作

この試験の目的は,CWTを超えたICカードに対するIFDの動作を測定することである(JIS X 6320-3

の11.4.3参照)。

8.3.4.1

試験装置

4.7.2に示す。

8.3.4.2

試験手順

IFDをIFD試験装置に接続する。

a) IFDは,IFD試験装置へIブロックを送信する。IFD試験装置は,全長nバイトのブロックに対し,IFD

へnバイト未満を送信する。

b) IFD応答の有無,内容,及びそのタイミングを記録する。

注記 中断に起因して発生する衝突でのIFDの動作は,調査することが望ましい。

シナリオ13−CWTを超えたICカードへのIFD応答

IFD

IFD試験装置

I(0,0) (INF a) =“00 B0 00 00 02”)

→

←

I(0,0)(不完全なINF)

IFD応答

→

注a) コマンドを示すINFフィールドはREAD BINARY,2バイトである。

8.3.4.3

試験成績書

応答の有無,内容及びIFD応答のタイミングを試験成績書に記載する。

8.3.5

ブロック保護時間(BGT)

この試験の目的は,IFD試験装置が送信したブロックの最終キャラクタの先端からIFDが送信する次の

ブロックの最初のキャラクタの先端までの間隔(JIS X 6320-3の11.4.3参照)を測定することである。

8.3.5.1

試験装置

4.7.2に示す。

8.3.5.2

試験手順

IFDをIFD試験装置に接続する。

a) IFDは,Iブロックを送信する。

b) IFD試験装置は,否定応答Rブロックを送信する。

c) IFDは,前回送ったIブロックを再送する。

40

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

d) Rブロックの最終キャラクタの先端と,2番目のIブロックの最初のキャラクタの先端との間の時間を

測定し記録する。

シナリオ14−ブロック保護時間(BGT)

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

R(0) (PCB =“81”)

I(0,0) (INF =“00 B0 00 00 02”)

→

8.3.5.3

試験成績書

試験手順d) で得られた時間を試験成績書に記載する。

8.3.6

IFDによるブロックシーケンス

この試験の目的は,送信誤りに対するIFDの動作を測定することである(JIS X 6320-3の11.6.3参照)。

8.3.6.1

試験装置

4.7.2に示す。

8.3.6.2

試験手順

IFDをIFD試験装置に接続する。

8.3.6.2.1

試験手順1(JIS X 6320-3の11.6.3.2,規則7.1,JIS X 6320-3の附属書A シナリオ9)

a) IFD試験装置のプロトコルを初期化する。

b) IFDは,IFD試験装置へブロックI(0,0)を送信する。

c) IFD試験装置は,IFDへ無効ブロックを送信する。

シナリオ15−IFDによるブロックシーケンス,試験手順1

(JIS X 6320-3の11.6.3.2,規則7.1,JIS X 6320-3の附属書Aシナリオ9)

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (EDC誤り)

IFD応答

→

d) IFDの応答を記録する。

8.3.6.2.2

試験手順2(JIS X 6320-3の11.6.3.2,規則7.4.2)

a) IFD試験装置のプロトコルを初期化する。

b) IFDは,IFD試験装置へブロックI(0,0)を送信する。

c) IFD試験装置は,IFDへ無効ブロックを送信する。

d) IFD試験装置は,IFDの応答を待ち,それからIFDへ2番目の無効ブロックを送信する。

e) IFDの応答を記録する。

f)

IFDがPCB=“81”のRブロックを応答した場合,IFD試験装置はIFDへ3番目の無効ブロックを送

信する。IFDがPCB=“81”のRブロックを応答しない場合,試験条件に対する応答を評価し,試験

を終える。

g) IFDの応答を記録する。

41

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

シナリオ16−IFDによるブロックシーケンス試験手順2(JIS X 6320-3の11.6.3.2,規則7.4.2)

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0) (EDC誤り)

R(0) (PCB =“81”)

→

←

I(0,0) (EDC誤り)

R(0) (PCB =“81”)

→

←

I(0,0) (EDC誤り) a)

IFD応答

→

注a) IFDは3回試みる前に,再同期又はICカードのリセットを行ってもよい。

8.3.6.2.3

試験手順3(ブロック連鎖)(JIS X 6320-3の11.6.3.2,規則7.1及びJIS X 6320-3の11.6.2.3,規

則5)

a) IFD試験装置のプロトコルを初期化する。

b) IFDは,IFD試験装置がサポートしているコマンドを含むINFをもつブロックI(0,0)をIFD試験装置

に送信する。

c) IFD試験装置は,ブロック連鎖の1番目のブロックをブロックI(0,1)で送信し,IFD応答を待つ。

d) IFD試験装置は,IFDへ無効ブロックを送信する。

e) IFDの応答を記録する。

f)

応答を規則7.1で評価する。試験基準を満たさない場合は,試験を終了する。試験基準を満たす場合,

IFD試験装置はブロック連鎖の2番目のブロックを誤りなく送信する。

g) IFDの応答を記録する。

シナリオ17−IFDによるブロックシーケンス試験手順3(ブロック連鎖)

(JIS X 6320-3の11.6.3.2,規則7.1及びJIS X 6320-3の11.6.2.3,規則5)

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 24”)

→

←

I(0,1) (INF =“31 32 .. 50”)

R(1) (PCB =“90”)

→

←

I(1,0) (EDC誤り)

R(1) (PCB =“91”)

→

←

I(1,0) (INF =“51 52 53 54 90 00”)

I(1,0) (INF =“00 B0 00 00 24”)

→

8.3.6.2.4

試験手順4(JIS X 6320-3の11.6.3.2,規則7.4.2,JIS X 6320-3の附属書Aシナリオ34)

a) 正しいATRシーケンスの後にIFD試験装置を無応答状態にする。

b) IFDは,IFD試験装置へIブロックを送信する。

c) 少なくとも三つの連続するBWT期間,IFDからの全ての応答を記録する。

42

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

シナリオ18−IFDによるブロックシーケンス試験手順4

(JIS X 6320-3の11.6.3.2,規則7.4.2,JIS X 6320-3の附属書Aシナリオ34)

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

無応答

R(0) (PCB =“81”),R(0) (PCB =“82”)又は初期化

→

←

無応答

R(0) (PCB =“81”),R(0) (PCB =“82”)又は初期化

→

←

無応答

IFD応答

→

8.3.6.2.5

試験成績書

各試験手順におけるIFDの応答を試験成績書に記載する。

8.3.7

IFDによる送信誤りの回復

この試験の目的は,IFDが基本規格(JIS X 6320-3参照)に従って否定応答に対する動作を確認するこ

とである。

8.3.7.1

試験装置

4.7.2に示す。

8.3.7.2

試験手順

a) IFDからIブロックを送信する。

b) 否定応答Rブロックを送信する。

c) IFDの動作を記録する。

シナリオ19−IFDによる送信誤りの復帰

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

R(0) (PCB =“81”)

IFD応答

→

8.3.7.3

試験成績書

IFDの動作を試験成績書に記載する。

8.3.8

IFSC調整

この試験の目的は,IFSC調整(JIS X 6320-3参照)を確認することである。

8.3.8.1

試験装置

4.7.2に示す。

8.3.8.2

試験手順

IFDをIFD試験装置に接続する。

a) IFD試験装置を初期化する。

b) IFDがサポートしているコマンドを含むINF及びIFD試験装置が実行可能なコマンドで,各々の方向

で一つのIブロックを交換する。

c) IFDへブロックS(IFS request)を送信する。

43

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

シナリオ19A−IFSC調整

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

I(0,0)

I(1,0)

→

←

S(IFS request)

IFD応答

→

d) IFDの動作を記録する。

8.3.8.3

試験成績書

IFDの動作を試験成績書に記載する。

8.3.9

ICカードによるブロック連鎖打切り

この試験の目的は,ブロック連鎖打切り(JIS X 6320-3参照)を確認することである。

8.3.9.1

試験装置

4.7.2に示す。

8.3.9.2

試験手順

IFDをIFD試験装置に接続する。

a) IFD試験装置を初期化する。

b) IFDは,IFD試験装置のエミュレータがサポートしているコマンド(オフセットなしで36バイト読む

READ BINARYコマンド,JIS X 6320-4参照)を含むINFで,IFD試験装置へIブロックを送信する。

c) IFD試験装置は,ブロック連鎖の1番目のブロックI(0,1)を送信する。IFDはR(1)で応答しなければ

ならない。

d) IFDへ打切り要求を送信する。

シナリオ20−ICカードによるブロック連鎖打切り

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 24”)

→

←

I(0,1) (INF =“31 32 .. 50”)

R(1) (PCB =“90”)

→

←

S(ABORT request)

IFD応答

→

e) IFDの応答の有無及びその内容を記録する。

8.3.9.3

試験成績書

IFDの応答の有無及びその内容を試験成績書に記載する。

8.4

不正なPCBに対するIFDの応答

この試験の目的は,不正なPCBに対するIFDの動作を分析することである(JIS X 6320-3の11.6.3.1参

照)。

8.4.1

試験装置

4.7.2に示す。

8.4.2

試験手順

a) IFD試験装置を初期化する。

44

X 6305-3:2012 (ISO/IEC 10373-3:2010)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

b) IFDは,IFD試験装置がサポートしているコマンド(オフセットなしで2バイトを読み出すREAD

BINARYコマンド,JIS X 6320-4参照)を含むINFでIFD試験装置にブロックI(0,0)を送る。

c) 不正なPCB(未定義の符号化)をもつ誤りを含むブロックをIFDに送る。ただし,このブロックのパ

リティ及びEDCは正しい値である。

シナリオ21−IFDの不正なPCBに対する動作

IFD

IFD試験装置

I(0,0) (INF =“00 B0 00 00 02”)

→

←

PCB=“FF”をもつブロック

IFD応答

→

d) IFDからの応答の有無及び内容を記録する。

8.4.3

試験成績書

IFDからの応答の有無及び内容を試験成績書に記載する。

参考文献 JIS X 6305-1 識別カードの試験方法−第1部:一般的特性

JIS X 6320-2 識別カード−ICカード−第2部:外部端子付きICカードの端子の寸法及び位置