C 61280-2-3:2013 (IEC 61280-2-3:2009)

(1)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

目 次

ページ

序文 ··································································································································· 1

1 適用範囲························································································································· 1

2 引用規格························································································································· 1

3 用語及び定義 ··················································································································· 1

4 一般事項························································································································· 5

4.1 ジッタ発生 ··················································································································· 5

4.2 信号品質へのジッタの影響 ······························································································ 6

4.3 ジッタ耐力 ··················································································································· 6

4.4 待機時間ジッタ ············································································································· 7

4.5 ワンダ ························································································································· 7

5 ジッタテスト手順 ············································································································· 8

5.1 ジッタ測定方式 ············································································································· 8

5.2 共通試験装置 ················································································································ 9

5.3 安全 ··························································································································· 10

5.4 光ファイバ接続 ············································································································ 10

5.5 測定サンプル ··············································································································· 11

6 ジッタ耐力の測定 ············································································································ 11

6.1 目的 ··························································································································· 11

6.2 使用する機器 ··············································································································· 11

6.3 ビット誤り率ペナルティ法 ····························································································· 11

6.4 エラー発生法 ··············································································································· 12

6.5 ジッタ耐力及びストレスアイ受信試験の測定 ······································································ 13

7 ジッタ伝達関数の測定 ······································································································ 15

7.1 一般事項 ····················································································································· 15

7.2 使用する機器 ··············································································································· 15

7.3 基礎技術 ····················································································································· 16

7.4 アナログ位相検出法 ······································································································ 16

8 出力ジッタの測定 ············································································································ 18

8.1 一般事項 ····················································································································· 18

8.2 機器の接続 ·················································································································· 18

9 システマティックジッタの測定 ·························································································· 19

9.1 使用する機器 ··············································································································· 19

9.2 基礎技術 ····················································································································· 19

10 BERTスキャン法の測定 ································································································· 21

10.1 一般事項 ···················································································································· 21

C 61280-2-3:2013 (IEC 61280-2-3:2009) 目次

(2)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ページ

10.2 使用する機器 ·············································································································· 22

10.3 基礎技術 ···················································································································· 22

11 ジッタ分離手法の測定 ···································································································· 23

11.1 一般事項 ···················································································································· 23

11.2 使用する機器 ·············································································································· 24

11.3 機器の接続 ················································································································· 25

11.4 機器設定 ···················································································································· 25

11.5 測定手順 ···················································································································· 25

12 ワンダの測定 ················································································································ 26

12.1 使用する機器 ·············································································································· 26

12.2 基礎技術 ···················································································································· 27

13 ワンダTDEV耐力の測定 ································································································ 28

13.1 目的 ·························································································································· 28

13.2 使用する機器 ·············································································································· 28

13.3 基礎技術 ···················································································································· 28

13.4 機器の接続 ················································································································· 28

13.5 機器設定 ···················································································································· 30

13.6 測定手順 ···················································································································· 30

14 ワンダTDEV伝達の測定 ································································································ 30

14.1 使用する機器 ·············································································································· 30

14.2 機器の接続 ················································································································· 30

14.3 機器設定 ···················································································································· 31

14.4 測定手順 ···················································································································· 31

15 試験結果 ······················································································································ 32

15.1 必須情報 ···················································································································· 32

15.2 有益な情報 ················································································································· 32

C 61280-2-3:2013 (IEC 61280-2-3:2009)

(3)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

まえがき

この規格は,工業標準化法第12条第1項の規定に基づき,一般財団法人光産業技術振興協会(OITDA)

及び一般財団法人日本規格協会(JSA)から,工業標準原案を具して日本工業規格を制定すべきとの申出

があり,日本工業標準調査会の審議を経て,経済産業大臣が制定した日本工業規格である。

この規格は,著作権法で保護対象となっている著作物である。

この規格の一部が,特許権,出願公開後の特許出願又は実用新案権に抵触する可能性があることに注意

を喚起する。経済産業大臣及び日本工業標準調査会は,このような特許権,出願公開後の特許出願及び実

用新案権に関わる確認について,責任はもたない。

JIS C 61280の規格群には,次に示す部編成がある。

JIS C 61280-1-3 中心波長及びスペクトル幅測定

JIS C 61280-2-1 受信感度及びオーバロード測定

JIS C 61280-2-2 光アイパターン,光波形及び消光比測定

JIS C 61280-2-3 ジッタ及びワンダ測定

JIS C 61280-2-8 Q値測定を用いた低ビット誤り率の決定法

JIS C 61280-2-9 高密度波長分割多重システムの光信号対雑音比測定

JIS C 61280-2-10 レーザ送信器の時間分解チャープ及びアルファファクタ測定

JIS C 61280-2-11 光信号品質評価のための強度ヒストグラム評価を用いた平均化Q値測定

また,これらの規格群の通則として,次の規格がある。

JIS C 61281-1 光ファイバ通信サブシステム通則

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

日本工業規格 JIS

C 61280-2-3:2013

(IEC 61280-2-3:2009)

光ファイバ通信サブシステム試験方法ー

第2-3部:ジッタ及びワンダ測定

Fibre optic communication subsystem test procedures-

Part 2-3: Digital systems-Jitter and wander measurements

序文

この規格は,2009年に第1版として発行されたIEC 61280-2-3を基に,技術的内容及び構成を変更する

ことなく作成した日本工業規格である。

なお,この規格で点線の下線を施してある参考事項は,対応国際規格にはない事項である。

1

適用範囲

この規格は,デジタル信号の伝送及び処理に適用できるジッタパラメータの測定方法(箇条5〜箇条11)

及びワンダパラメータの測定方法(箇条12〜箇条14)について規定する。

注記 この規格の対応国際規格及びその対応の程度を表す記号を,次に示す。

IEC 61280-2-3:2009,Fibre optic communication subsystem test procedures−Part 2-3: Digital systems

−Jitter and wander measurements(IDT)

なお,対応の程度を表す記号“IDT”は,ISO/IEC Guide 21-1に基づき,“一致している”こ

とを示す。

2

引用規格

次に掲げる規格は,この規格に引用されることによって,この規格の規定の一部を構成する。これらの

引用規格は,その最新版(追補を含む。)を適用する。

JIS C 6802 レーザ製品の安全基準

注記 対応国際規格:IEC 60825-1,Safety of laser products−Part 1: Equipment classification and

requirements(IDT)

ITU-T Recommendation G.813,Timing characteristics of SDH equipment slave clocks (SEC)

ITU-T Recommendation G.8251,The control of jitter and wander within the optical transport network (OTN)

3

用語及び定義

この規格で用いる主な用語及び定義は,次による。

3.1

ジッタ(jitter)

デジタル信号の理想的な時間位置からの短期的で,かつ,非累積の時間変動。短期的な時間変動とは,

繰返し周波数が10 Hz以上のジッタ成分である。

2

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.2

ジッタ振幅(jitter amplitude)

デジタル信号の理想的な時間位置からの瞬時変動。この規格では,ジッタ振幅を単位間隔(UI)で表す。

ジッタ振幅は,時間単位で表す場合もある。

3.3

単位間隔[unit interval (UI)]

理想的な時間位置における事象間の最小間隔。実際には,この単位間隔は,デジタル信号の理想的なタ

イミング周期と等しい。

3.4

ジッタ周波数(jitter frequency)

理想的な時間位置に対するデジタル信号の繰返し変動時間。単位は,ヘルツ(Hz)で表す。

3.5

ジッタ帯域幅(jitter bandwidth)

ジッタ振幅がその最大値に対して3 dB減衰するときのジッタ周波数。

3.6

アライメントジッタ(alignment jitter)

データ信号のタイミングを信号から抽出するときに生じるジッタ。

3.7

タイミングジッタ(timing jitter)

タイミング源に存在するジッタ。

3.8

システマティックジッタ(systematic jitter)

不規則でなく発生周期をもつジッタ成分。デジタル信号に含まれるシステマティックジッタは,フレー

ムアライメントデータ及びスタッフ同期制御データのようなデジタル信号の定期的に繰り返す特性によっ

て生じる。このジッタは,確定ジッタにも分類され,周期性無相関ジッタ及びデータ依存性ジッタから成

る。

3.9

周期性無相関ジッタ(periodic uncorrelated jitter)

周期的に発生するシステマティックジッタの一種で,かつ,データパターンが繰り返す場合でもデータ

と相関関係のないジッタ。周期性無相関ジッタは,パターンエッジの観測に関連しない。スイッチング電

源,位相変調のかかった基準クロック又はデータレートを決定するクロックのいかなる周期的な位相変調

も,周期性無相関ジッタの発生源となる。

3.10

符号間干渉ジッタ(inter-symbol interference jitter)

伝送路の帯域幅が狭いために発生するジッタ。帯域幅が狭い場合,異なる論理レベルに至らず,信号レ

ベルの変化が十分な振幅とならないことがある。論理の中間点に近いレベルから信号変遷が始まる場合,

完全な振幅まで到達している連続した同一ビット列に比べて早く論理が切り変わる。

3.11

デューティサイクルひずみ(duty cycle distortion)

論理1(0-1-0)の持続時間と論理0(1-0-1)の持続時間とが異なる場合に起きるひずみ。例えば,論理1の持

3

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

続時間が長い場合,立ち上がりエッジは,立ち下がりエッジと比べ,理想的な時間位置より早くなる。

3.12

データ依存性ジッタ(data dependent jitter)

周期性データパターンの特定のビットに関連するジッタ。このジッタは,データパターンが繰り返され

るとき,データエッジに繰り返し現れ,デューティサイクルひずみ及び/又は符号間干渉によって生じる。

3.13

待機時間ジッタ(waiting time jitter)

非同期の多重化方式で発生し,スタッフ同期の要求とその実行との間の遅延が変動することによって生

じるジッタ。

3.14

ジッタ耐力(jitter tolerance)

ジッタ付加によって特定のペナルティ又は特定の誤りを起こさずに受信できる最大ジッタ振幅値。最大

ジッタ耐力振幅は,ジッタ周波数に依存する。

3.15

ジッタ発生(jitter generation)

データ信号にジッタ障害が付加される過程。

3.16

入力ジッタ(input jitter)

ハイアラーキインタフェース又は装置若しくはデバイスの入力端子に発生するジッタ。

3.17

出力ジッタ(output jitter)

ハイアラーキインタフェース又は装置若しくはデバイスの出力端子に発生するジッタ。

3.18

ジッタ伝達(jitter transfer)

装置又はデバイスの入力から出力に伝達されるジッタ量。ジッタ伝達は,通常,入力ジッタに対する出

力ジッタの比率をデシベル(dB)で表す。

3.19

トータルジッタ(total jitter)

確定ジッタとランダムジッタとの合計。トータルジッタは,ピーク値で表す。

注記 確定ジッタは,データ又はクロックに依存して受信信号の波形タイミングが変化するジッタ。

このジッタは,アライメントジッタ,タイミングジッタ,システマティックジッタ,周期性無

相関ジッタ,符号間干渉ジッタ,デューティサイクルひずみ,データ依存性ジッタ,待機時間

ジッタなどの総称である。

ランダムジッタは,不規則なジッタ。このジッタは,デバイスが本来もっている特性,熱雑

音などが影響して,自然誘発的に起こるジッタである。

3.20

ジッタバスタブ曲線(jitter bathtub curve)

ビット誤り率を,ビット誤り検出のサンプリングポイントの時間位置の関数として表示する曲線。この

曲線は,データエッジが単位間隔内での特定位置に誤って存在する確率を表す。

4

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.21

ワンダ(wander)

デジタル信号の理想的な位置からの長期的な非累積の時間変動。長期的な時間変動とは,繰返し周波数

が,10 Hz未満のジッタ成分をいう。ワンダ振幅は時間単位(s)で表すが,単位間隔(UI)で表す場合も

ある。

3.22

タイムインターバルエラー,TIE(time interval error)

被測定クロックと基準クロックとの間のそれぞれの時間間隔の測定の差。TIE(t;τ)は,式(1)によって表す。

(

)

[

][

]

)

(

)

(

)

(

)

(

)

(

)

;(

t

x

t

x

t

Tref

t

Tref

t

T

t

T

t

TIE

−

+

=

−

+

−

−

+

=

τ

τ

τ

τ

··············· (1)

ここに,

τ: 観測間隔

T(t): 絶対時間のサンプル

Tref(t): 絶対時間のサンプルの初期値

x(t): 時間誤差のサンプル

3.23

最大タイムインターバルエラー,MTIE(maximum time interval error)

測定期間(T)における観測時間間隔(τ=nτ0)での理想的なタイミング信号と被測定タイミング信号と

の間の最大のピーク変動。MTIE(nτ0)は,式(2)によって表す。

−

≅

+

+

−

i

n

k

i

k

i

n

k

i

k

n

N

k

x

x

n

MTIE

≦

≦

≦

≦

≦

≦

min

max

max

)

(

1

0τ

n=1,2,…,N−1 ·················· (2)

ここに,

xi: 時間誤差のサンプル

N: サンプルの総数

τ0: 時間誤差のサンプル間隔

n: 測定期間(T)中のサンプル間隔数

3.24

タイムデビエーション,TDEV,σx(time deviation)

積分時間(τ=nτ0)の関数として表され,信号に見込まれる時間変動の尺度。TDEVは,被測定信号の位

相(又は時間)ノイズのスペクトル成分の情報を含んでいる。TDEVは,時間単位(s)で表す。時間誤差

のサンプルのシーケンスに基づいて,TDEV(nτ0)は式(3)によって表す。

(

)

(

)

2

1

2

1

3

1

2

0

2

)1

3

(

6

1

+

−

+

−

≅

∑

∑

−

+

=

+

+

+

−

=

j

n

j

i

i

n

i

n

i

n

N

j

x

x

x

n

N

n

n

TDEVτ

とする。)

を超えない最大の整数

は

(ただし,

3

,

,2,1

N

M

M

n

Λ

=

··········· (3)

ここに,

xi: 時間誤差のサンプル

N: サンプルの総数

τ0: 時間誤差のサンプル間隔

τ: TDEVの独立変数である積分時間

n: 積分時間τ中のサンプル間隔数

3.25

ビット誤り率,BER(bit error ratio)

総受信ビット数に対するエラービット数の比率。

5

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

3.26

エラー秒(errored second)

データストリームに1個以上のデジタルエラーを含む1 s当たりの総エラー時間。

4

一般事項

4.1

ジッタ発生

4.1.0A

一般

デジタル信号のジッタは,次に示す三つの基本プロセスによって発生する。ジッタ発生プロセスの数理

解析は複雑であるため,この規格の対象外とする。ジッタ発生プロセスの包括的解析及び初期の数理解析

は,参考文献[1]を参照する。

4.1.1

タイミングジッタ

タイミングジッタは,データタイミングクロックに起因するジッタ障害である。最も安定したタイミン

グ源でさえ,ある程度のジッタ又は意図していない位相変調若しくは位相ノイズを含んでいる。主要なタ

イミング発生器では,この障害は極めて小さいが,タイミング信号がシステムに分配されるときに増加す

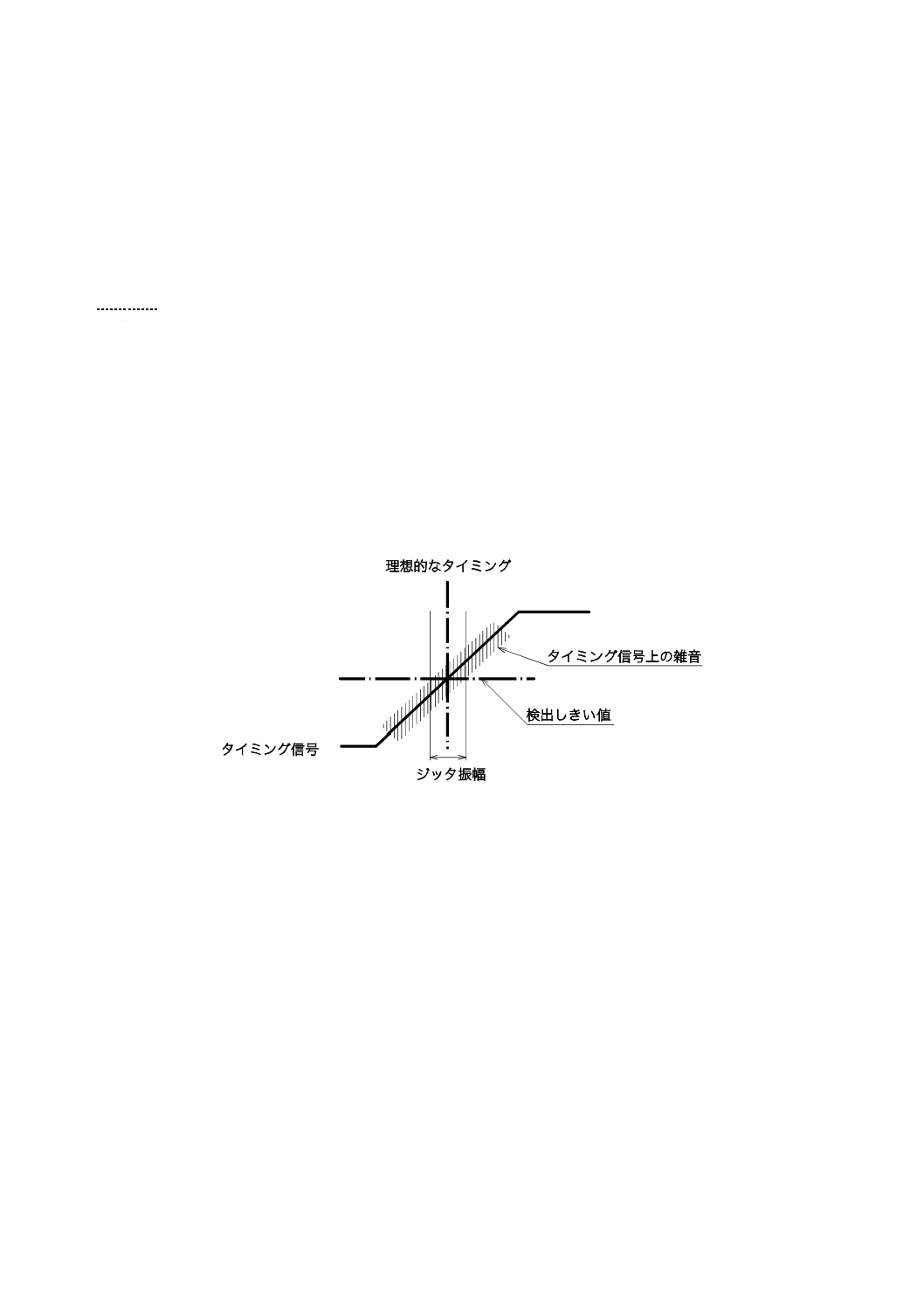

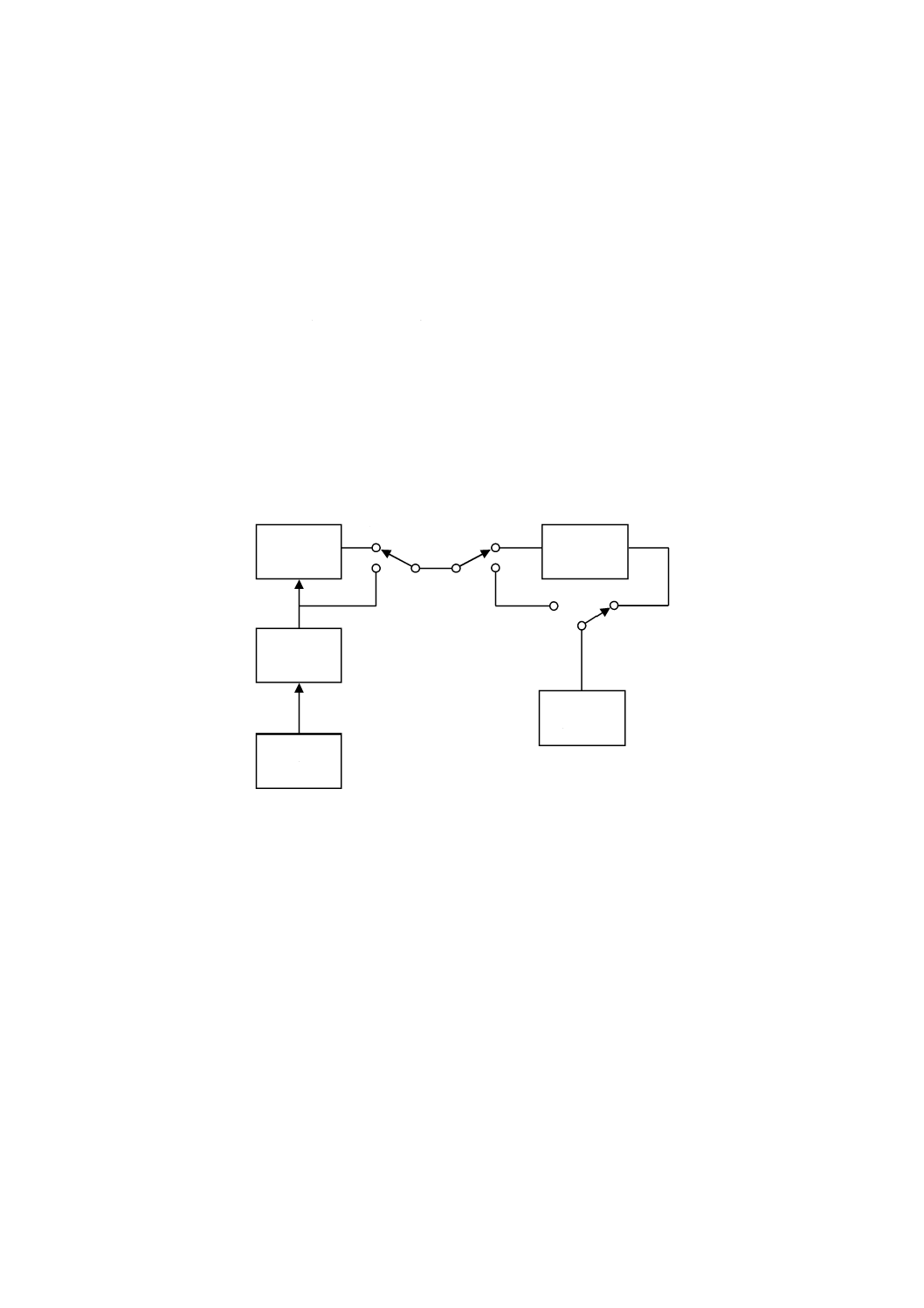

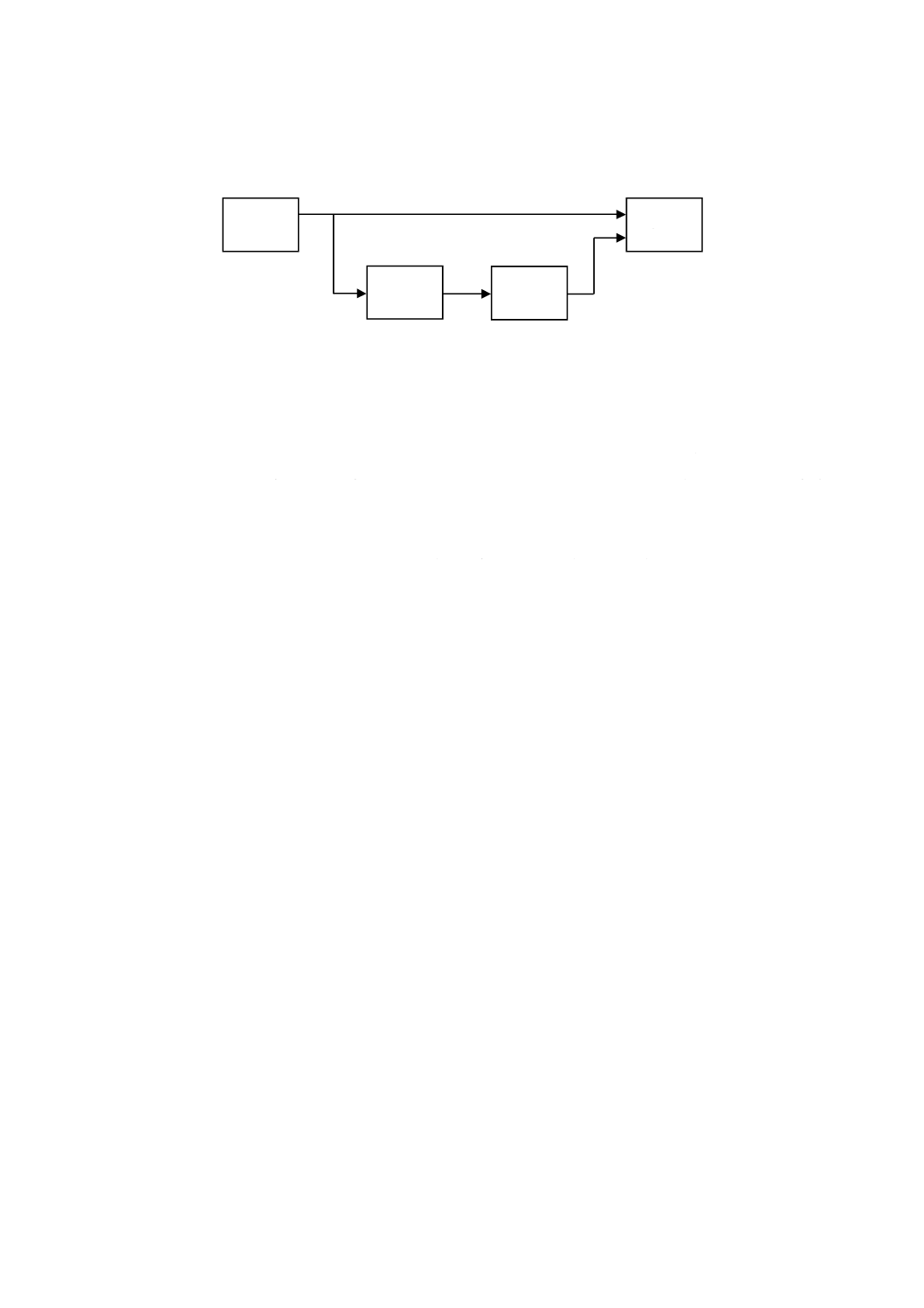

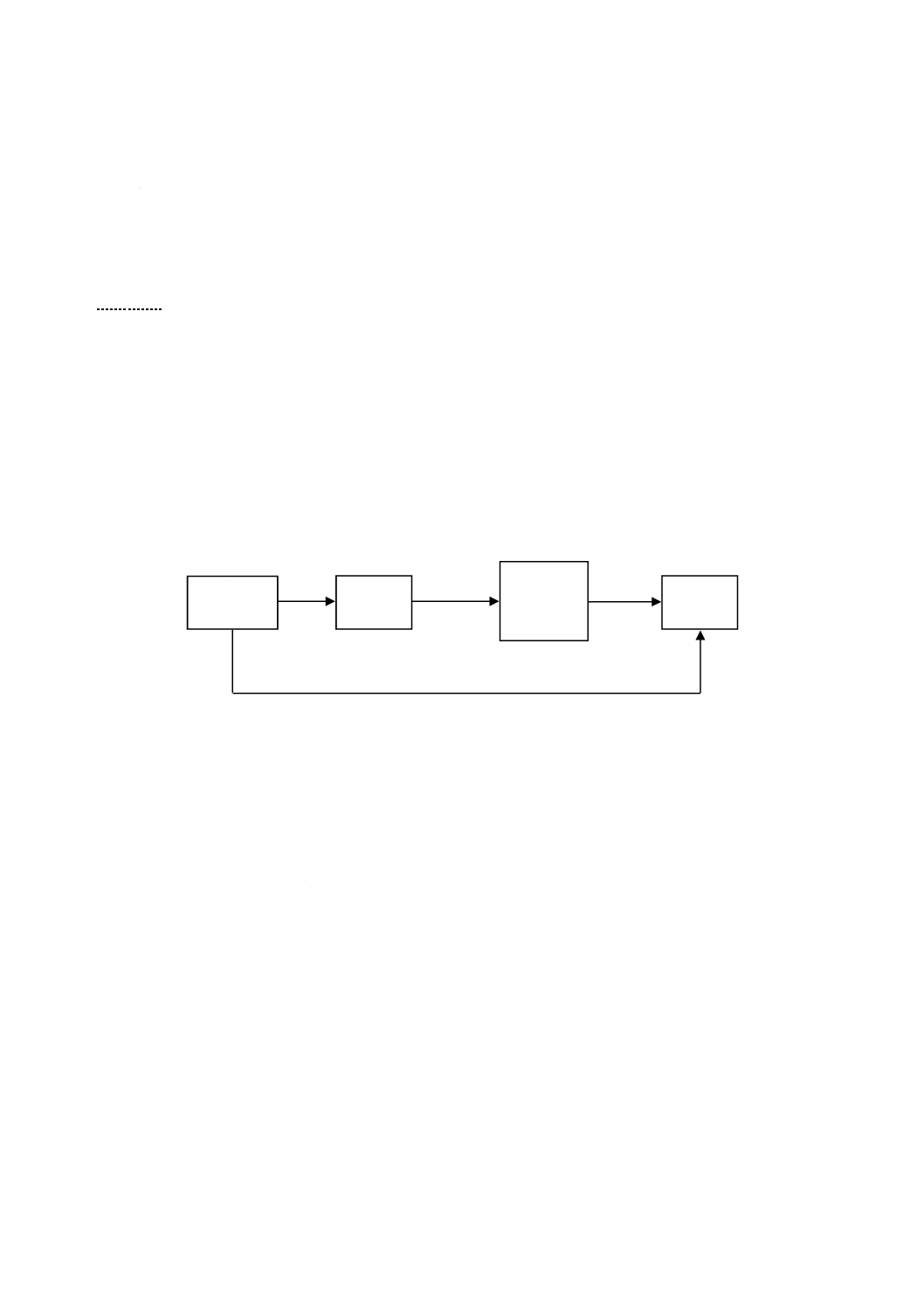

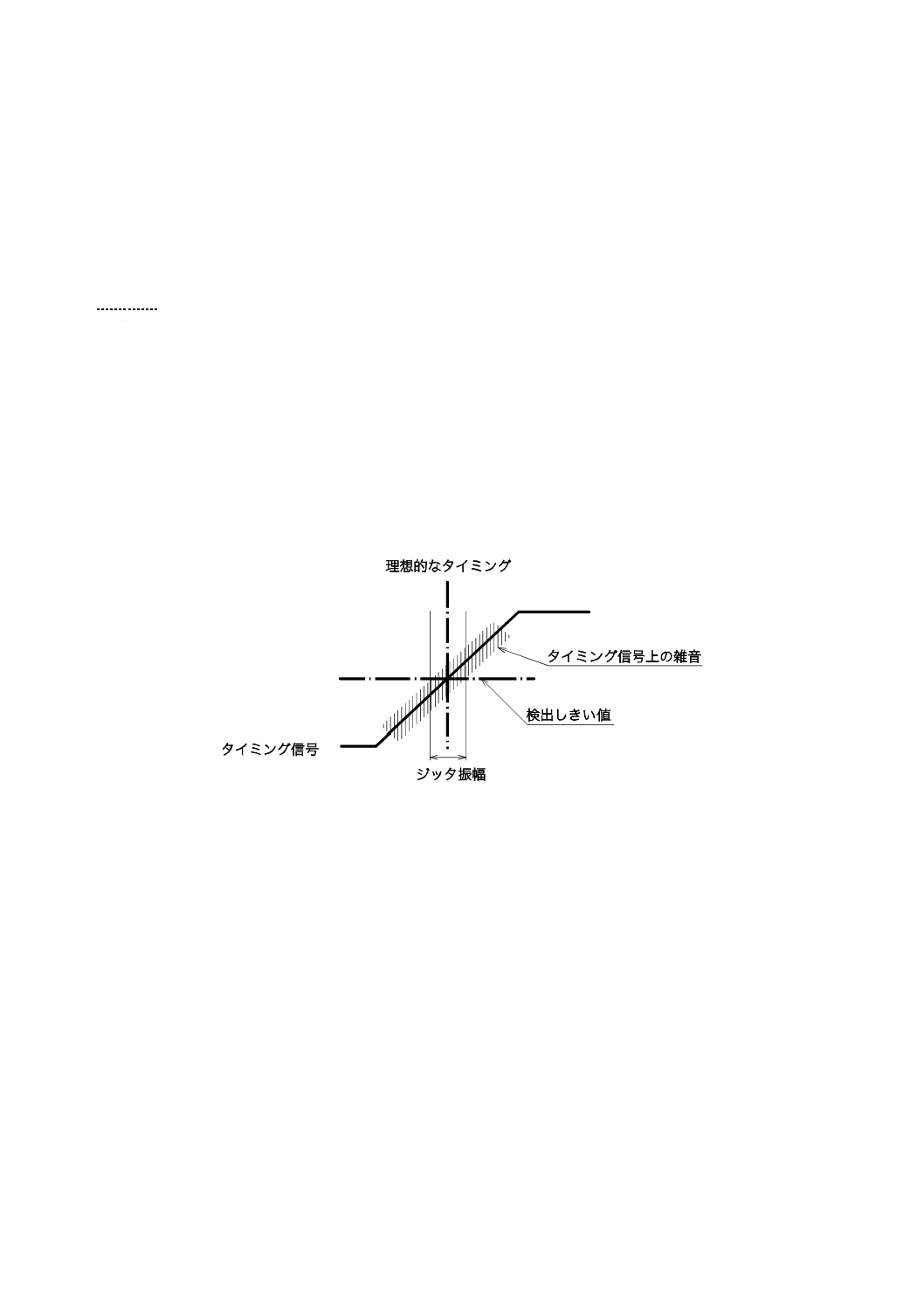

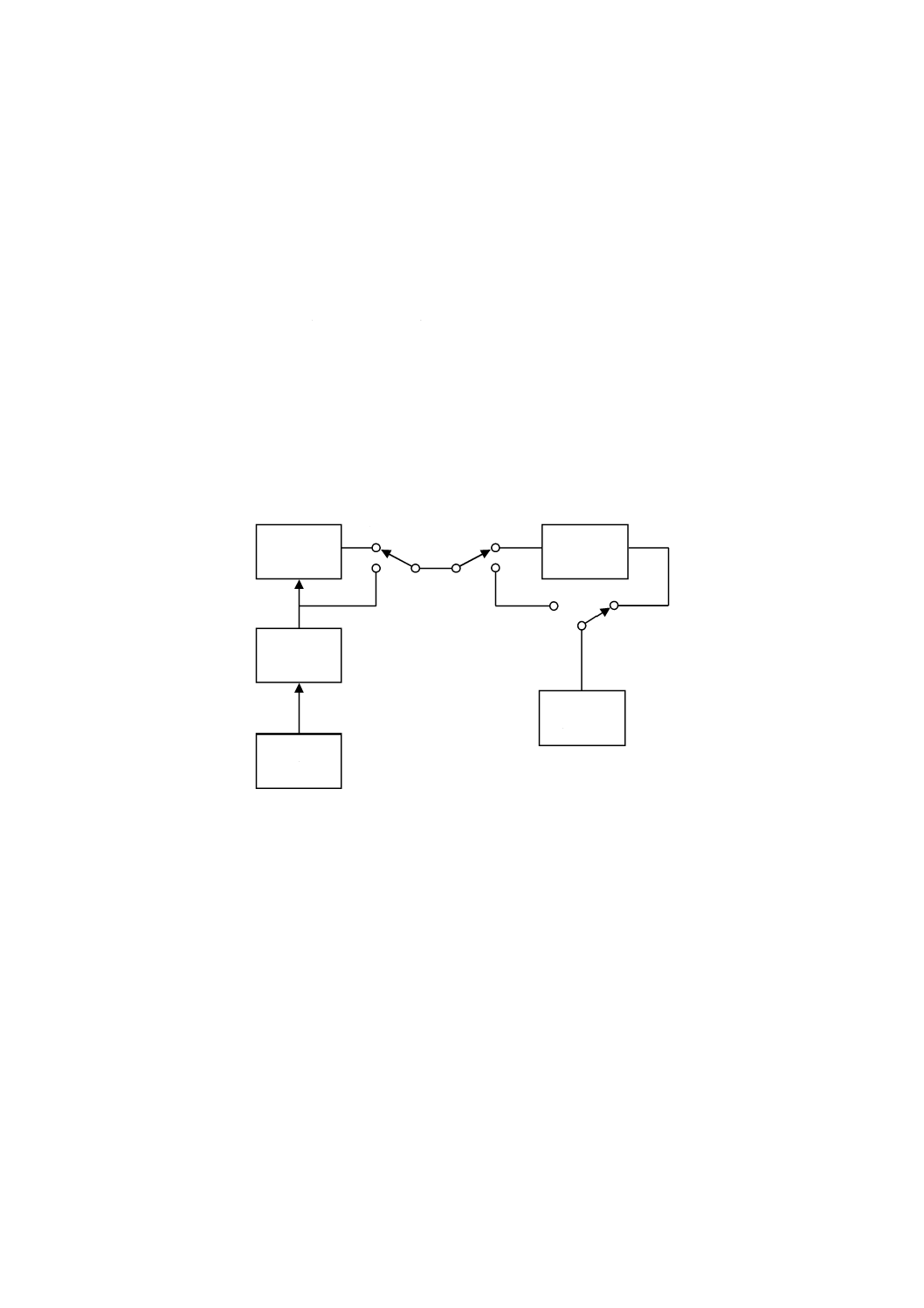

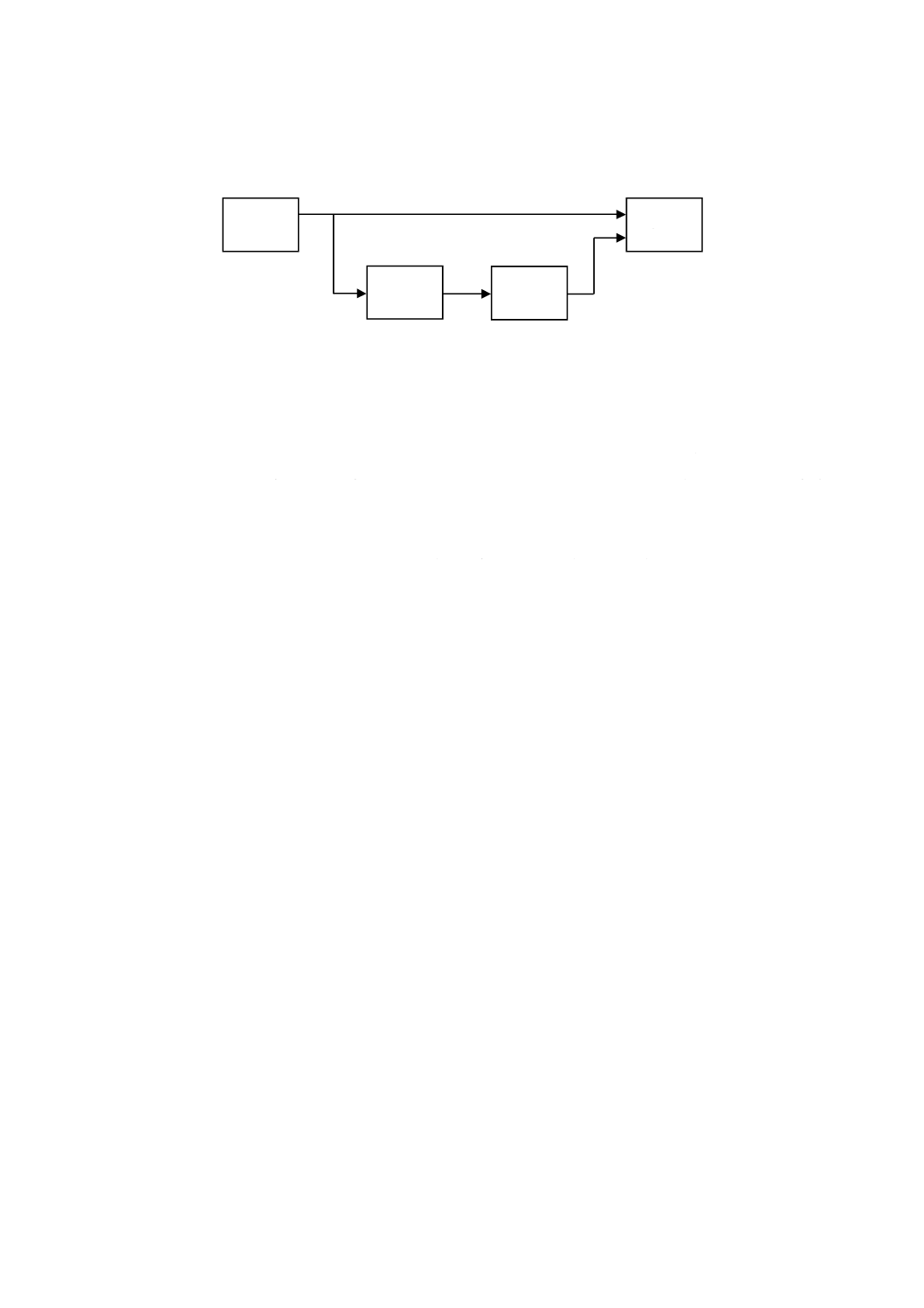

る。デジタルシステムのタイミング信号へのノイズの影響を,図1に誇張して示す。

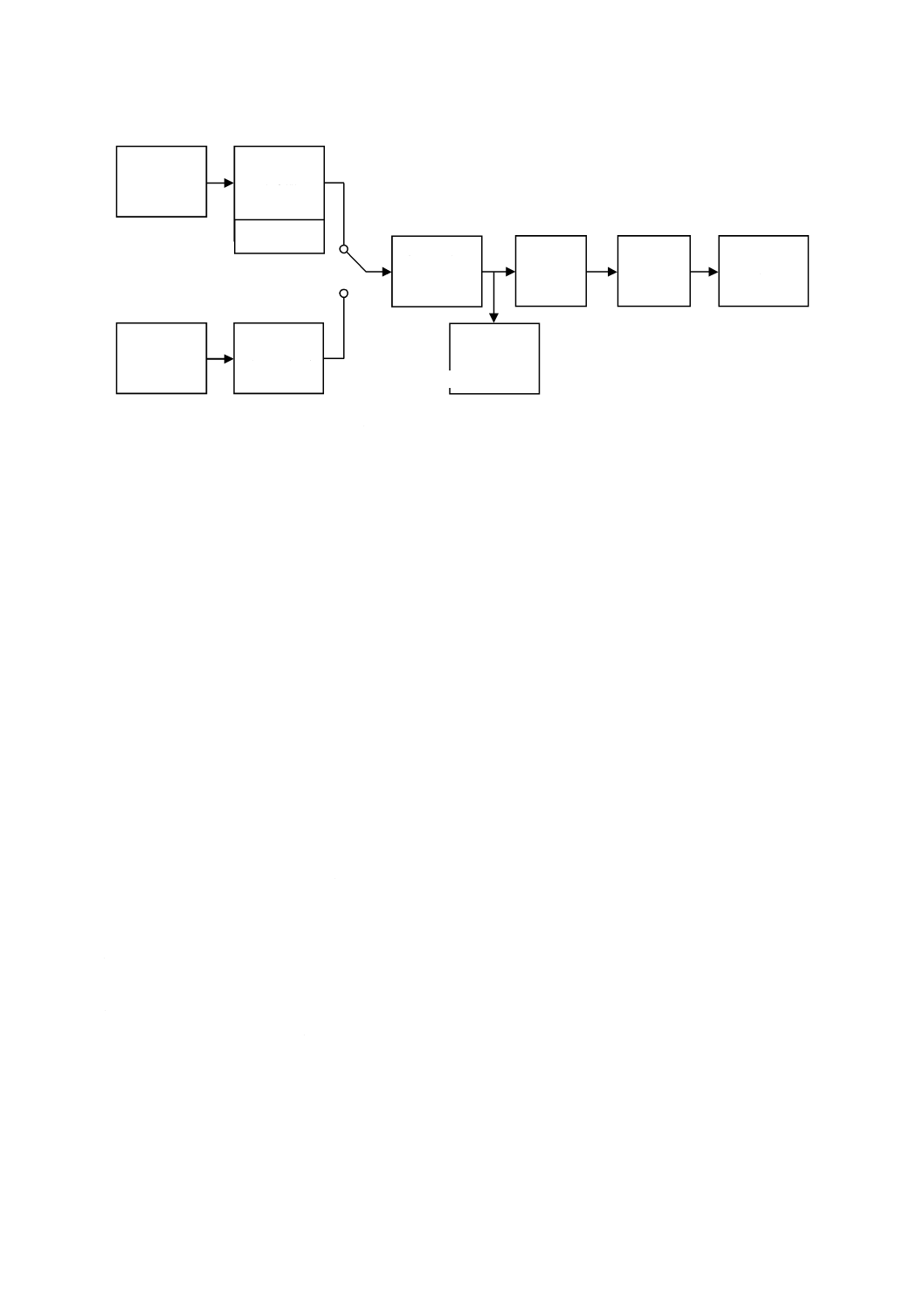

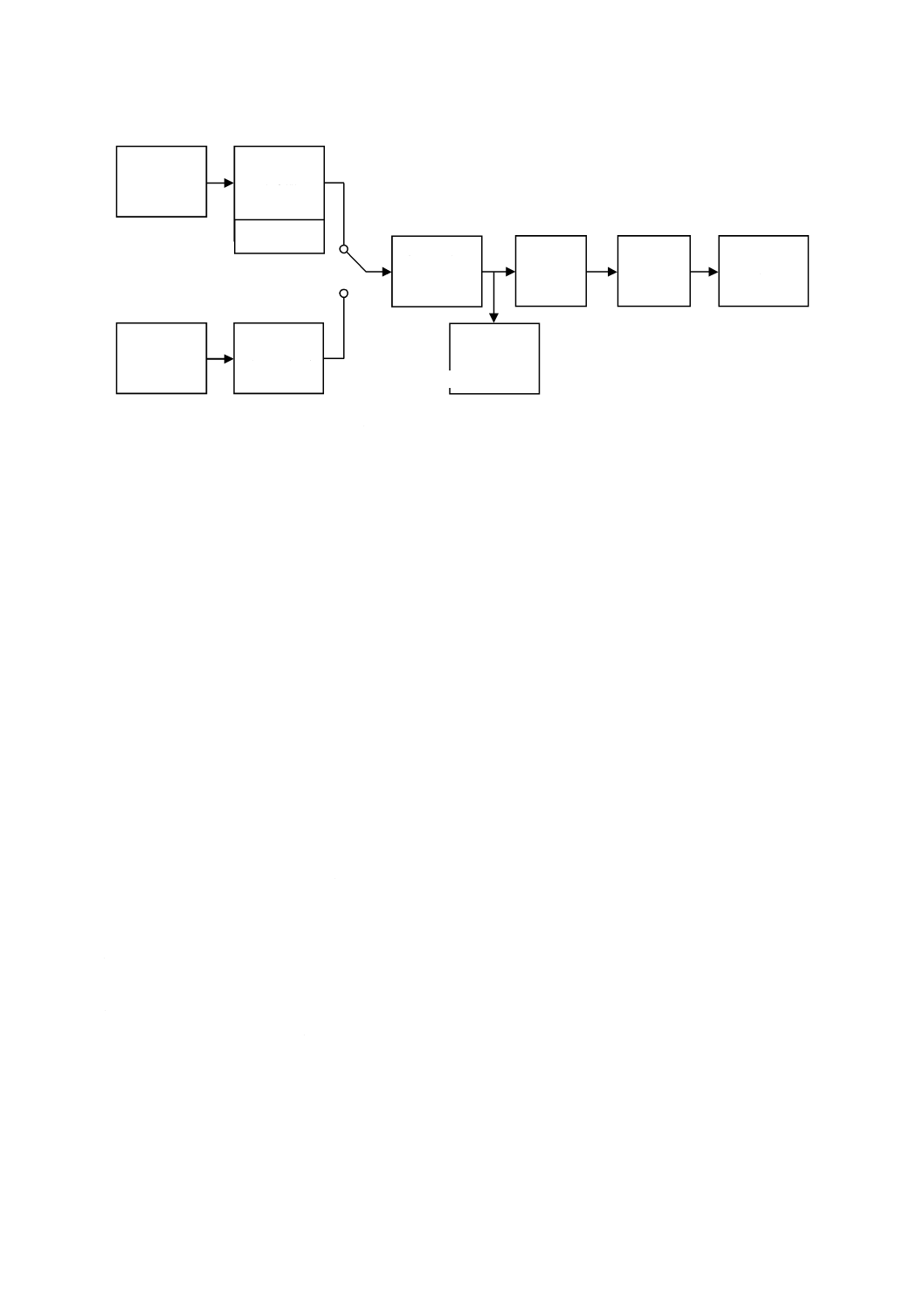

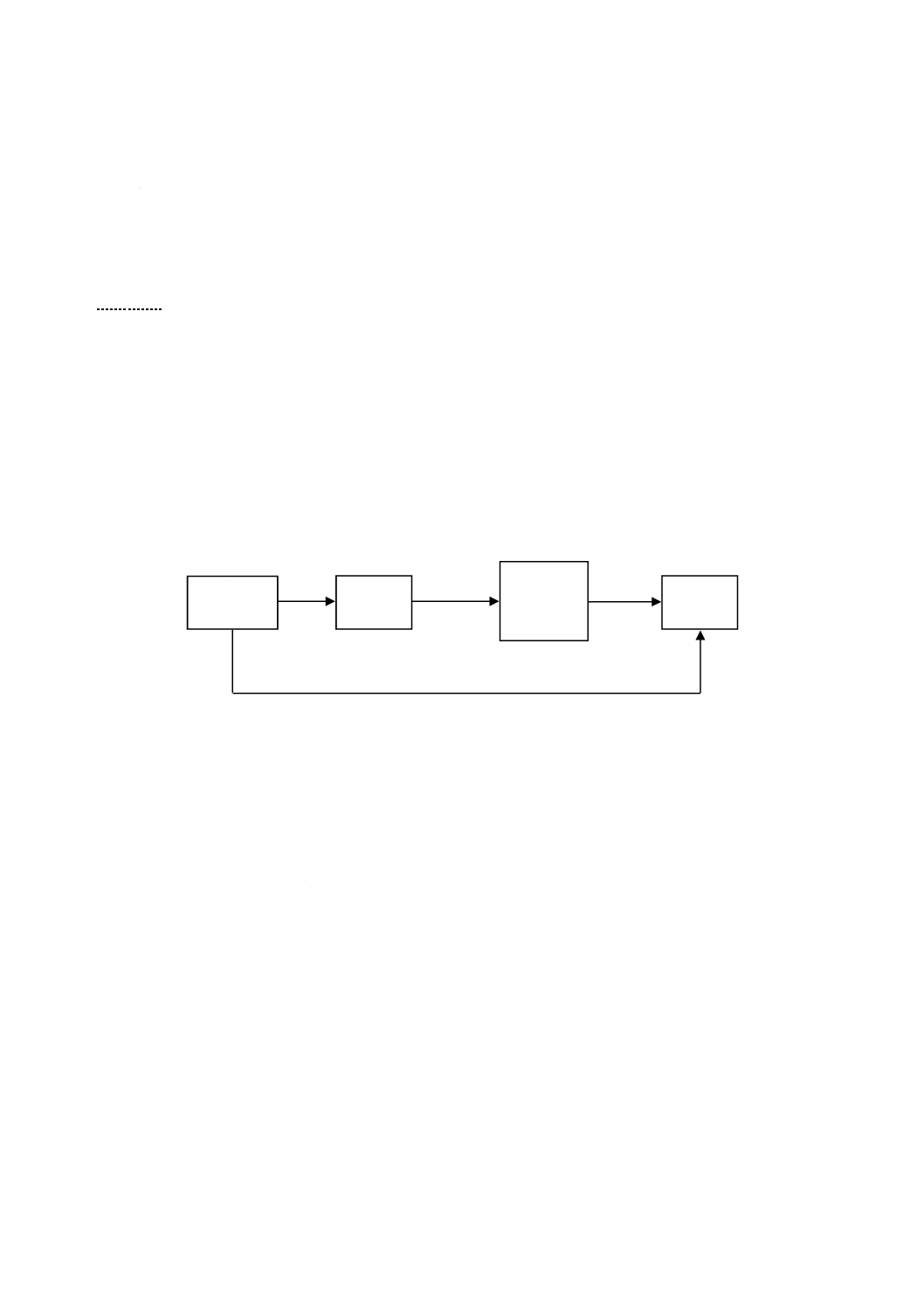

図1−ジッタ発生

4.1.2

アライメントジッタ

デジタルパターンがタイミング再生回路に伝えられると,デジタルパターンの連続的変化によって,再

生クロック信号に,入力データに関連したアライメントジッタが生じる。この影響は,初めて参考文献[2]

によって詳細に分析された,ジッタ発生の主原因である。これは,再生クロック信号のジッタ成分が,リ

タイミングされるときにデータに付加されるということを意味する。このプロセスで引き起こされたジッ

タの帯域幅は,使用しているクロック再生回路のアナログ帯域幅と同じである。

信号の再生のプロセスが同様の装置で繰り返されると,タイミングジッタ及びアライメントジッタによ

って,結果的にクロック信号のジッタ量が増加する。したがって,ジッタがデータ信号に付加されて,次

のタイミング再生時に増幅される。多くの中継器又はアドドロップ多重化装置をもつ伝送リンク内では,

このプロセスを繰り返すことによって,ジッタが増加する。タイミング再生の帯域幅が,信号のジッタ帯

域幅以上の場合は,ジッタは常に蓄積される。タイミング再生時のジッタの蓄積に関する解析は,参考文

献[3]によって初めて発表された。ジッタ増加を,式(4)によって示す。

6

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

()

∑

=

+

=

n

k

k

n

B

j

j

1

0

1

1

ω

ω

θ

θ

····························································· (4)

式(4)から,ジッタ電力密度スペクトルは,式(5)によって求める。

0

2

2

2

2

sin

φ

ω

ω

φ

≈

B

nB

n

n

n

ω<<Bのとき············································ (5)

ここに,

θn: n段のタイミング再生プロセス後のジッタ振幅

θ0: 各タイミング再生プロセスのジッタ振幅

n: タイミング再生プロセスの段数

ω: ジッタ成分の角周波数

B: タイミング再生回路の半分の角帯域幅

φn: n段のタイミング再生プロセス後のジッタ電力密度

φ0: 各タイミング再生プロセスのジッタ電力密度

ジッタ振幅は,タイミング再生プロセスの接続数によって線形に増えるため,低い周波数の電力密度に

は注意するのが望ましい。

2地点間通信装置においては,入力データから送信タイミングを抽出しないので,アライメントジッタ

及びジッタ増加は,重要な問題ではない。

4.1.3

他の影響

デジタル信号の伝送過程では,雑音付加,分散効果などの劣化要因によって,信号からタイミングを再

生するときに,ジッタ成分が増える。デジタルリンク長を延ばすために,デジタル再生よりむしろ,アナ

ログ増幅器を使うときの方が,その影響は大きい。

4.2

信号品質へのジッタの影響

規定のジッタ振幅及びジッタ周波数を許容できる装置の場合,ジッタはデータ伝送に影響を与えない

(4.3参照)。受信器の識別点がデータエッジに近い又は越えるようなジッタが大きい又は速い場合,誤り

が生じ,BERが劣化する。そのようなジッタは,デジタルリンク上の音楽,又はアナログサービスに,深

刻な影響をもたらす。ジッタの影響は,不要な周波数及び位相変調成分をもたらし,それが音楽で聞こえ

たり,テレビ映像に見えたりする。

4.3

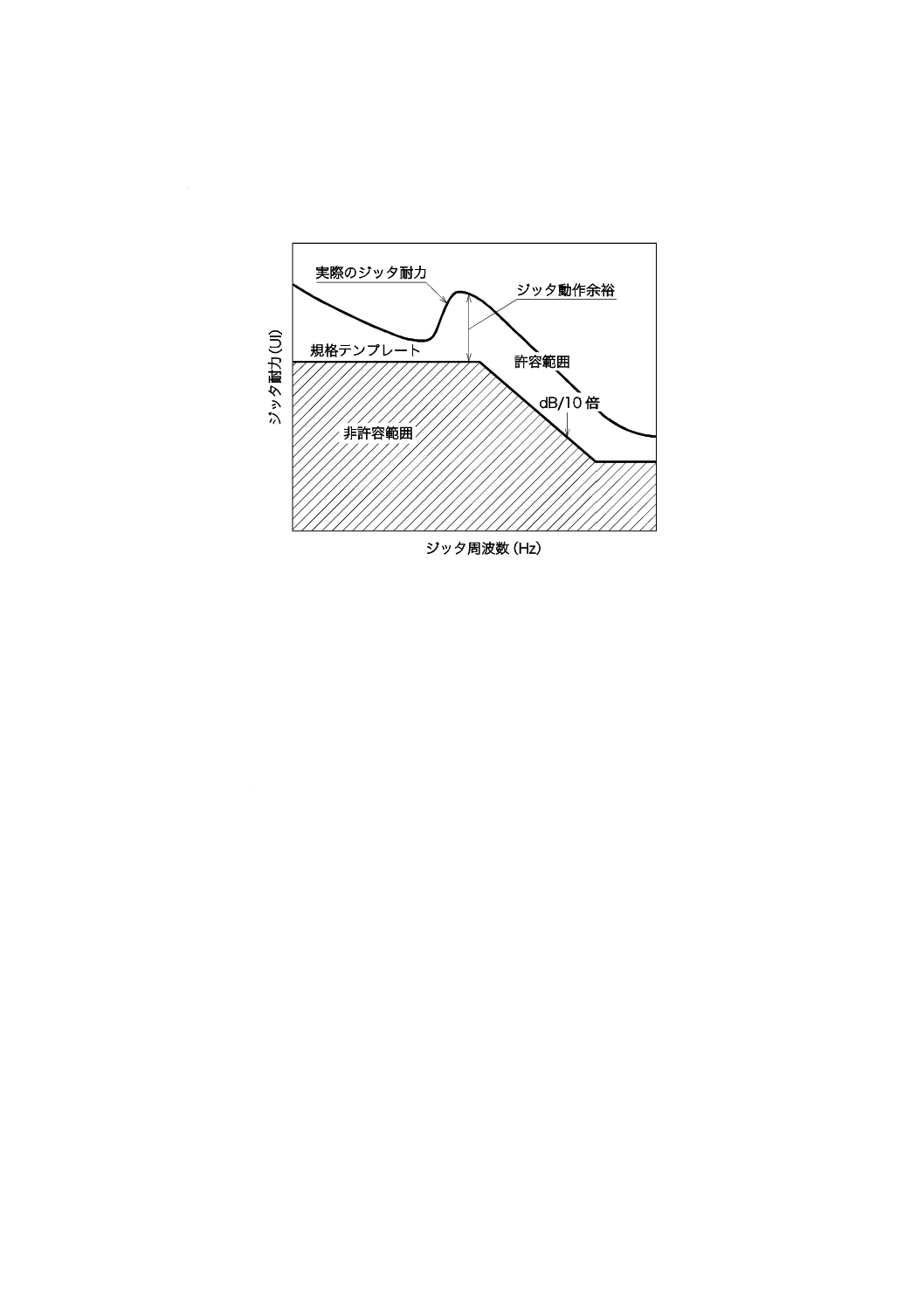

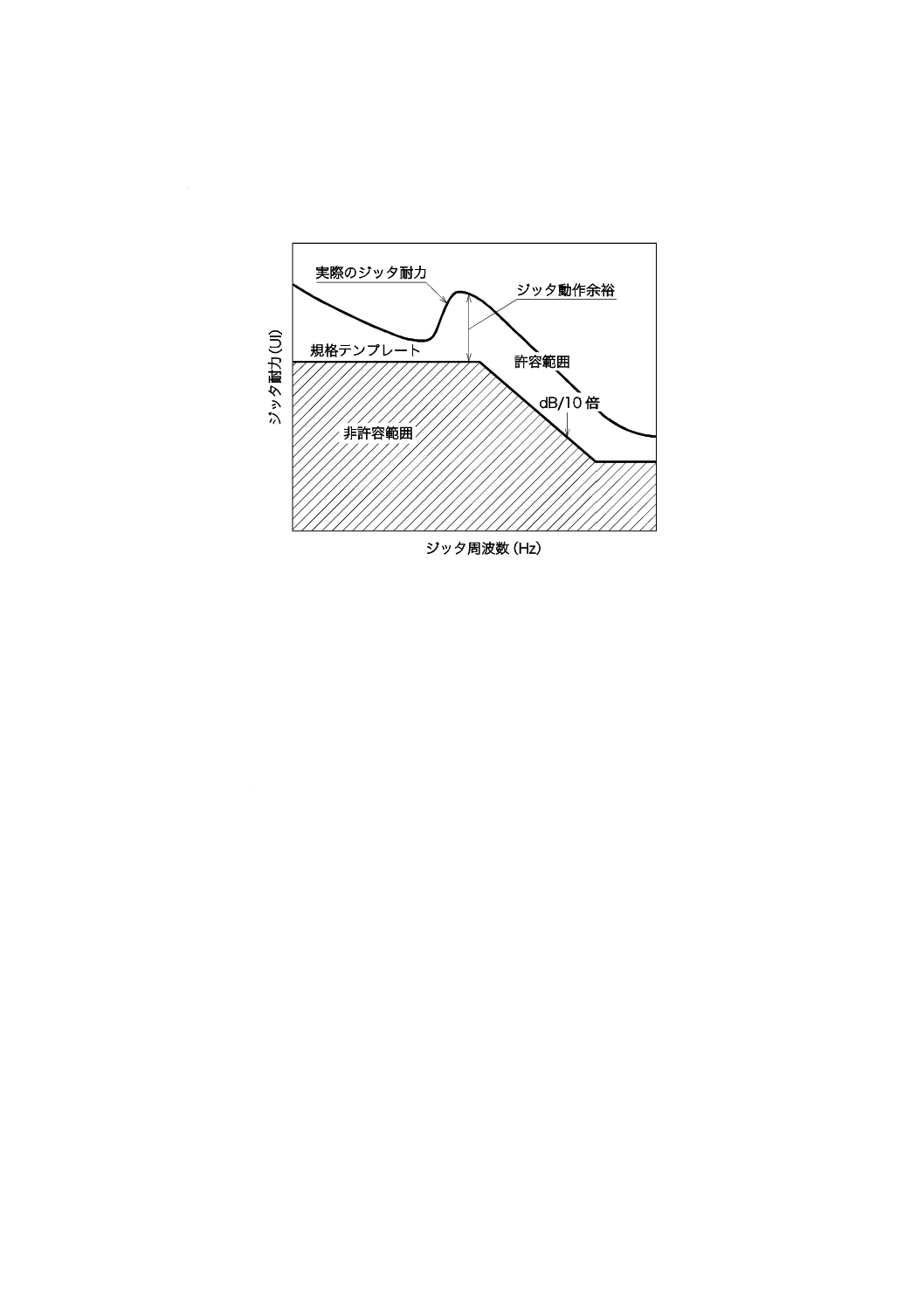

ジッタ耐力

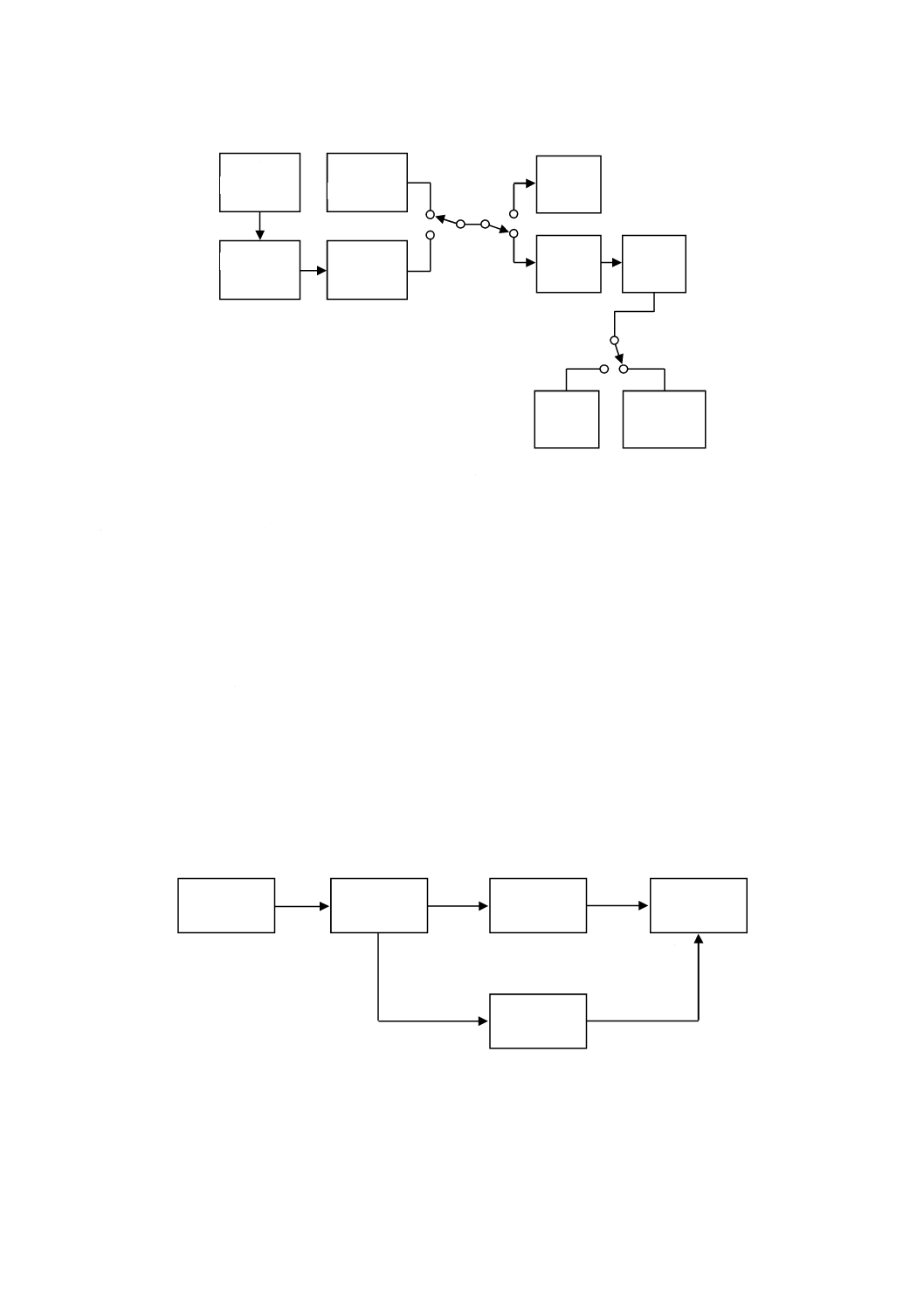

情報通信システムにおいては,ジッタ耐力の要求事項は,特定の正弦波変調の振幅・周波数におけるジ

ッタテンプレートで規定する。ジッタテンプレートは,装置が誤り性能の劣化を起こさずに受け入れるこ

とができる最小ジッタ値を表す。実際のジッタ耐力とジッタテンプレートとの一般的な関係を,図2に示

す。

与えられた周波数において装置が実際に耐えられるジッタ振幅は,誤り性能の劣化を引き起こさない最

大振幅と定義する。誤り性能の劣化は,ビット誤り率ペナルティ法又はエラー発生法のいずれかの評価基

準に用いて示してもよい。二つの評価基準が用いられるのは,デジタル装置の入力のジッタ耐力が,主に

次の三つの要素によって決まるためである。

a) パルスひずみ,クロストーク,ノイズ及びその他の障害と一緒にジッタを含んだデータ信号から正確

にタイミングを再生する入力クロック再生能力。

7

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

b) ジッタ振幅を許容するための,例えば弾性メモリなどの入力バッファ回路の能力。

c) パルス調整能力及び非同期デジタル多重化装置の同期・非同期バッファサイズのような動的に変化す

る入力データ速度を許容する部品の能力。

図2−ジッタ耐力の例

データ通信システムにおいて,ジッタ耐力は,単純な正弦波より複雑な信号障害によって決まる。ジッ

タ耐力の評価とは,実際のシステムで発生する信号を加えたとき,受信器が要求されるBER性能を満たせ

るかどうかを確認することである。したがって,ジッタ耐力のテスト信号は,送信器と通信路との両方で

許容される障害を含むことになる。例えば,実際の送信器には,周期性ジッタ,ランダムジッタ及びデュ

ーティサイクルひずみがある場合がある。信号が通信路を通過するときに,通信路の帯域幅制限によって

更に劣化し,符号間干渉ジッタが加わる場合がある。受信器は,実際のシステムにおいて,そのような信

号を許容できなければならない。すなわち,受信器のジッタ耐力を確かめるために使用する信号は,これ

ら障害の全てを含まなければならない。この検査方法を,“ストレスアイ”試験と呼び,受信器に入力する

信号のアイパターンを意図的に劣化させる,又はストレスを与える。

4.4

待機時間ジッタ

非同期信号を多重送信するとき,多重化装置のトリビュタリタイミングと入力デジタル信号との位相比

較に関係付けたスタッフ同期技術(パルススタッフィングとして知られている。)が用いられる。この技術

は,初期設定との差を検出したとき,多重フレーム構造のオーバヘッドを通して,制御信号を逆多重化装

置に対して送信する。制御信号に誤りがあっても確実に実行するために,この処理を3回又は5回繰り返

す。逆多重化装置では,制御信号を認識するために大きい値を取る。この処理によって,デマルチプレク

サで,スタッフ同期の要求とその実行との間で,不確定な状態及び変動する遅延が生じ,待機時間ジッタ

として現れる。

4.5

ワンダ

伝送路の遅延の周期変化及びデータクロックのゆっくりとした周波数変化は,ワンダを引き起こす。最

も重要なワンダは,時間,日,月,季節などの遅い頻度で繰り返されるため,10 Hzというジッタとワン

ダとの間の境界は,少し不自然となる。一般的には,温度変化が,伝送媒体又は装置の遅延に影響して,

8

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ワンダの原因となる。陸地上伝送時のワンダ成分は,通常,数十ナノ秒までに限られる。

同期ネットワークにおいては,ビットのスリップによってデータ損失を伴う再同期化プロセスが始まる

ため,ワンダの調整は,不可欠となる。データ損失が高次の逆多重化装置で発生すると,全ての低次デー

タも再同期を行い,データ損失を増大させる。ワンダは,通常,ジッタを調整するために使用するバッフ

ァメモリサイズを増やすことによって許容できる。

特別なケースとして,静止衛星を通した通信で,ワンダの影響が生じることがある。そのような衛星の

横方向の位置は比較的安定しているが,地上35 000 kmの平均高度では,約±1 000 kmで日周変動が発生

する。これはおよそ26 msの遅延変動をもたらす。150メガビット/秒のデータ信号速度において,これ

は,45ビット/秒のワンダに相当し,同期ネットワークでそれを許容するには,3.9メガビット以上の容

量をもつ弾性メモリが必要となる。

5

ジッタテスト手順

5.1

ジッタ測定方式

5.1.0A

一般

ジッタを測定するためには,アナログ方式又はデジタル方式のいずれの方式を用いてもよい。両方式と

も,再生タイミング信号又は被測定信号そのものと,周波数が理想的に安定したクロック信号との間の位

相比較によって測定する。電気通信の用途では,被測定信号から抽出したタイミング信号の周波数を平均

化してこの理想的な信号(クロック)を生成する。生成したクロックのジッタ帯域幅は,10 Hz未満でな

ければならない。データ通信の用途では,一般的に,基準クロックも信号から生成するが,多くの場合,

生成した信号のジッタ帯域幅は,送信器と対になる受信器のクロック再生帯域幅と同じである。システム

として使用する場合は,受信器の帯域内ジッタが,受信器へ及ぼす影響は少ない。測定においては,基準

信号と被測定信号との両方に共通するジッタは,意図的に観測しない。これは,基準信号のジッタ帯域外

のジッタを観測することで実現できる。

5.1.1

アナログ方式

アナログ方式は,再生クロックと安定クロックとの位相比較によって,再生クロックのジッタ周波数及

びジッタ振幅成分に関連したパルス幅変調信号からなるアナログ出力を使用する。この出力は,次段でア

ナログ出力に変換する。全てのアナログ測定技術と同様に,このアナログ方式は,注意深い校正を必要と

し,安定性を含む位相比較器の性能に大きく依存する。

5.1.2

デジタル方式

5.1.2.1

狭ジッタ帯域幅クロックに対する生成クロック

デジタル方式は,再生クロック信号と生成した安定クロック信号との間の時間差を測定するために,高

速なサンプリングクロックを使用する。その測定結果は,測定時間間隔のデジタル処理によって求める。

この方式は,正確な結果を得ることができ,デジタル技術を使用した測定器に適している。この方式の主

な難点は,十分な分解能を得るために高速なタイミング信号を必要とすることである。

5.1.2.2

基準又は再生クロックに対するデータエッジ

データエッジの理想的な位置を示す基準クロックを使って,理想的な位置に対する被測定信号のエッジ

の位置の母集団を収集する。この母集団を後処理して,ジッタ性能を確定する。確定ジッタ成分とランダ

ムジッタ成分とは,分離できる。更なる処理によって,低い発生確率のジッタを直接測定する場合に必要

となる長時間の測定をしなくても,極めて低い発生確率のトータルジッタが推定できる。この技術によっ

て,非常に正確な測定及び推定ができる。この技術の主な難点は,発生確率の低い確定ジッタをランダム

9

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ジッタとして誤認することであり,次々にトータルジッタの推定を悪く見積もってしまうことである。テ

ストシステムの帯域幅制限及びノイズも,ジッタ源として振る舞うため,ジッタの結果が劣化する。

5.2

共通試験装置

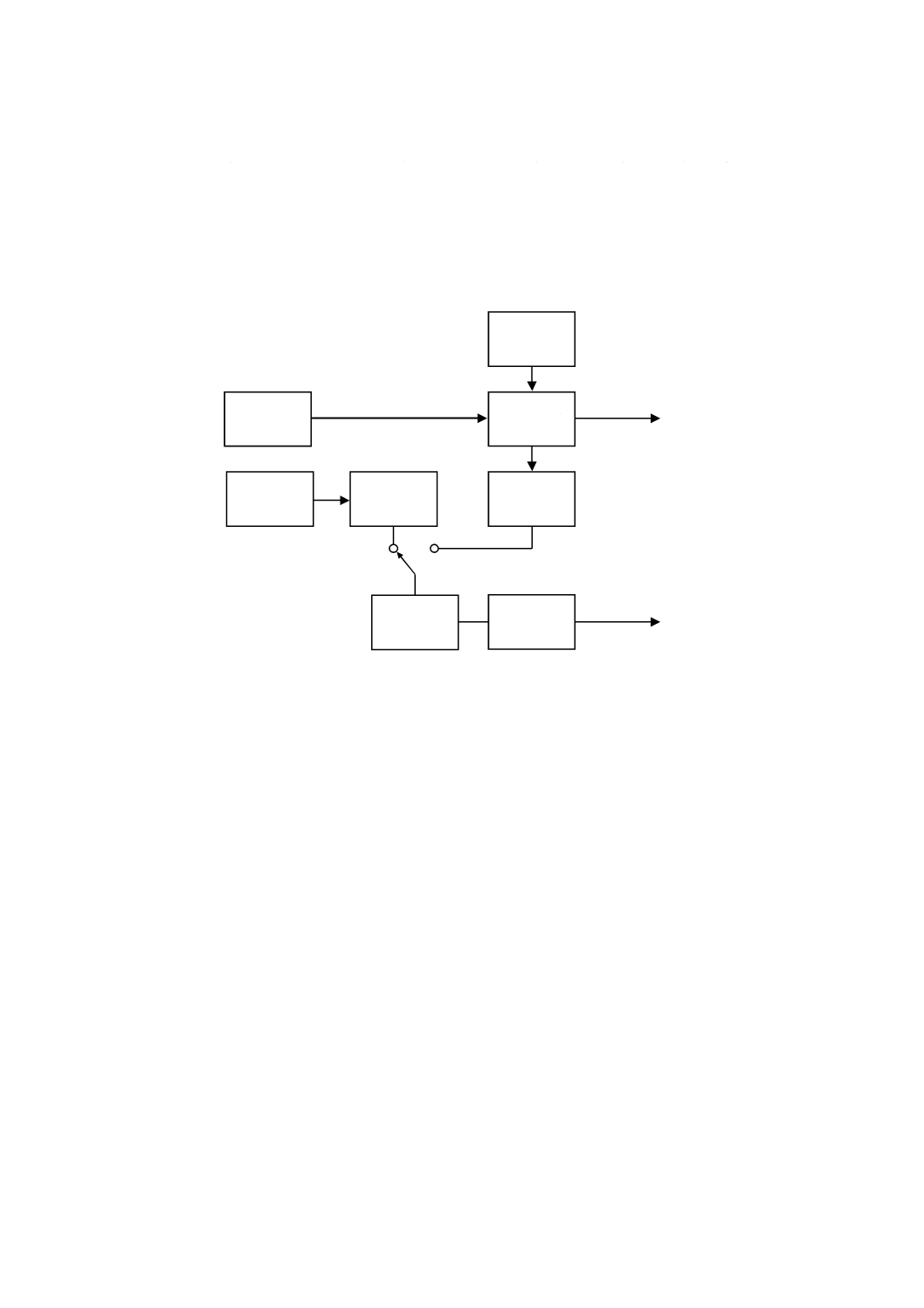

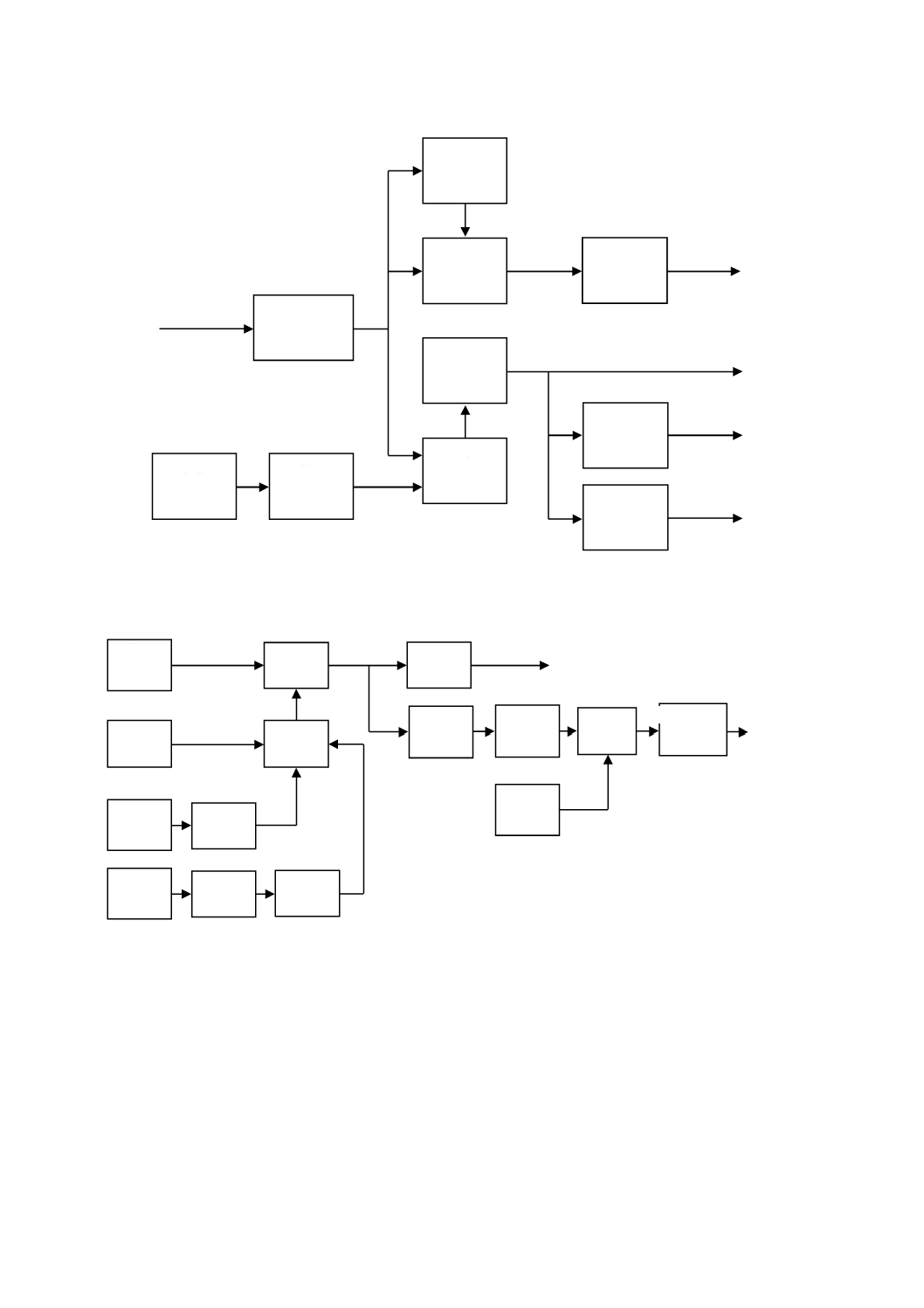

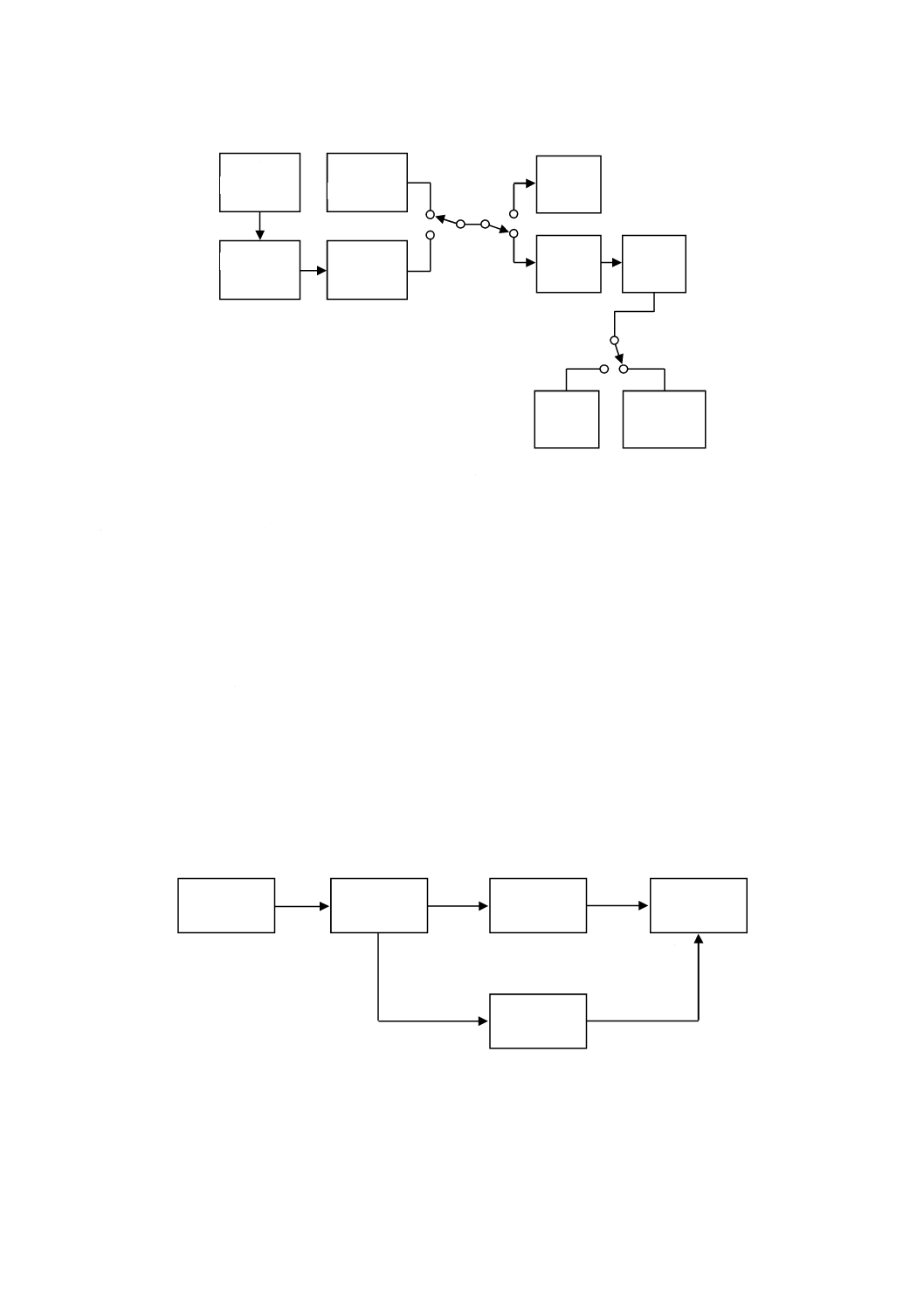

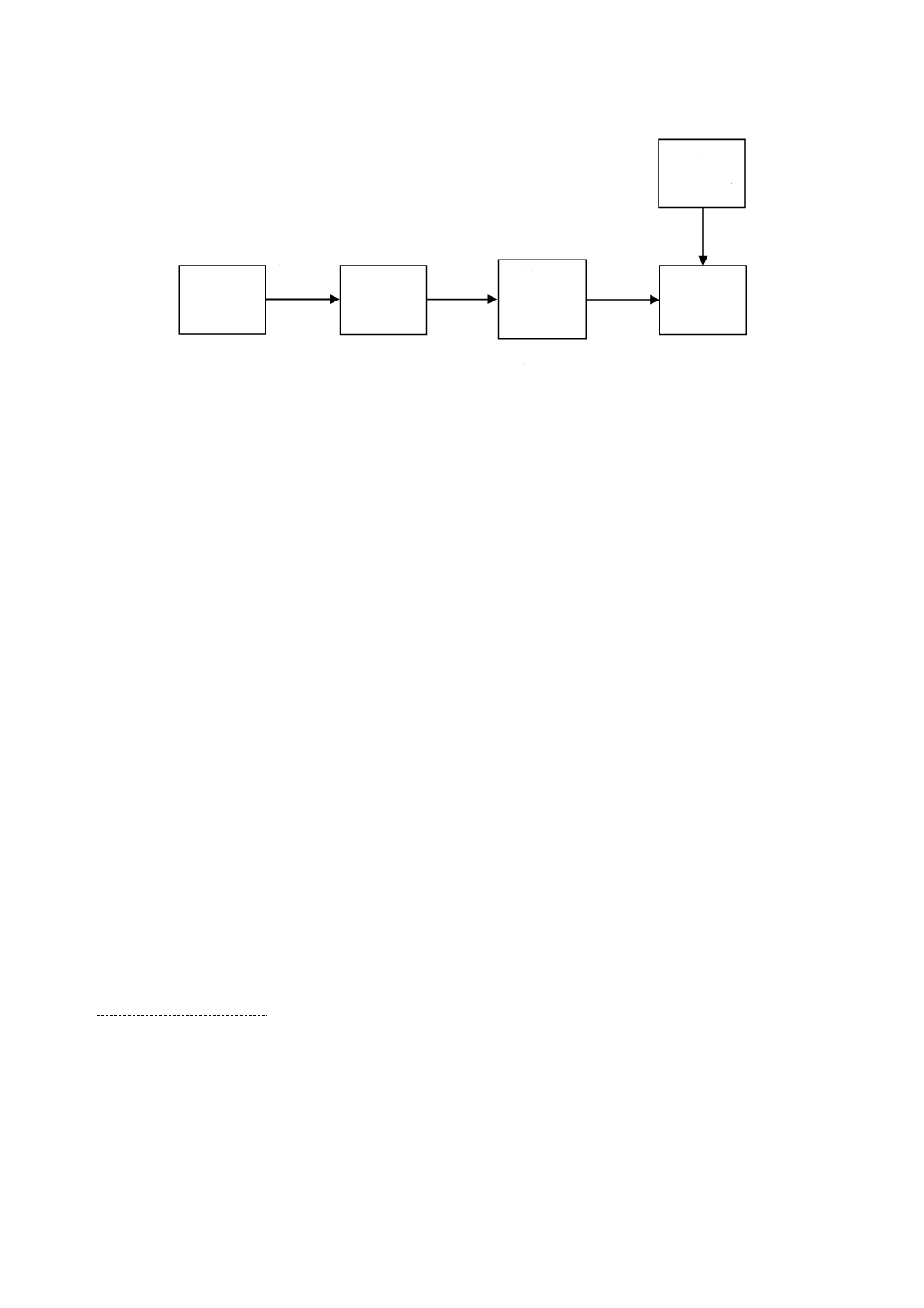

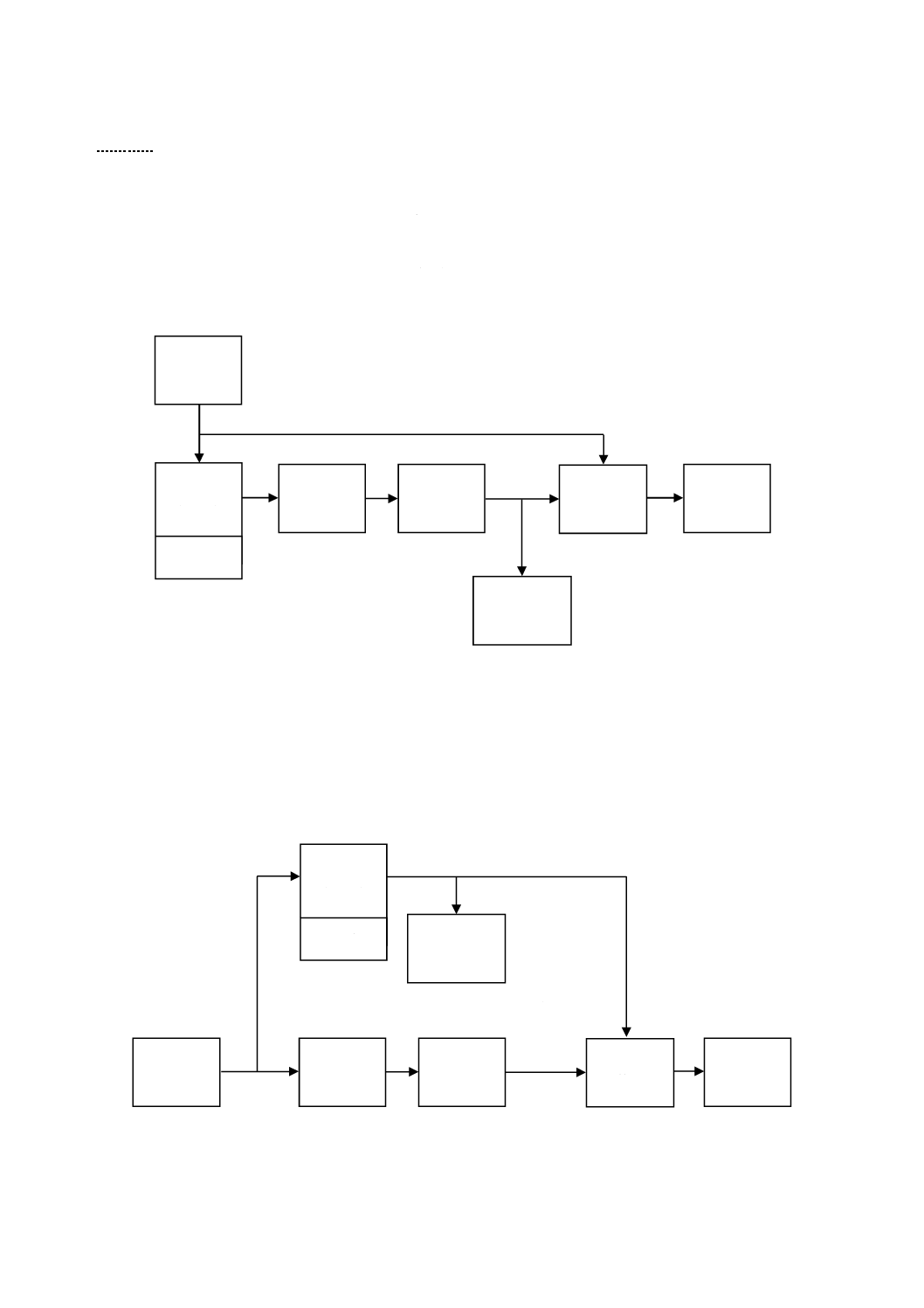

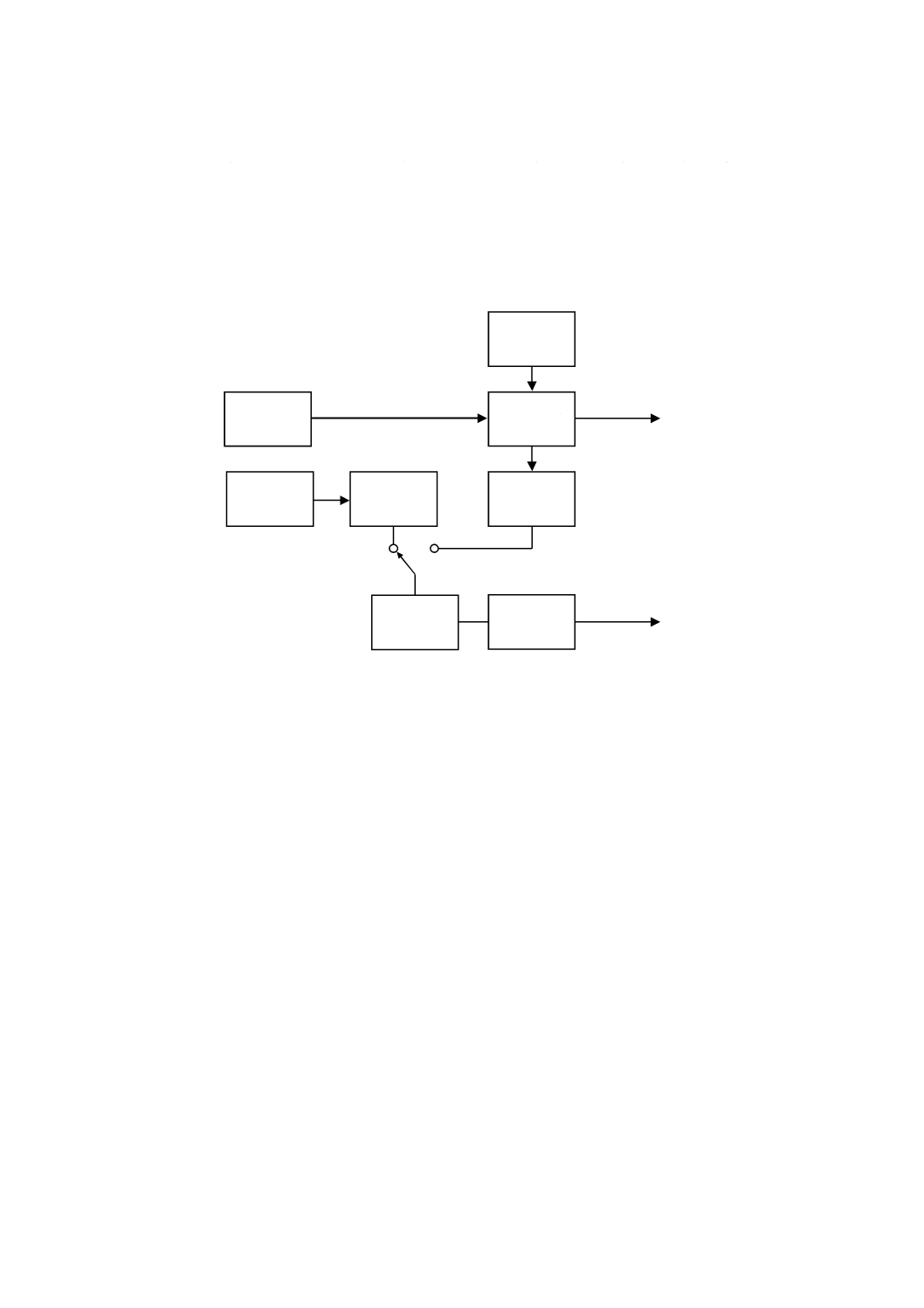

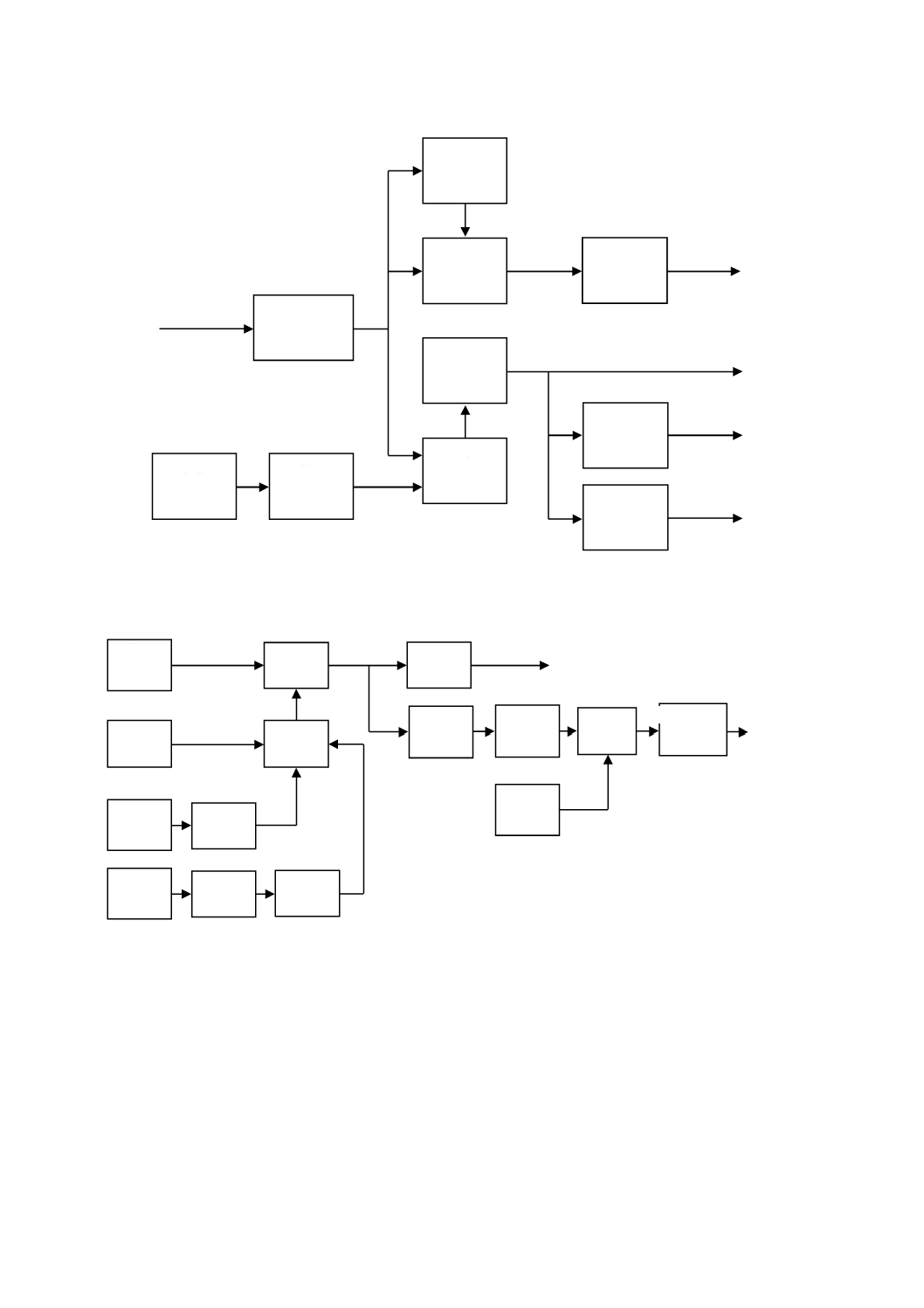

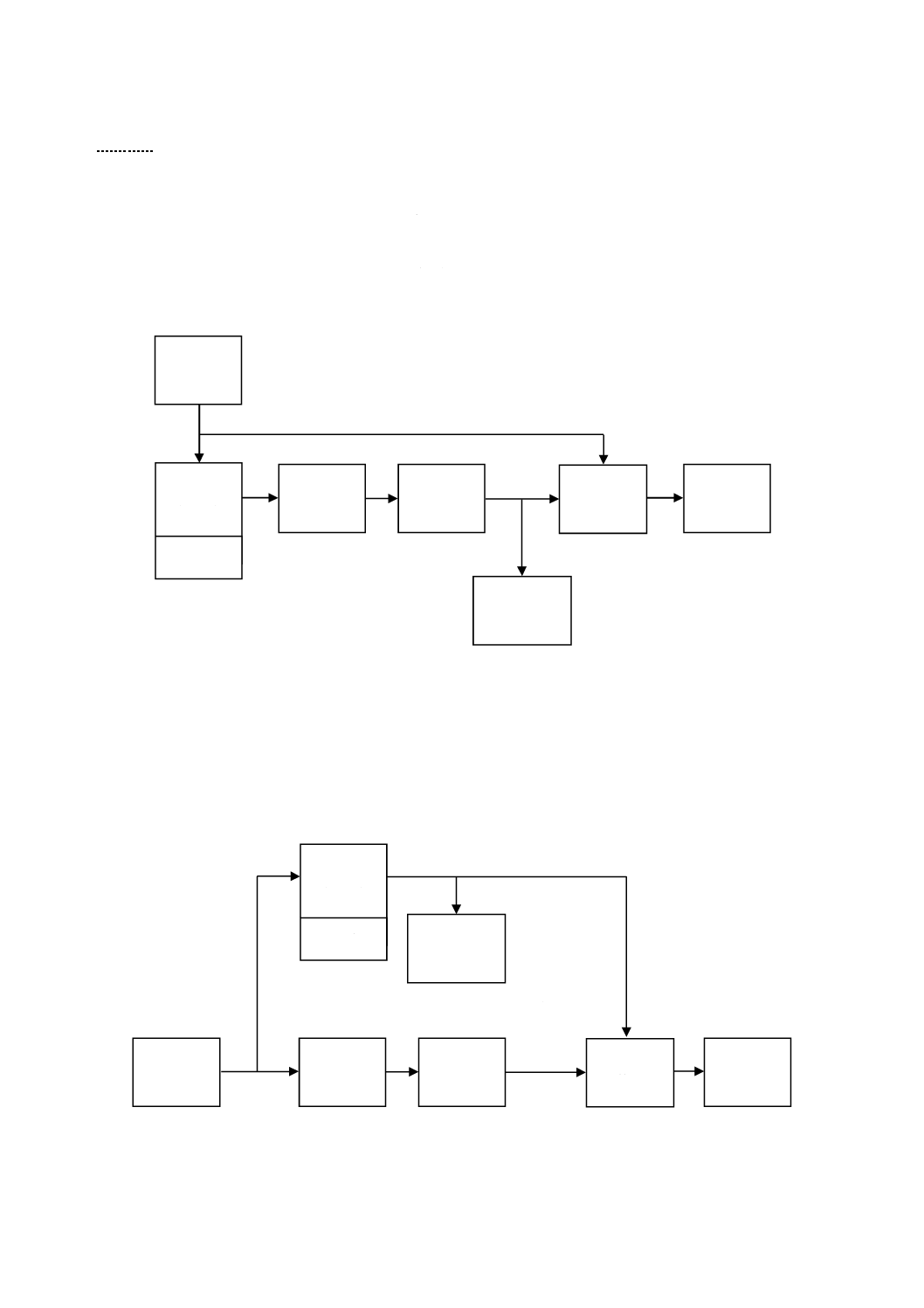

測定に使用する主な共通試験装置のブロック図を,図3,図4及び図5に示す。これらの図は,特定の

方法を意図してはいない。

図3−ジッタ及びワンダ発生器

テスト信号出力

テスト信号出力

ワンダ

TDEV

変調信号源

基準

タイミング

信号

電気光変換

インタ

フェース

外部基準

タイミング源

クロック

発生器

クロック

発生器

ジッタ

変調信号源

デジタル

信号発生器

10

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

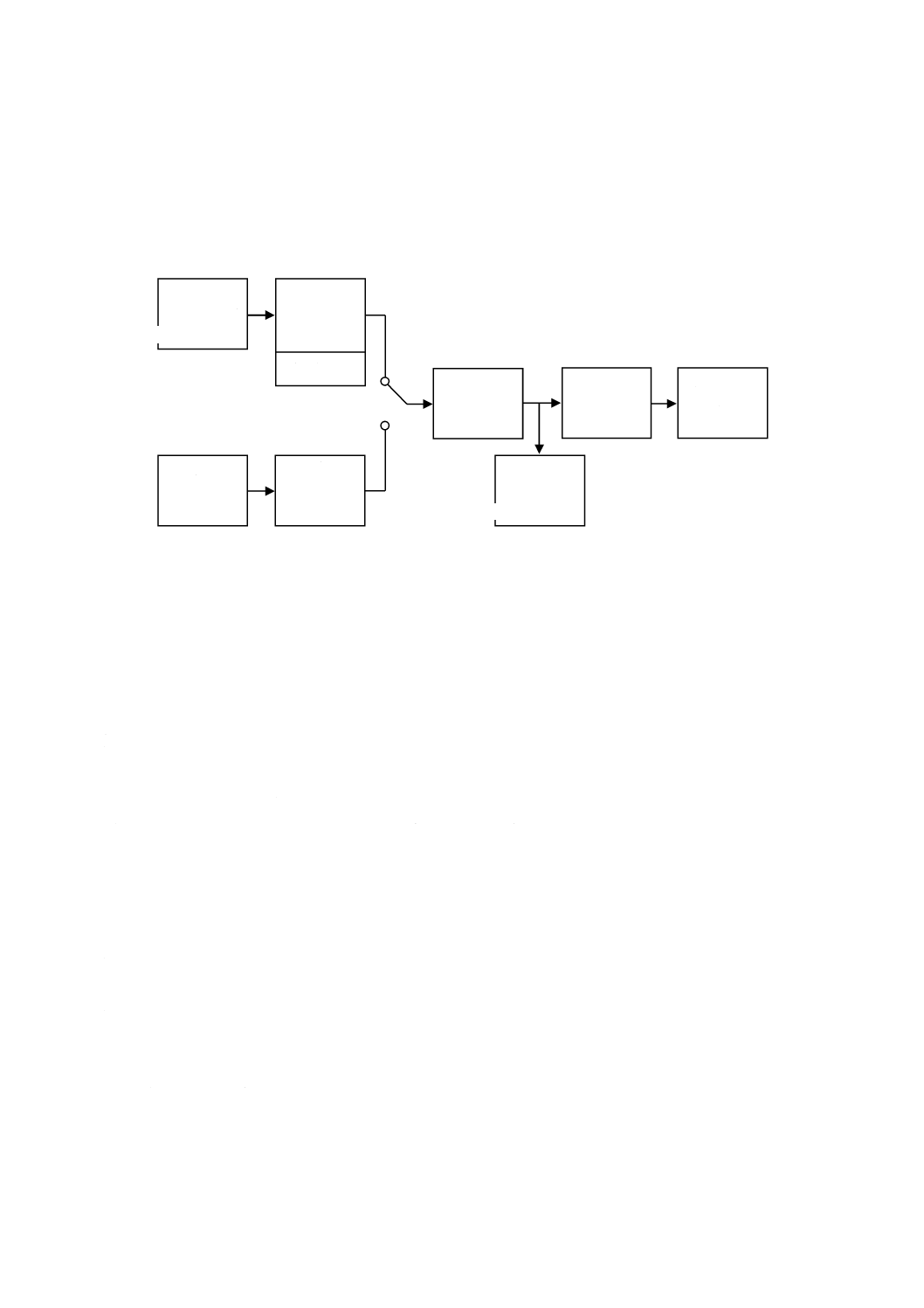

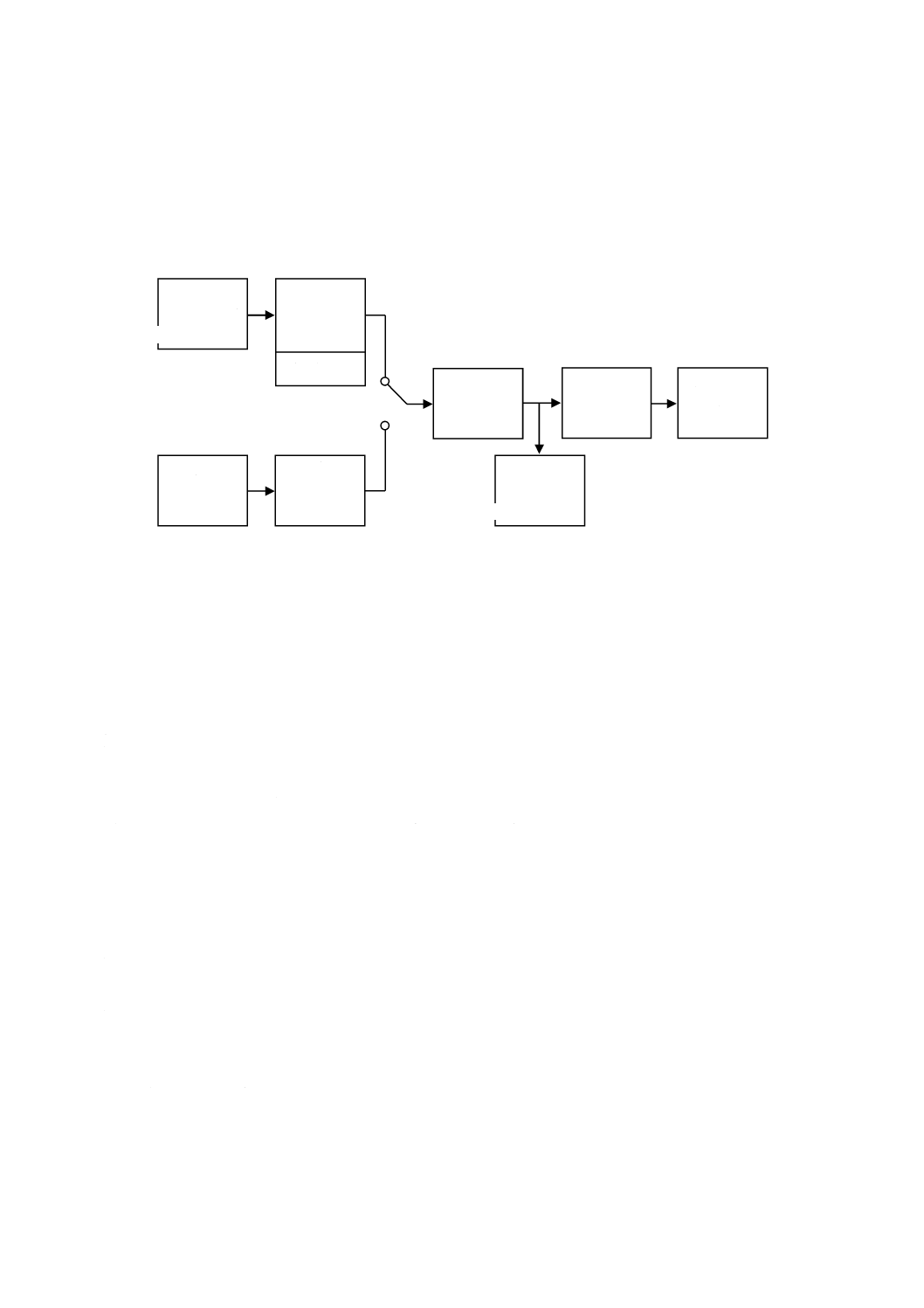

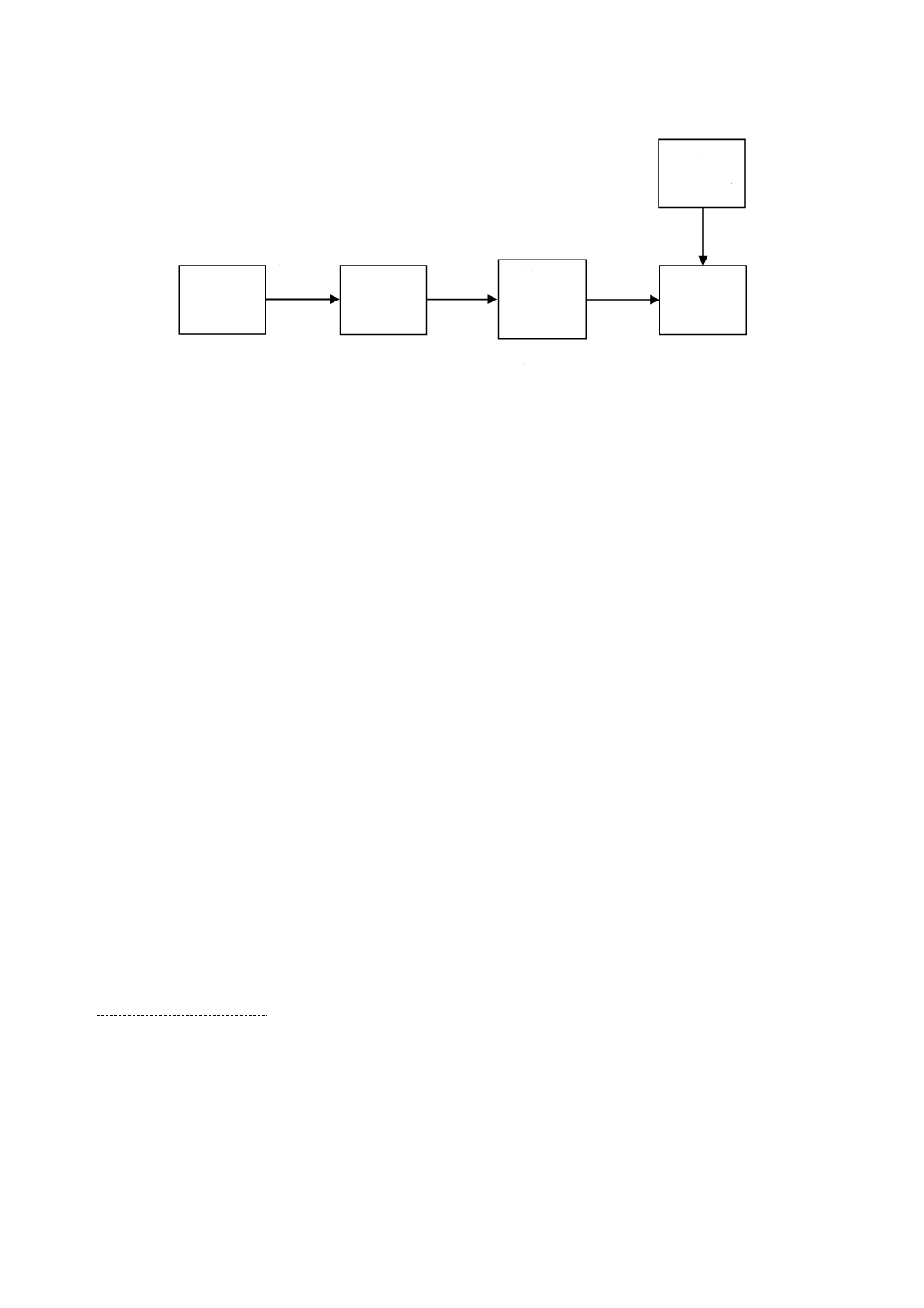

図4−ジッタ及びワンダ測定器

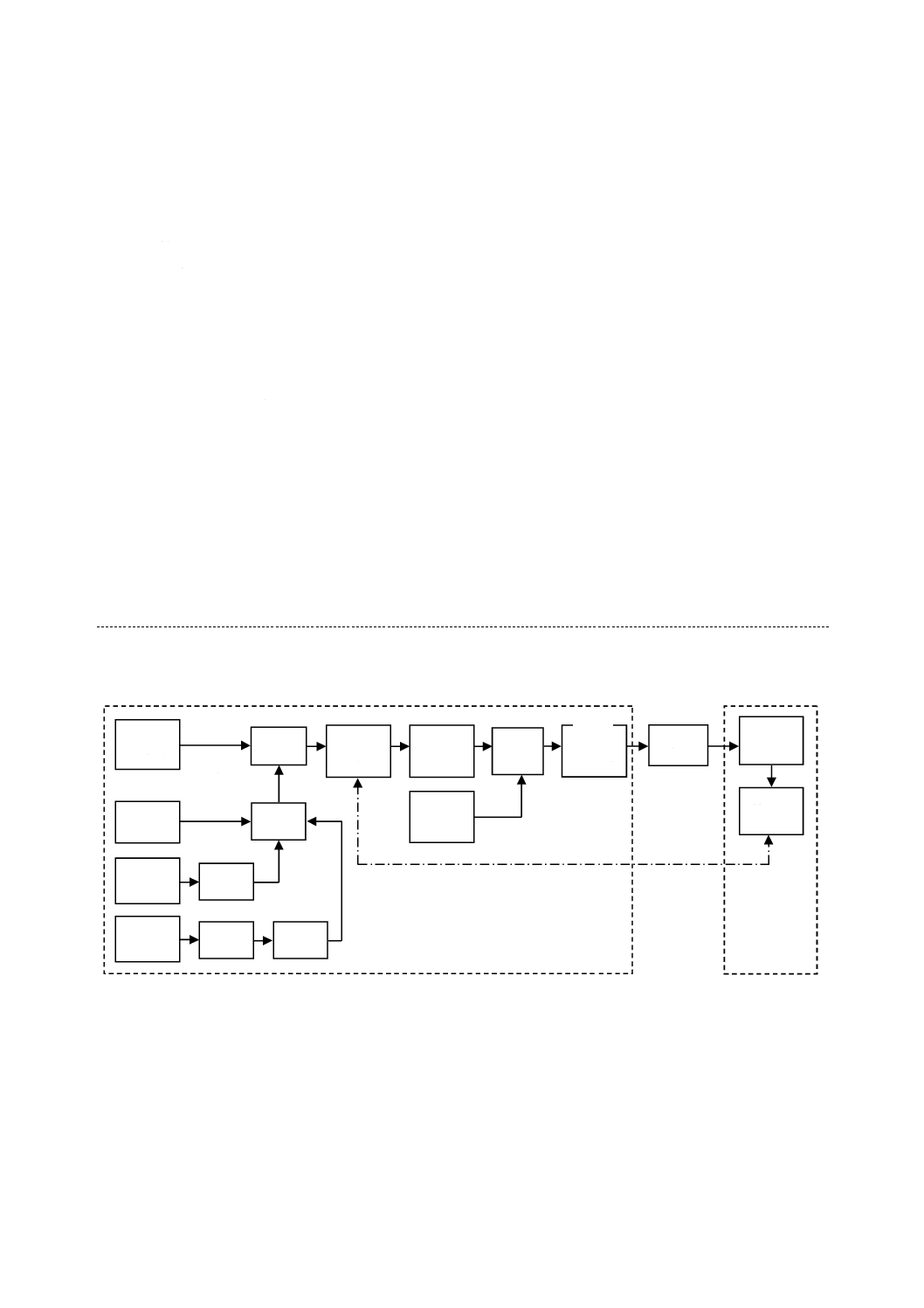

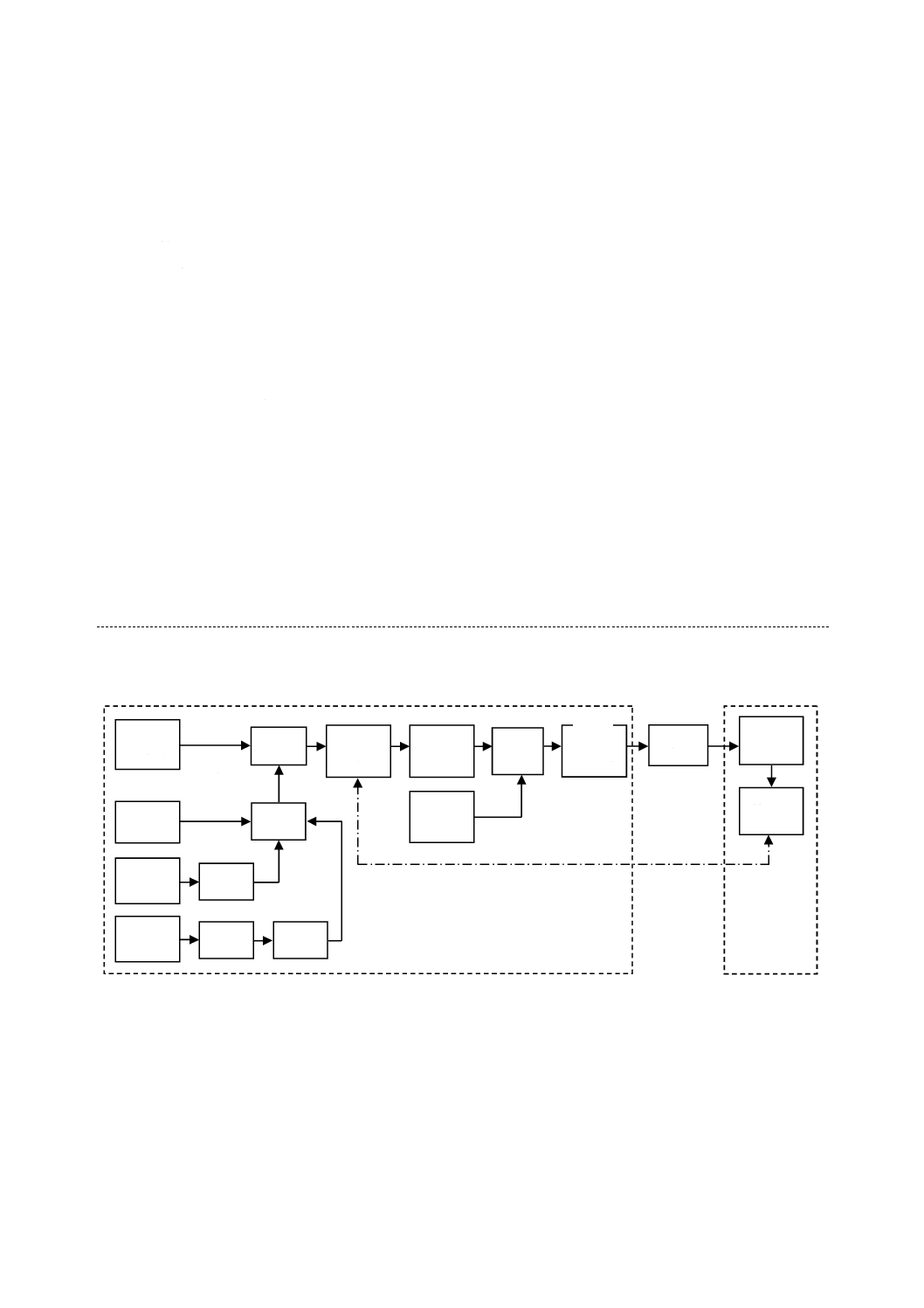

図5−ジッタストレス発生器

5.3

安全

レーザ若しくはLEDを用いた試験,又は光ファイバ通信システムで行う全ての試験は,JIS C 6802に準

拠した安全上の注意事項を適切に実施する。

5.4

光ファイバ接続

測定用の光ファイバ接続は,適切な光ファイバテストコードを使用する。

装置を接続する前に,全てのコネクタを清掃する。

高出力光信号の場合,テストコードの曲率半径は,30 mmを超えなければならない。

テスト信号入力

ジッタ結果

TIE結果

MTIE結果

TDEV結果

デジタル

信号受信器

位相

検出器

測定用

フィルタ

位相

検出器

測定用

フィルタ

外部基準

クロック源

基準

タイミング

信号

クロック再生付

電気光変換

インタフェース

MTIE

演算

TDEV

演算

ストレス

テスト信号

出力

クロック信号出力

変調器入力

基準

クロック

発生器

正弦波

発生器

PRBS

発生器

(オプション)

ノイズ

発生器

(オプション)

結合器

ジッタ

変調器

LPF

LPF

HPF

クロック

発生器

デジタル

信号

発生器

ベッセル

トムソン

フィルタ

電気光変換

インタ

フェース

結合器

正弦波

振幅

干渉計

11

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

5.5

測定サンプル

測定サンプルは,特定の装置又は試験用伝送路とする。

6

ジッタ耐力の測定

6.1

目的

この試験の目的は,装置に正弦波ジッタを印加した場合,規定した誤り性能となる,正弦波ジッタ振幅

で表されるジッタ耐力を測定することである。ジッタ耐力は,ジッタ振幅及びジッタ周波数の関数である。

6.2

使用する機器

測定に必要な機器を,次に示す。

− 変調信号源を内蔵したジッタ発生器,又は位相/周波数変調機能付き周波数シンセサイザ及び変調信

号源

− デジタル信号発生器

− デジタル信号受信器

− 減衰器

オプション機器を,次に示す。

− 周波数シンセサイザ

− ジッタ受信器

6.3

ビット誤り率ペナルティ法

6.3.0A

一般事項

ジッタ耐力測定のためのビット誤り率ペナルティの評価基準は,与えられたジッタ周波数におけるジッ

タ振幅値として定義する。このジッタ振幅は,特定の信号対雑音比の減少によって発生するビット誤り率

の劣化に相当する。

6.3.1

機器の接続

ビット誤り率ペナルティ法の測定構成を,図6に示す。オプション機器の周波数シンセサイザは,より

高確度な周波数設定をする場合に使用する。これは,非同期デジタル多重化装置などの機器の測定の再現

性を得るために,特に重要である。オプション機器のジッタ受信器は,発生させたジッタ振幅を確認する

ために使用する。

注記 位相/周波数変調機能付き周波数シンセサイザ及び変調信号源は,変調信号源を内蔵したジッ

タ発生器の代わりに用いることができる。

12

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図6−ビット誤り率ペナルティ法の測定構成

6.3.2

機器設定

ビット誤り率ペナルティ法は,二つの手順に分けられる。第1手順では,被試験機器に対し,信号対雑

音比の基準点に対して二つのビット誤り率を測定する。ジッタを付加しない状態で,適切なビット誤り率

を得るまで信号を減衰する。識別回路での信号対雑音比が特定の値分(1 dB)増加するように,信号を増

幅する。第2手順では,信号対雑音比の基準点でのビット誤り率を使用し,与えられたジッタ周波数で,

ビット誤り率が初期値になるまで,ジッタをテスト信号に付加する。既知の識別回路のアイマージンは,

信号対雑音比の基準点に対する二つのビット誤り率で規定されるため,付加した相当のジッタは,識別回

路のジッタ耐力性能の高確度で,かつ,再現性の高い尺度となる。適用したジッタ周波数範囲において,

被試験機器の連続した正弦波入力ジッタ耐力を測定するために十分な数の周波数で,第2手順を繰り返す。

テスト機器は,データストリームのジッタ信号又は信号対雑音比を調整でき,被試験機器のビット誤り率

を測定できなければならない。

6.3.3

測定手順

測定手順は,次による。

a) 機器を,図6に示すように接続する。適度に連続して,エラーのない動作をすることを確認する。

b) ジッタを付加しない状態で,1秒当たり100以上のビット誤りが観測されるまで,信号を減衰する(す

なわち,ITU-T Recommendation G.8251ではビット誤り率=1E-10)。

c) ビット誤り率及び信号対雑音比を,記録する。

d) 信号対雑音比を特定の値分(1 dB)増加する。

e) 必要とする入力ジッタ周波数を,設定する。

f)

c) で記録したビット誤り率に戻るまで,ジッタ振幅を調整する。

g) 適用した入力ジッタの振幅及び周波数を,記録する。そして,ジッタ耐力曲線の特性を測定するため,

e)〜g) を,十分な回数,繰り返す。

6.4

エラー発生法

ジッタ耐力測定のためのエラー発生法の評価基準は,ジッタ振幅を30秒間継続して増大させ,測定時間

ごとの総エラー数が2エラー秒以下となる,特定のジッタ周波数における最大ジッタ振幅と定義する。

6.4.1

機器の接続

エラー発生法の測定構成を,図7に示す。オプション機器の周波数シンセサイザは,より高確度な周波

周波数

シンセサイザ

(オプション)

変調

信号源

周波数

シンセサイザ

(位相/周波

数変調付)

ジッタ

発生器

変調信号源

デジタル信号

発生器

被測定

機器

減衰器

デジタル信号

受信器

ジッタ

受信器

(オプション)

13

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

数設定を行う場合に使用する。オプション機器のジッタ受信器は,発生させたジッタ振幅を確認するため

に使用する。

注記 位相/周波数変調機能付き周波数シンセサイザ及び変調信号源は,変調信号源を内蔵したジッ

タ発生器の代わりに用いることができる。

図7−エラー発生法の測定構成

6.4.2

機器設定

エラー発生法では,評価基準を満足するエラーを発生させるテスト信号のジッタ周波数及びジッタ振幅

を設定する。この手法は,次の手順で行う。

a) ジッタ振幅を変化させているときは,エラーのない動作が途絶えるので測定しない。

b) ジッタ振幅を増加させるごとに,30秒間,エラー秒を測定する。

c) 累積で2エラー秒以下となる最大のジッタ振幅を,決定する。

この手順は,適用したジッタ周波数範囲において,被試験機器の連続した正弦波入力ジッタ耐力を正確

に測定するために十分に多くの周波数で,繰り返す。テスト機器は,制御されたジッタ信号を生成し,入

力信号のジッタによって起こるエラー秒を測定できなければならない。

6.4.3

測定手順

測定手順は,次による。

a) 機器を,図7に示すように接続する。適度に連続して,エラーのない動作をすることを確認する。

b) 必要とする入力ジッタ周波数に設定し,ジッタ振幅は0 UI p-pに初期設定する。

c) エラーが発生する点まで,ジッタ振幅を増加する。

d) 30秒以上測定し,エラー秒を記録する。初期測定は,0エラー秒でなければならない。

e) ジッタ振幅を少しずつ増加させ,エラー発生の評価基準を満足するまで,d) を繰り返し行う。

f)

設定した入力ジッタ振幅及び周波数を記録し,ジッタ耐力曲線を描くのに十分な数が得られるまで,

b)〜d) を繰り返し行う。

6.5

ジッタ耐力及びストレスアイ受信試験の測定

6.5.1

目的

この試験の目的は,通信網で発生するような理想的ではない信号がある環境で,用いる受信器又はシス

テムの能力を見極めることである。この試験は,ジッタ耐力試験と類似しているが,信号を意図的に劣化

周波数

シンセサイザ

(オプション)

変調

信号源

周波数

シンセサイザ

(位相/周波

数変調付)

ジッタ

発生器

変調信号源

デジタル信号

発生器

被測定

機器

デジタル信号

受信器

ジッタ

受信器

(オプション)

14

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

させるものを正弦波ジッタに限定せず,一般的に幾つかの信号障害メカニズムからなる点が異なる。

6.5.2

使用する機器

測定に必要な機器を,次に示す。

− デジタル信号発生器

− 誤り検出器

− ジッタ変調器

− 基準クロック発生器

− 正弦波発生器(正弦波ジッタ用)

オプション機器を,次に示す。

− PRBS発生器(周期的ジッタ用)

− 雑音発生器(ランダムジッタ用)

6.5.3

正弦波ジッタテンプレート法

ストレスには,幾つもの項目があるが,試験では他のストレス項目を固定し,一つのストレス項目を変

化させるのが一般的である。最も一般的な手法は,他のストレス項目を一定に保った状態で,不連続に正

弦波ジッタ周波数を変化させ,ビット誤り率を測定する方法である。

6.5.3.1

機器の接続

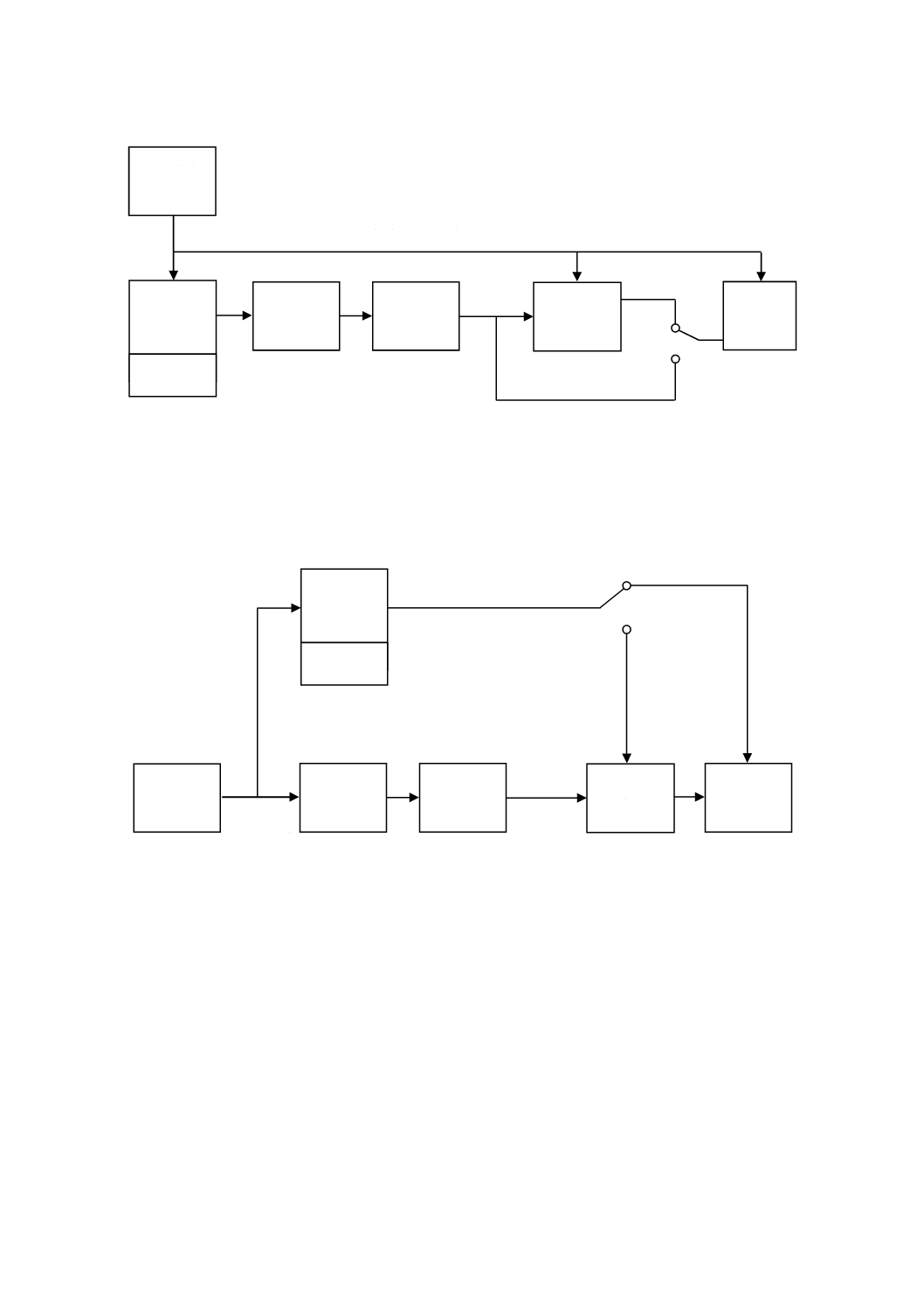

複数項目のストレスアイを発生する測定構成を,図8に示す。ストレス信号を,被試験機器に印加する。

被試験機器の出力は,ビット誤り率が測定できるように,誤り検出器で監視する。オプション機器のPRBS

発生器は,周期的ジッタを加える場合に使用する。また,オプション機器の雑音発生器は,ランダムジッ

タを加える場合に使用する。

図8−ストレスアイ試験のための測定構成

6.5.3.2

機器設定

この試験の目的は,特定のストレスレベルの信号を受信した際,被試験機器の最小ビット誤り率が達成

できることを確認することである。受信器への信号パワーは,システム動作で起こるような最悪の状態に

設定する。信号ストレス(正弦波ジッタ,ランダムジッタ,符号間干渉など)は,通常のシステム動作で

起こるような最悪の状態に設定する。

変調入力

デジタルジッタストレス発生器

テストパターン

誤り検出器

基準

クロック

発生器

正弦波

発生器

PRBS

発生器

(オプション)

雑音

発生器

(オプション)

ジッタ

変調器

LPF

デジタル

信号

発生器

ベッセル

トムソン

フィルタ

結合器

LPF

HPF

結合器

正弦波

振幅

干渉器

インタ

フェース

E/O

光ATT付

被試験

機器

インタ

フェース

O/E

誤り

検出器

CDR付

15

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

信号ストレスは,通常,何らかの正弦波ジッタを含んでいる。ジッタ周波数は,受信器の低周波ジッタ

応答特性を確認できるように,周波数範囲内で変化させる。実際の伝送網では,低周波ジッタのジッタ振

幅は,しばしば高周波ジッタより大きくなる。したがって,テストシーケンスでは,複数の不連続な正弦

波ジッタ周波数において,低周波では大きいジッタ振幅を用い,高周波では小さいジッタ振幅を用いて,

ビット誤り率を確認する。

複数のジッタ周波数で,ビット誤り率を測定する。適用したジッタ周波数範囲において連続的な正弦波

ジッタを入力した被試験機器のジッタ耐力を正確に測定するために,十分に多くの周波数で繰り返し測定

を行う。信号ストレスの他の項目は,固定値とする。

6.5.3.3

測定手順

測定手順は,次による。

a) 機器を,図8に示すように接続する。信号ストレス項目が機能しないようにし,連続動作及びエラー

のない動作をすることを確認する。

b) 必要とする入力ジッタの周波数及び振幅を設定する。必要に応じ,他のストレス項目が機能するよう

にする。

c) ビット誤り率を測定し,許容できるレベルであることを確認する。

d) ジッタ周波数を増加させ,適切なジッタ振幅を設定する。c) を繰り返す。

e) ストレスアイの受信耐力を確認するために,必要なジッタ周波数の全範囲で,d) を繰り返す。

7

ジッタ伝達関数の測定

7.1

一般事項

この試験の目的は,装置又は伝送網の入出力間でのジッタ振幅及びジッタ周波数の関係を決定すること

である。

7.2

使用する機器

測定に必要な機器を,次に示す。

− ジッタ発生器

− デジタル信号発生器

− デジタル信号受信器

− スペクトラムアナライザ

− ジッタ受信器

− 周波数シンセサイザ(オプション機器)

さらに,拡張するには,次の機器が必要となる。

− 正弦波発生器

− 位相変調機能付周波数シンセサイザ

− バッファアンプ

− 可変遅延器

− ドライバ

− ミキサ

− 低域通過フィルタ

− 位相計

− 電圧計

16

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

逆多重化装置技術を用いる場合には,多重化装置も必要となる。

7.3

基礎技術

7.3.1

機器の接続

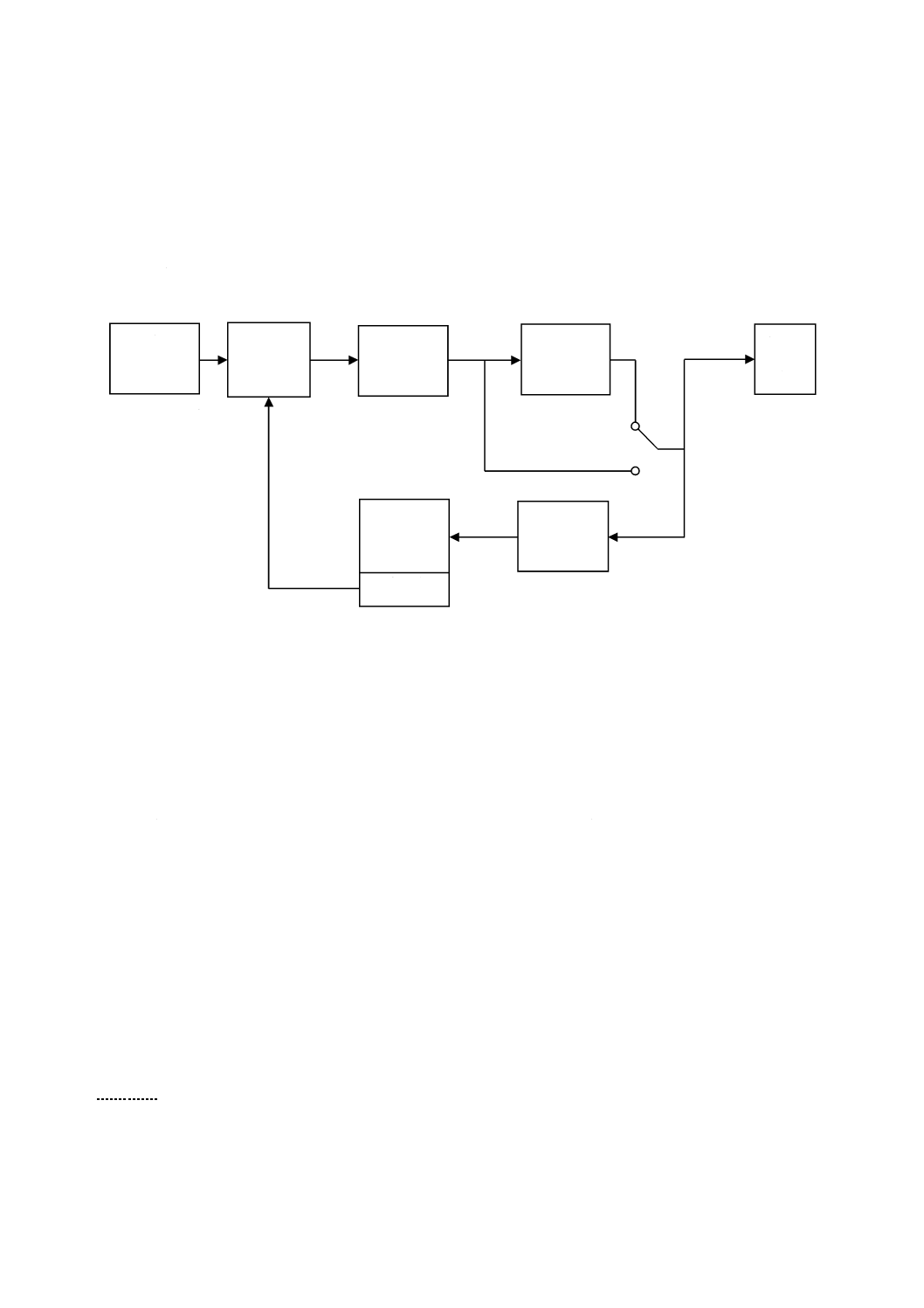

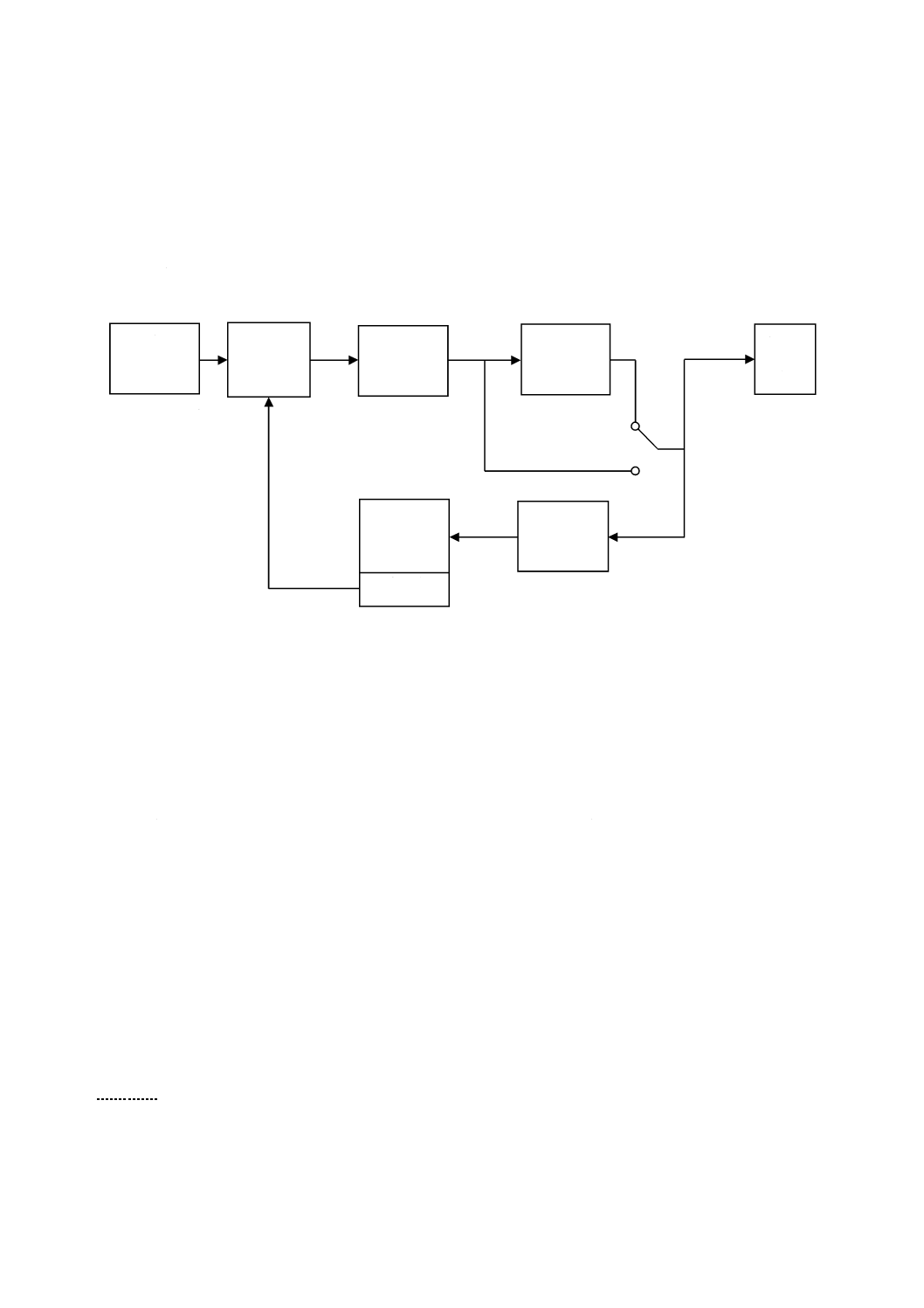

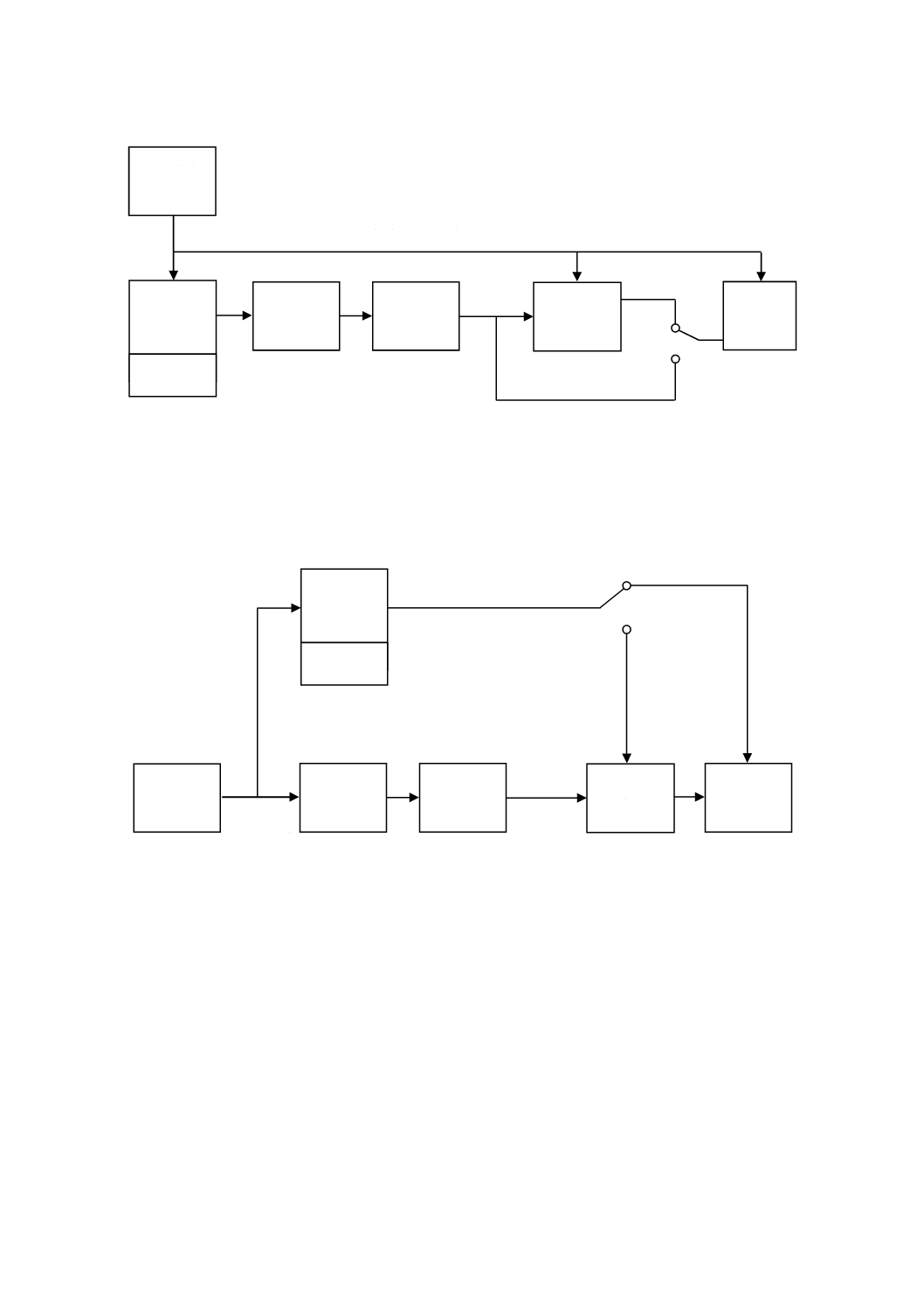

機器を,図9に示すように被試験機器をう(迂)回して接続する。適度に連続して,線形動作及びエラ

ーのない動作をすることを確認する。オプション機器の周波数シンセサイザは,より高確度な周波数設定

を行う場合に使用する。

図9−ジッタ伝達関数測定:基礎技術

7.3.2

機器設定

スペクトラムアナライザの周波数範囲を所定の値に設定する。ジッタ振幅が,選択した周波数範囲で,

適切な測定精度を保証できるくらいの大きさで,かつ,線形性が十分確保できるように,スペクトラムア

ナライザの連動形信号発生器の出力レベルを調整する。

必要とする周波数で掃引でき,かつ,試験に用いる機器の基準振幅が0 dBとなるようにスペクトラムア

ナライザの帯域幅をできるだけ狭く設定する(スペクトラムアナライザの帯域幅を狭くすると,ジッタ振

幅が減少しても測定精度を維持できる。)。

7.3.3

測定手順

被試験機器を,図9に示すように接続し直す。適度に連続して,線形動作及びエラーのない動作をする

ことを確認する。

スペクトラムアナライザを選択した周波数範囲で掃引し,全体(試験に用いる機器及び被試験機器)の

ジッタ伝達関数の振幅を測定する。被試験機器のジッタ伝達関数を得るには,全てのジッタ伝達関数から

0 dB基準振幅トレースを差し引く。

選択した周波数範囲において,十分に多くの周波数で,繰り返し測定する。

7.4

アナログ位相検出法

7.4.0A

一般事項

計測用クロック再生システムは,正弦波ジッタ振幅を測定するために用いる。クロック再生内蔵の位相

検出器の出力を,被試験機器への入力ジッタ及び被試験機器からの出力ジッタを正確に測定できるように

校正する。必要とする範囲でジッタ周波数を変化させ,かつ,入力ジッタに対する出力ジッタの比を調べ

ジッタ入力

連動形

発振器出力

テスト

シーケンス

テスト

シーケンス

校正時にう(迂)回

周波数

シンセサイザ

(オプション)

ジッタ

発生器

デジタル

信号

発生器

被試験

機器

デジタル

信号

受信器

ジッタ

受信器

スペクトラム

アナライザ

連動形

信号発生器

17

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

ることによって,ジッタ伝達の結果を得る。

この試験方法は,被試験機器への入力信号(校正手順における)又は被試験機器の出力信号からジッタ

を抽出する点においては,7.3と類似している。アナログ位相検出器はジッタ受信器として動作する。ただ

し,スペクトラムアナライザによって再生されたジッタを測定するよりも,一般的には校正されたAD変

換器の形態をとる位相検出システムを備えた計測器によってジッタ振幅を直接測定する。

7.4.1

機器の接続

被試験機器の種類によって,機器の接続は異なる。クロック再生システムには,データ入力及びクロッ

ク出力がある。中継器には,データ入力及びデータ出力がある。クロック逓倍器には,クロック入力及び

クロック出力がある。デジタル送信器は,高速データ出力を生成するために,被試験機器内部で逓倍する

基準クロック入力を使う場合がある(図10参照)。クロック信号又はデータ信号を直接アナログクロック

再生システムに接続して,信号源及び受信器のフラットネスを校正する(7.4.2及び7.4.3参照)。その後,

クロック信号又はデータ信号を被試験機器に接続し,被試験機器の出力をクロック再生システムに接続す

る。

図10−ジッタ伝達関数測定:アナログ位相検出法

7.4.2

機器設定

正弦波発生器は,周波数シンセサイザのジッタ(位相)変調レベルの生成に必要な振幅を設定する。一

般的に,最適なレベルは被試験機器に依存する。ジッタは,被試験機器又はクロック再生システムが非線

形領域動作にならない,又は非同期状態にならない程度に設定することが望ましい。正弦波の周波数は,

最初は被試験機器のループ帯域幅に比べて十分低い値に設定する。

7.4.3

測定手順

正弦波の周波数は,被試験機器のループ帯域幅よりも適度に広い範囲で変化させる(上下1桁程度)。そ

れぞれ設定したジッタ周波数でジッタ振幅を測定し,結果を記録する。ジッタは,同じ周波数範囲におい

て,校正と被試験機器出力との両方で,測定及び記録を行う。

7.4.4

測定結果の計算

ジッタ伝達は,校正時に測定されたジッタに対する被試験機器出力で測定されたジッタの比を取ること

によって求める。ジッタ伝達曲線は,試験した各ジッタ周波数での比をプロットすることによって得られ

データ

クロック

校正時にう(迂)回

周波数

シンセサイザ

パターン

発生器

正弦波

発生器

被試験

機器

アナログ

クロック

再生システム

18

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

る。

8

出力ジッタの測定

8.1

一般事項

この試験の目的は,ハイアラーキインタフェースの出力ジッタ及び個々のデジタル機器によって生成さ

れる本質的なジッタを測定することである。出力ジッタは,指定の周波数範囲におけるRMS又はピーク

振幅で測定され,統計的な特性評価が必要となる場合がある。

8.2

機器の接続

8.2.0A

使用する機器

測定に必要な機器を,次に示す。

− デジタル信号受信器

− デジタル信号発生器

− ジッタ受信器

− ジッタ測定フィルタ

− 電圧計

より高い精度が必要な場合に,次の機器を追加する。

− 周波数シンセサイザ

− スペクトラムアナライザ

8.2.1

機器設定

機器は,デジタル信号発生器と同じデータパターンを発生するように設定する。ジッタ振幅は,規定の

値に設定する。

8.2.2

測定手順

8.2.2.0A

一般事項

測定サンプルは,正常動作条件で使用され,システムの利用者から観測できる入力及び出力を標準的に

もつ光ファイバ伝送システムの一構成要素でなければならない。被試験機器としての測定サンプルを,図

11に示す。オプション機器の周波数シンセサイザは,より高確度な周波数設定を行う場合に使用する。

8.2.2.1

実トラフィック

機器を,図11に示すように接続する。適度に連続して,エラーのない動作をすることを確認する。

必要とするジッタフィルタを選択し,フィルタ後の出力ジッタを測定し,次いで特定の測定時間間隔で

発生した真のピーク間のジッタの振幅を測定する。

必要とする全てのジッタフィルタで,上記の手順を繰り返し測定する。

8.2.2.2

制御データ

制御されたジッタのないデータ(例えば,PRBS 223−1)を発生することのできるデジタル信号発生器を

用いて,被試験機器を図11に示すように接続する。適度に連続して,エラーのない動作をすることを確認

する。

必要とするジッタフィルタを選択し,フィルタ後の出力ジッタを測定し,次いで特定の測定時間間隔で

発生した真のピーク間のジッタの振幅を測定する。

必要とする全てのジッタフィルタで,上記の手順を繰り返す。

19

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図11−出力ジッタ測定

9

システマティックジッタの測定

9.1

使用する機器

測定に必要な機器を,次に示す。

− クロック発生器

− デジタル信号発生器

− 遅延器

− オシロスコープ

9.2

基礎技術

9.2.1

機器の接続

システマティックジッタ測定方法の基礎技術構成を,図12に示す。

注a) 波形評価可能な別の位相検出測定器に置換え可能である。

図12−システマティックジッタ測定方法の構成:基礎技術

被試験

ネットワーク

被試験

機器

周波数

シンセサイザ

(オプション)

デジタル信号

発生器

デジタル

信号

受信器

ジッタ

受信器

ジッタ

測定

フィルタ

電圧計

Peak/

rms

スペクトラム

アナライザ

(オプション)

クロック

テスト

シーケンス

テスト

シーケンス

フレーム

トリガー

クロック

発生器

デジタル

信号発生器

被測定

試験機器

オシロ

スコープa)

遅延器

トリガー

入力

20

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

9.2.2

機器設定

ランダム位相雑音を除去するために,64回以上のトレースを平均するようにオシロスコープを設定する。

クロックの立ち上がりエッジとデータ信号のエッジとが,一致するように,位相を調整する(この調整に

よって,オシロスコープの時間軸の非線形性の影響を最小にする。)。クロックエッジとデータ信号エッジ

との時間差(単位はUI)を測定する。測定可能範囲は,±0.5 UIとする。

9.2.3

測定手順

測定手順は,次による。

a) 信号発生器から必要とするパターンのフレーム試験信号を発生する。

b) オシロスコープの3 dB帯域幅が,データレートの0.75倍となる4次ベッセルトムソンフィルタ特性

と等価なものを使用し,データ及びクロック波形を取得する。

c) 64回以上のトレースを平均するようにオシロスコープを設定する。クロックの立ち上がりエッジとデ

ータ信号のエッジとが一致するように,位相を調整する。クロックエッジとデータ信号エッジとの時

間差(単位はUI)を測定する。測定可能範囲は,±0.5 UIとする。パターン依存によって発生する時

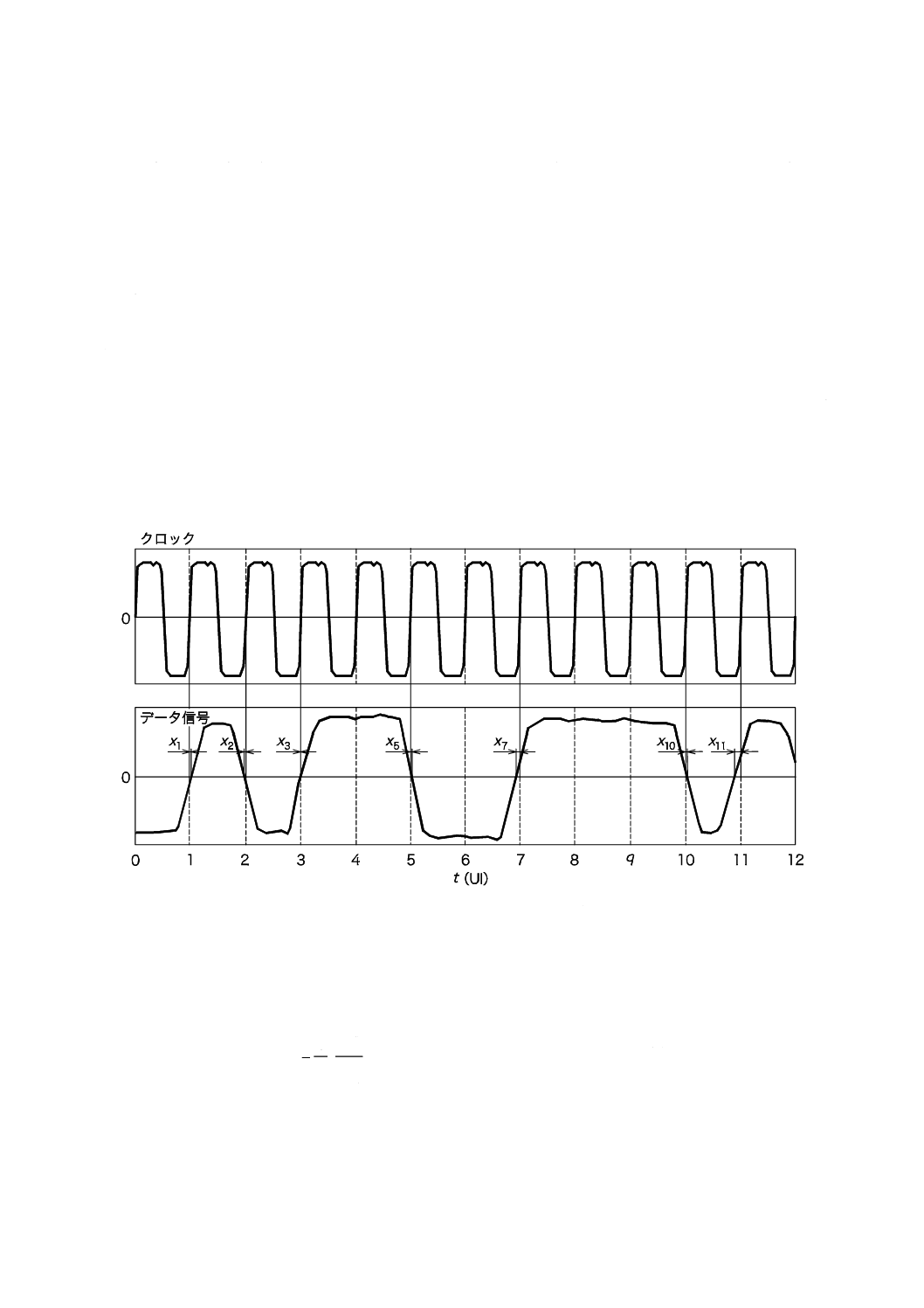

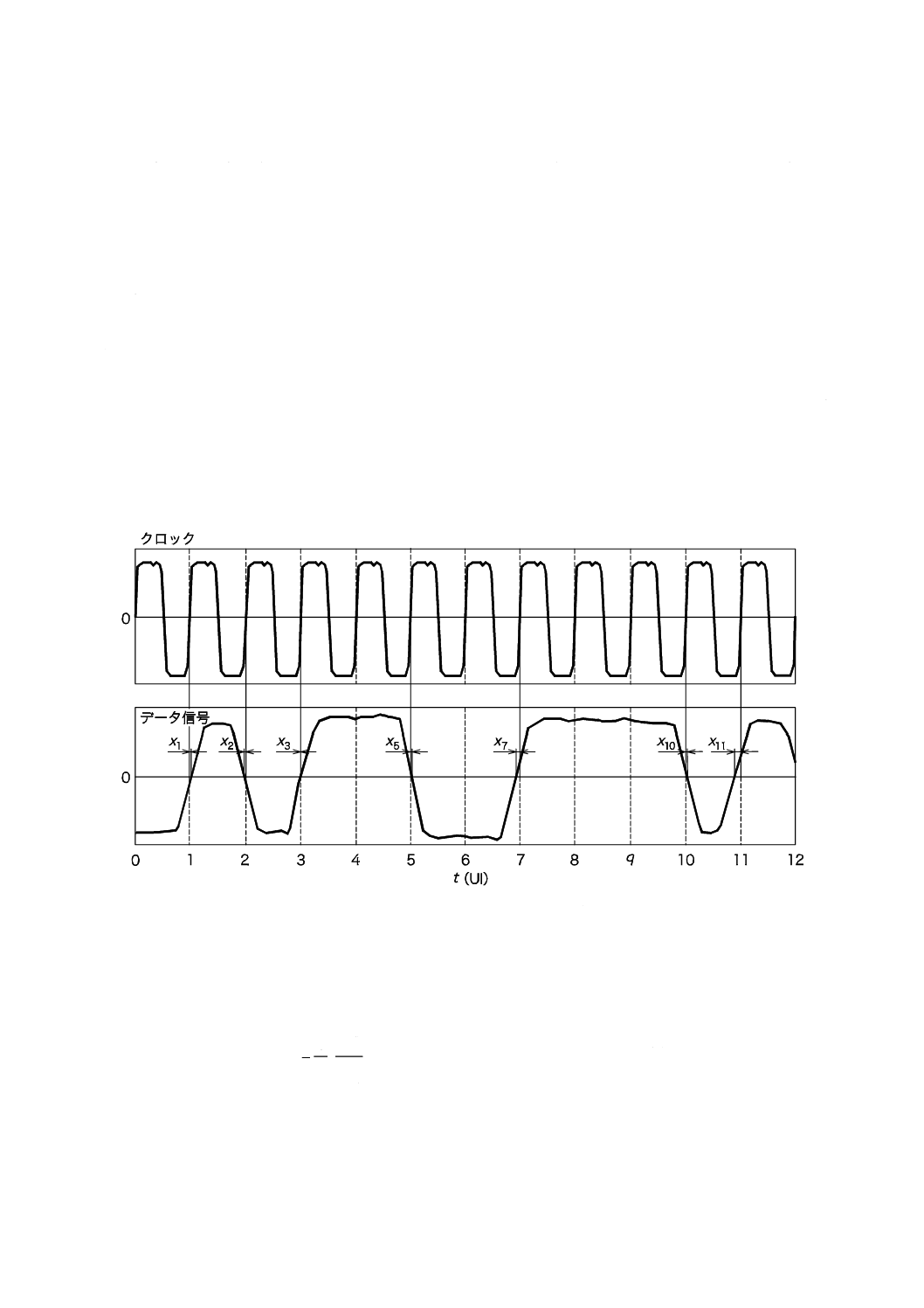

間差xiを,図13に示す。

図13−パターン依存によって発生する時間差xiの測定

d) 特定のiに対するデジタル信号エッジがない場合は,xi=0とする。デジタルフレーム信号の一周期を

含むようにxiを測定し,式(6)又は式(7)を用いて,エッジのない箇所の時間差xiを求める。

∑

∑

=

−

=

−

=

24

1

24

1

'

n

n

i

n

n

i

i

p

x

x

(データ信号長がPRBS 223−1以下の場合) ·················· (6)

21

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

∑

∑

=

−

=

−

=

64

1

64

1

'

n

n

i

n

n

n

i

n

i

p

h

x

h

x

(データ信号長がPRBS 231−1の場合) ······················ (7)

ここに,

pi: パターン密度情報

pi=1(データエッジがある場合)

pi=0(データエッジがない場合)

hn: カットオフ周波数0.032 foのLPF係数

fo:データレート

xiの実測値がない場合は,x'iの値を代わりに使う。

e) 数列xiを,適切な高域通過フィルタ及び低域通過フィルタで数学的にフィルタリングし,パターン依

存ジッタ数列yiを求める。

10

BERTスキャン法の測定

10.1 一般事項

ジッタは,ビット誤り率の劣化をもたらす一般的な根本原因と考えられる。一般的なシステムでは,ビ

ット誤り率性能は受信した1兆ビット当たり1ビット(1E-12)未満となるため,同程度の確率に対してジ

ッタの特性評価を行うことが重要である。こうすることによって,全体のビット誤り率性能においてジッ

タの影響を正確に見積もることができる。ジッタの影響を可視化する一つの方法に,アイパターンがある。

アイパターンは,共通の時間軸上にデジタルストリームの全ビットを重ねて表示したものである。信号に

ジッタがない場合,全ての立ち上がりエッジ(0から1への遷移)は理想的な時間位置にあり,信号が相

互に重なっている。立ち下がりエッジ(1から0への遷移)に対しても同様である。データストリームに

ジッタがある場合,アイパターンのデータエッジは,同じ時間位置にはない。早いエッジ及び遅いエッジ

によって,アイパターンは時間軸方向で閉じ始める。

一般的には,理想からの最大偏差をもつエッジは,最も低い確率で発生する。特に,ランダムジッタ成

分があるときには当てはまる。被試験信号を,ビット誤り率試験器(BERT)の誤り検出器に入力し,かつ,

誤り検出器の識別をアイの中心で行うように設定した場合,ジッタが極端に大きくなければ誤りは検出さ

れない。識別点をアイの中心から離した場合,最も大きいジッタを含むビットが,ある論理状態から別の

論理状態に遷移しているときに識別が行われると,誤りが検出される。最も大きいジッタの発生確率は低

いため,このような誤りは一般的に非常に低い頻度で発生する。識別点が中心から離れるにつれて,デー

タ遷移の前に,より頻繁に識別が行われるようになるため,誤りの可能性は増える。ビット誤り率を識別

回路の時間位置の関数として記録する場合,これは単位間隔又はビット周期にわたって変化するため,ジ

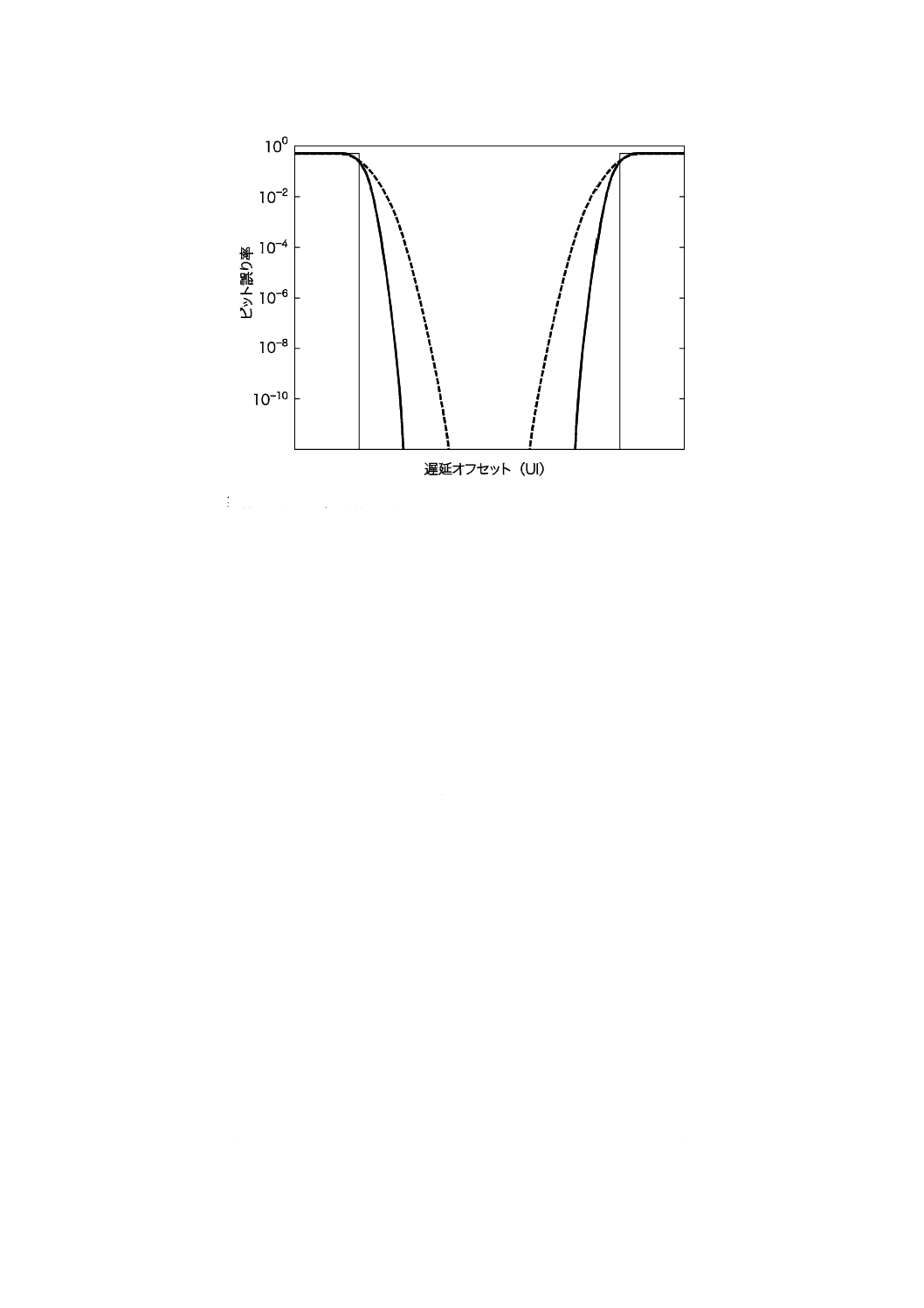

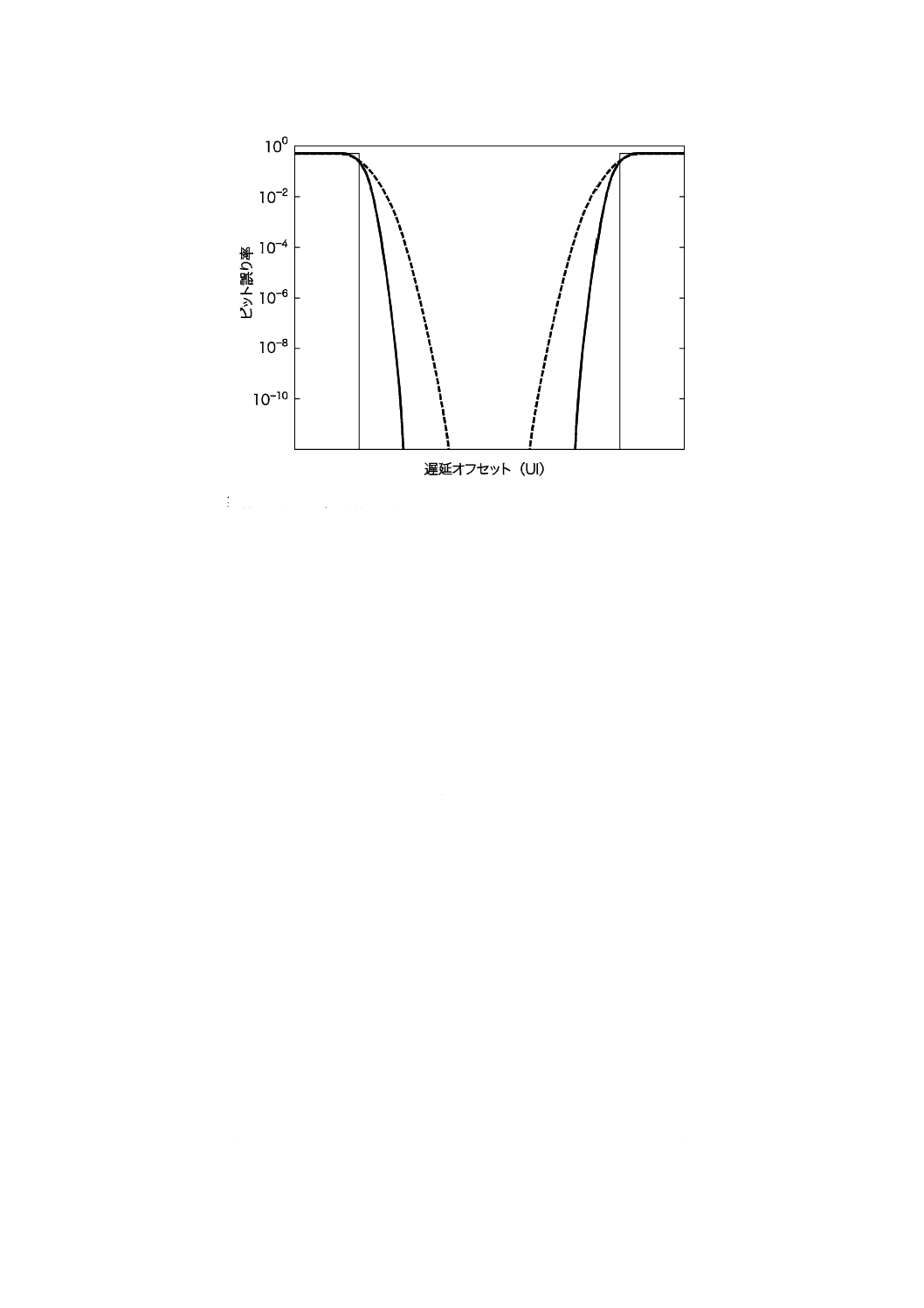

ッタの累積分布関数を図示できる。これを,一般にジッタバスタブ曲線と呼ぶ(図14参照)。単位間隔の

中心においては,誤りの確率(それは,ジッタのあるエッジが発生する確率を表す。)は極端に小さくなり,

測定することができない。中心から離れた位置では,ビット誤り率が増えるため,バスタブに似た形とな

る。

22

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

実線はジッタ小,破線はジッタ大

図14−ジッタバスタブ曲線

この方法によって,一兆回に一回(又はそれ以下)の割合で発生するエッジ位置のような,極端に低い

水準までジッタ確率を直接測定することができる。ただし,このような低い確率までジッタを評価しよう

とするとき,何兆ビットも観察しなければならない。いかなる時間位置に対する誤り率も,有意の数の誤

りが測定されるまでは正確に決定できないため,測定に長い時間を要する。アイパターンのエッジ付近を

測定する時間は短くなるが,アイパターンの中心領域を測定する時間は長くなる。

10.2 使用する機器

測定に必要な機器を,次に示す。

− 誤り率検出器

− 理想的なジッタ性能をもつクロック信号源(例 クロック抽出及び可変遅延器)

10.3 基礎技術

10.3.1 機器の接続

被測定信号を,誤り率検出器のデータ端子に入力する。理想的なクロック信号を,誤り率検出器のクロ

ック端子に入力する。

10.3.2 機器設定

誤り率検出器は,振幅及び時間において,データのアイパターンの内部で理想的なサンプリングポイン

トを識別するように設定する。クロック信号は,誤り検出器の識別を行う基準となる。全てのジッタは,

この基準に対して測定する。クロック信号にジッタがなく,データストリームに同期している場合,測定

したジッタは信号のタイミング偏差を全て含んでいる。対照的に,クロック信号が,あるクロック抽出装

置を通してデータストリームから得たものである場合,クロック信号及びデータストリームの両方に共通

するジッタは,BERTスキャン法では測定できない(図15参照)。測定されるジッタ領域は,クロック抽

出装置のジッタ帯域幅を除いたものになる。ジッタ帯域幅は一般的には低域通過の機能になるので,タイ

ミング基準用として抽出クロックを使うことは,一般的には高域通過したのと同じ結果となる。したがっ

て,クロック抽出装置のジッタ帯域幅よりも高域のジッタが測定されることになる。これは,低周波ジッ

23

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

タが小さく,装置の受信器で容易に許容できる場合にあてはまる。

図15−BERTスキャン法のための測定構成

10.3.3 測定手順

誤り率検出器のサンプリングポイントを,理想的な振幅及び時間位置に置き,データパターンに対して

整列した状態で,サンプリングポイントを単位間隔の半分だけ早い時間に調整する。有意の数の誤りを検

出し,ビット誤り率を決定して相対時間に対して記録する。アイの中心に向かって単位間隔の小さな割合

だけサンプリングポイントを増加し,次のビット誤り率及び時間位置のデータ組を記録する。各々の連続

する測定で,ビット誤り率は一般的には減少していく。ビット誤り率が小さすぎて測定できなくなるまで,

又は必要なビット誤り率のしきい値を得るまで(例えば,1E-12以下),手順を繰り返す。次にサンプリン

グポイントを理想的なサンプリング時間よりも単位間隔の半分だけ遅く設定する。ビット誤り率を決定し,

サンプリングポイントをアイの中心方向へ減少させていくことを除いて,上の手順を繰り返す。

試験時間を短縮するために,低いビット誤り率は,高いビット誤り率の測定値から外挿してもよい。

11

ジッタ分離手法の測定

11.1

一般事項

極端に低い確率の事象を捕捉するために信号性能を直接評価するには,非常に大きな測定母集団を伴い,

大変長い測定時間を伴う(箇条10参照)。ジッタは,様々な確率分布をもつ原因によって生じるため,時

間効率を上げるために少ないデータ数で推定を行うと,大きな測定誤差を生じる。ジッタ分離手法は,直

接測定するような長い時間をかけることなく,非常に低い確率の事象を含め,全ジッタの正確な評価を行

うことができる手法である。この手法の基本原理は,まず,高い確率のジッタ成分を直接測定し,そこか

ら低い確率のジッタ成分の分布を正確に見積もる。それらによって,集合体の分布を見積もり,ジッタの

広がりを必要とする確率まで予測して,様々な要素を使ったモデルを構成する。

ジッタ分離の現実的な手法としては,繰返しパターンをもつ試験信号を使う。パターンの各エッジの平

均位置を決定し,その期待される位置と比較する。これは,データ依存又は相関ジッタに相当する。パタ

ーンの何らかの特定のエッジを観察し,エッジ位置の分布を決定することで,無相関ジッタを得る。これ

は,データパターンの位置に無関係なランダムジッタ及び周期ジッタを含む。言い換えれば,このジッタ

は,パターンが繰り返されてエッジが何度も観察されるとき,いずれのエッジにも同様に現れる。周期的

な無相関ジッタは,有限の分布をもつ。すなわち,振幅には限度がある。真にランダムのジッタは,有限

ではない。それは,一般的に,システムの物理的な限界の範囲内で,無限に広がるガウス分布をもつ。し

たがって,その分布は,標準偏差によって正確に記載できる。

ランダムジッタの標準偏差を決定するために,周期的な無相関ジッタを分離しなければならない。周波

数領域で無相関ジッタの母集団を調査し,後処理又は無相関ジッタの母集団の曲線フィッティングによっ

被試験

機器

誤り率

検出器

可変

遅延器

クロック

抽出

24

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

て周期的なスペクトルを除去するなど,様々な手法が用いられる。

仮に装置のジッタの集合が完全にランダムである場合,ジッタ母集団の特性を評価して標準偏差を決定

すれば,低い確率の事象を含む全ジッタを見積もることができる。特定の確率水準までジッタを決定する

ために,標準偏差を適切に乗算する。例えば,10−12の確率までジッタ振幅を決定するためには,標準偏差

をおよそ14倍する。このため,ランダムジッタの標準偏差を正確に求めることが必要である。一般的に,

大きな乗数を伴うため,誤差があると全ジッタの見積りが著しく変わる。

ジッタがランダム成分だけから成ることはないので,全ジッタの推定には,全てのジッタ成分を含んだ

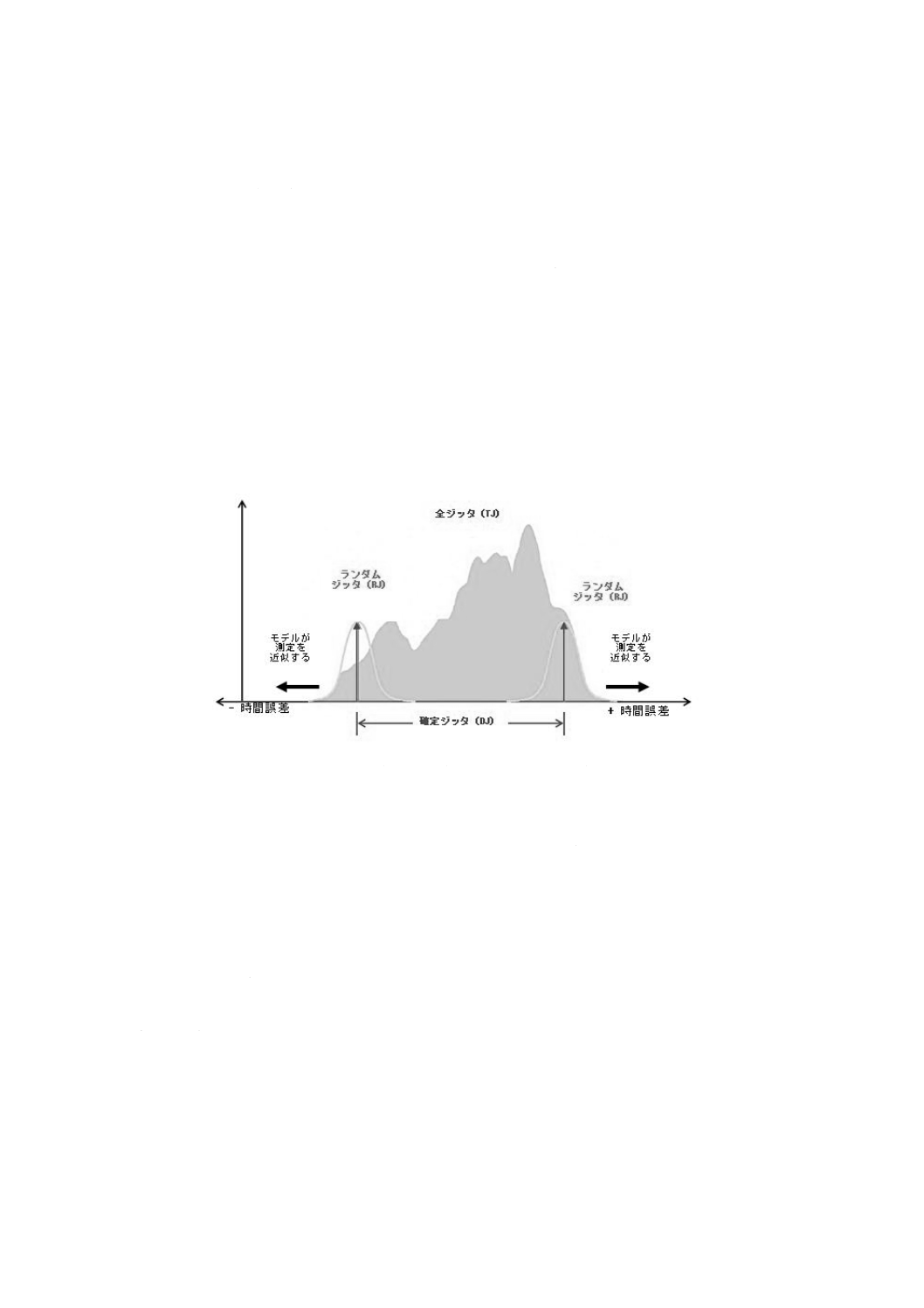

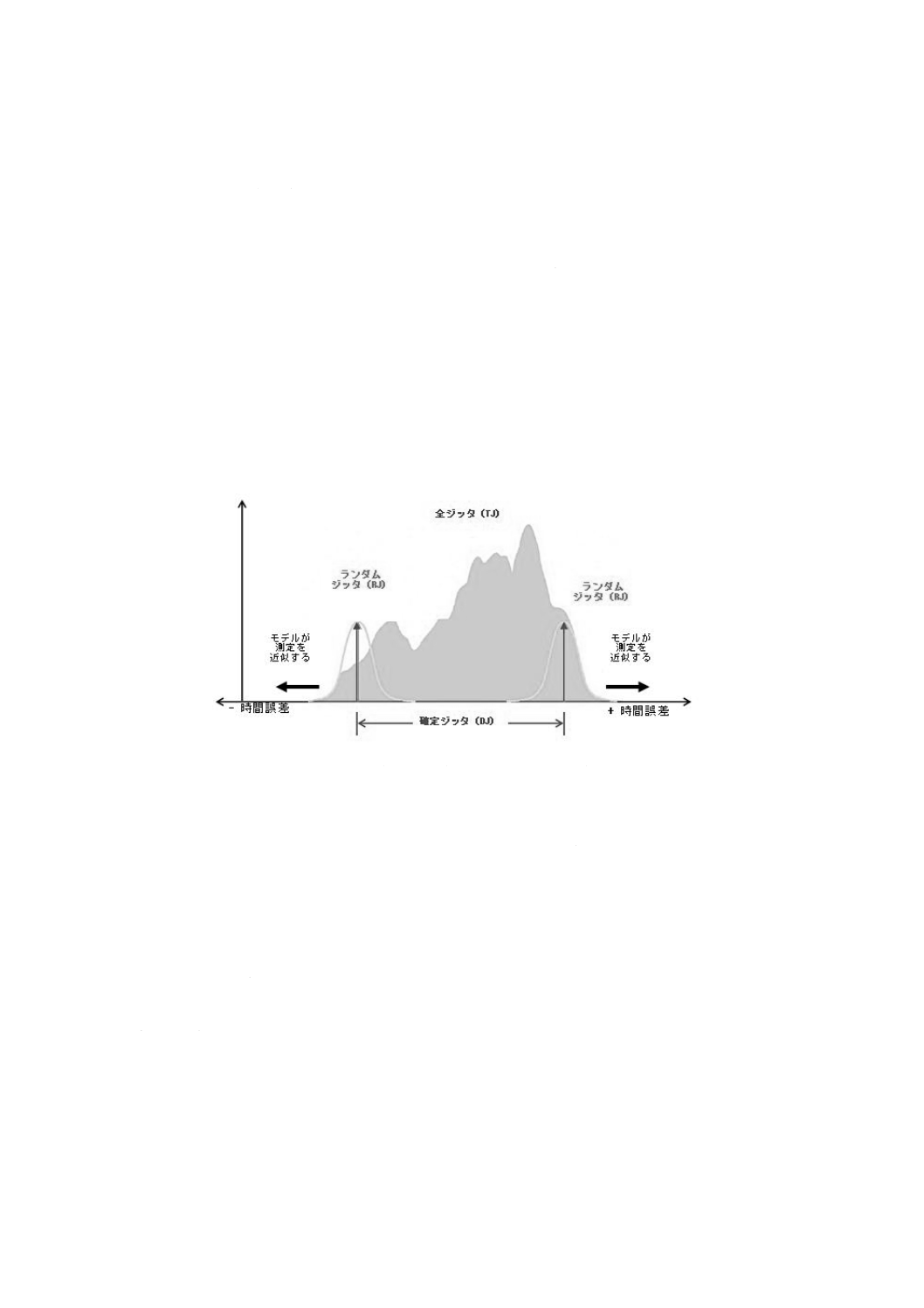

解析を必要とする。一般的なアプローチには,デュアルディラックジッタモデルがある(図16参照)。こ

のアプローチでは,ランダムジッタの標準偏差を決めてから,ランダムジッタ分布を構成する。この分布

を分離し,確定ジッタ成分群の有効な大きさに従って位置を定める。有効な確定ジッタは,確定ジッタ群

の実際の大きさとは一致しないが,それを起点値としてモデル内でランダムジッタと組み合わせることに

よって,全ジッタの最適な推定ができる。

図16−デュアルディラックジッタモデル

モデルを使うことによって,信号の中で発生確率の低い領域まで測定することなしに,ジッタを極端に

低い確率まで推定することができる。正確な測定のためには,ランダムジッタに低確率の周期性ジッタを

含めないようにし,残留ジッタ及びノイズの少ない試験に用いる機器を使用して,正確なモデルを作るた

めに十分な母集団を得る効果的な方法を用いる。

11.2

使用する機器

測定に必要な機器を,次に示す。

− ジッタ受信器(デジタルビットストリームのエッジの時間位置を特定できるオシロスコープ,タイム

インターバルアナライザ,ビット誤り率試験器など)

オプション機器を,次に示す。

− クロック再生器(データエッジの理想的な位置を表すクロック)

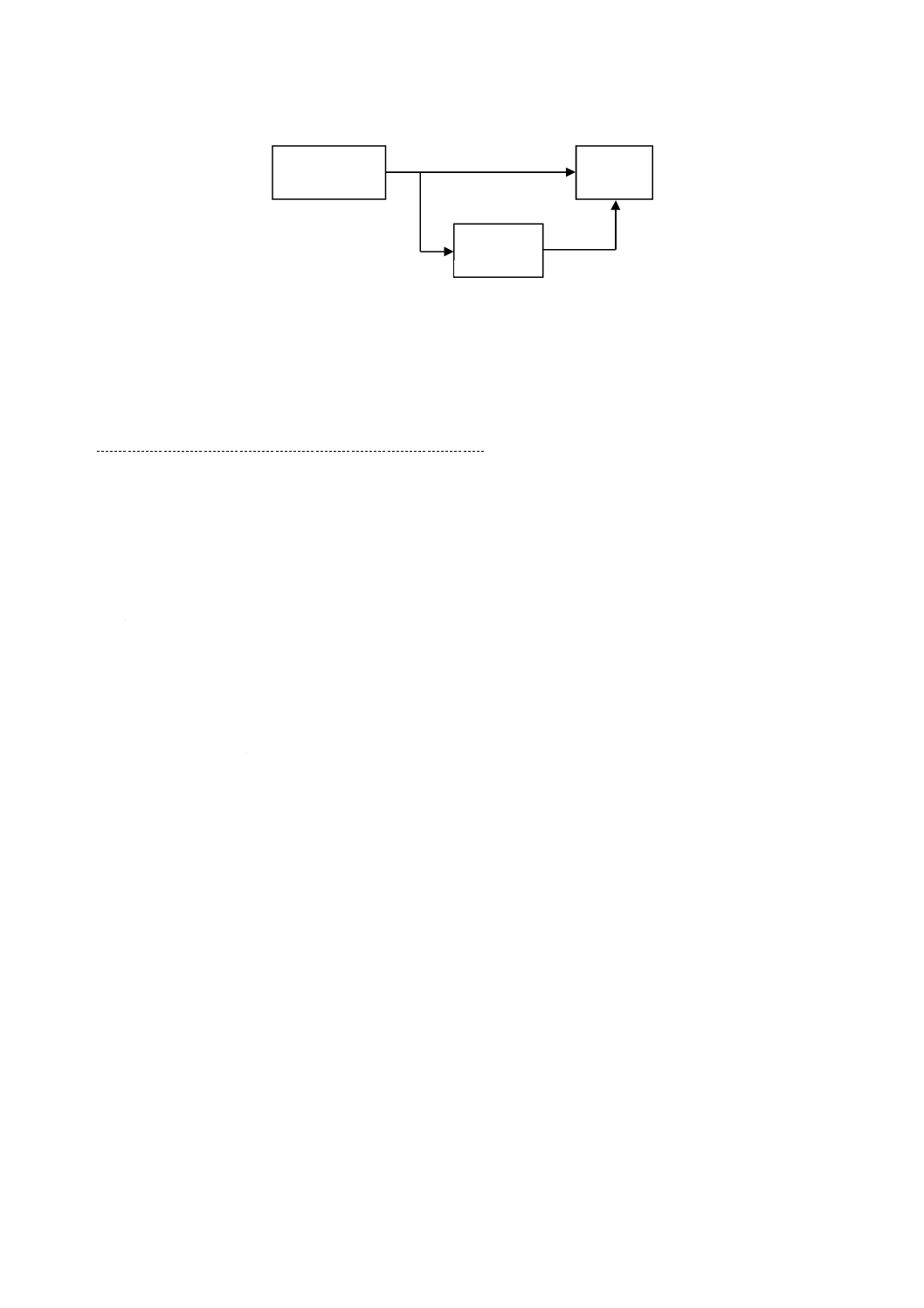

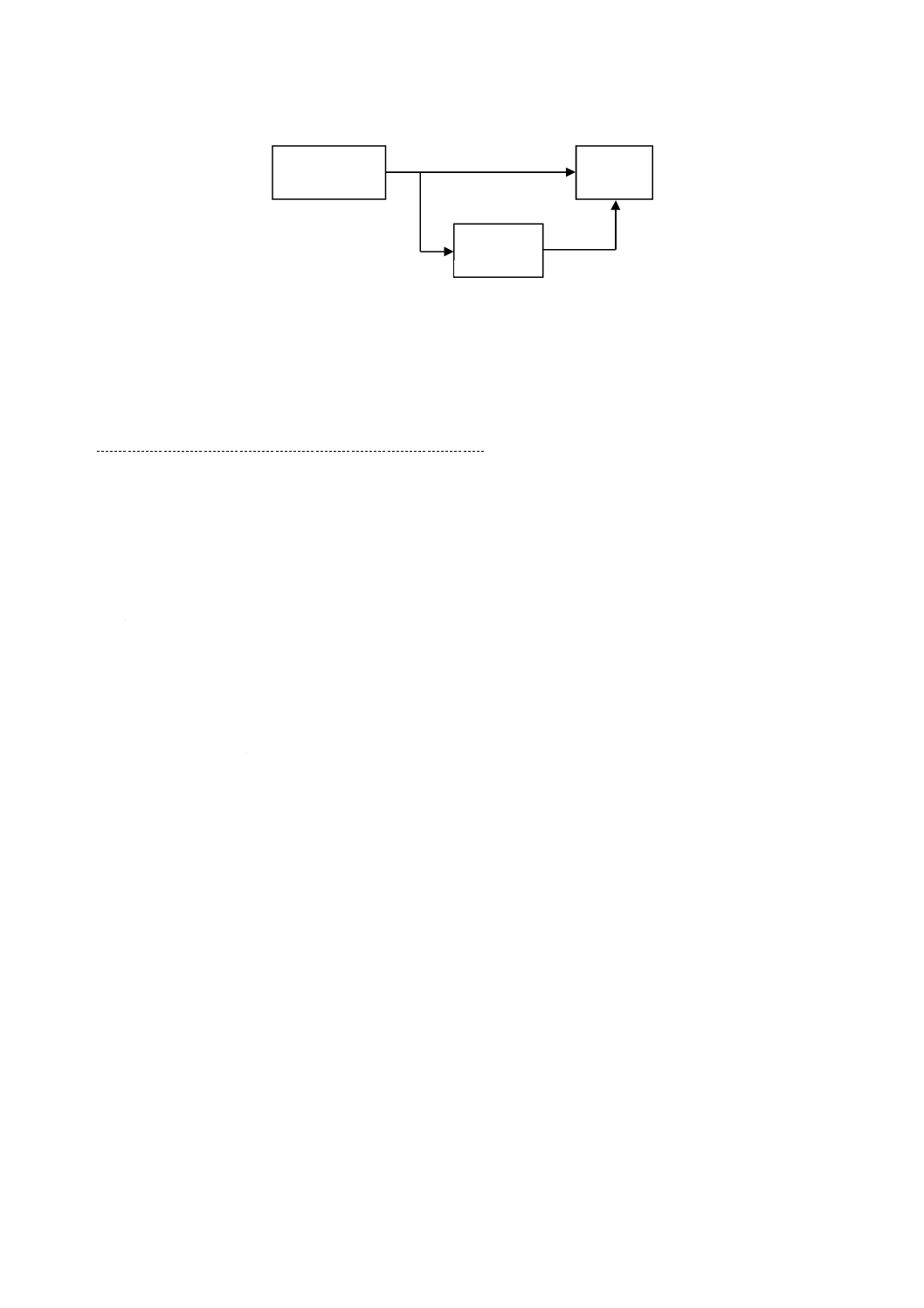

基本的な測定構成を,図17に示す。

25

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図17−ジッタ分離測定のための測定構成

11.3

機器の接続

被試験信号を,エッジ測定機器に出力する。クロック信号も,タイミング基準信号として出力する。ク

ロックは,被試験信号から抽出する場合もある。オプション機器のクロック再生器は,クロックタイミン

グ基準信号を被試験信号から抽出する場合に使用する。

11.4

機器設定

被試験機器は,繰返しデータパターンを発生するように設定する。測定する振幅のしきい値を,信号振

幅の中間レベルに設定する。クロックタイミング基準信号を被試験信号から抽出する場合,クロック抽出

システムのジッタ帯域幅は,測定されるジッタが正しく透過するように設定する(9.2.2参照)。

11.5

測定手順

11.5.1 サンプリングオシロスコープ

データパターンの全てのエッジを,理想的な位置に対する平均位置として記録する。全体の最も早いエ

ッジ位置(理想的な位置に対して)と最も遅いエッジ位置(理想的な位置に対して)との間の時間間隔が,

データ依存性ジッタを表す。パターンのエッジを調査し,理想的な位置に対するエッジ位置の集団を得る

ことによって,無相関ジッタを求める。周波数領域への変換ができるように,周期的にサンプリングする。

周波数領域においては,スペクトルのノイズフロアはランダムジッタを表す。不連続の線スペクトルは,

周期的成分を表す。線スペクトルを除いて,ノイズフロアを積分するとランダムジッタが求まり,更に処

理することで標準偏差が求まる。線スペクトルのエネルギーは,周期ジッタとなる。様々な成分を畳み込

みすることによって,全体の母集団が求まる。再構築されたジッタ母集団に最適となるように,デュアル

ディラックジッタモデルを調整する。このモデルによって,必要とする発生確率に相当する全ジッタを求

めることができる(信号処理の詳細は,この規格では扱わない。)。

11.5.2 リアルタイムオシロスコープ

リアルタイムオシロスコープは,一回の波形取得で全部のデータパターンを取り込むことができる。ジ

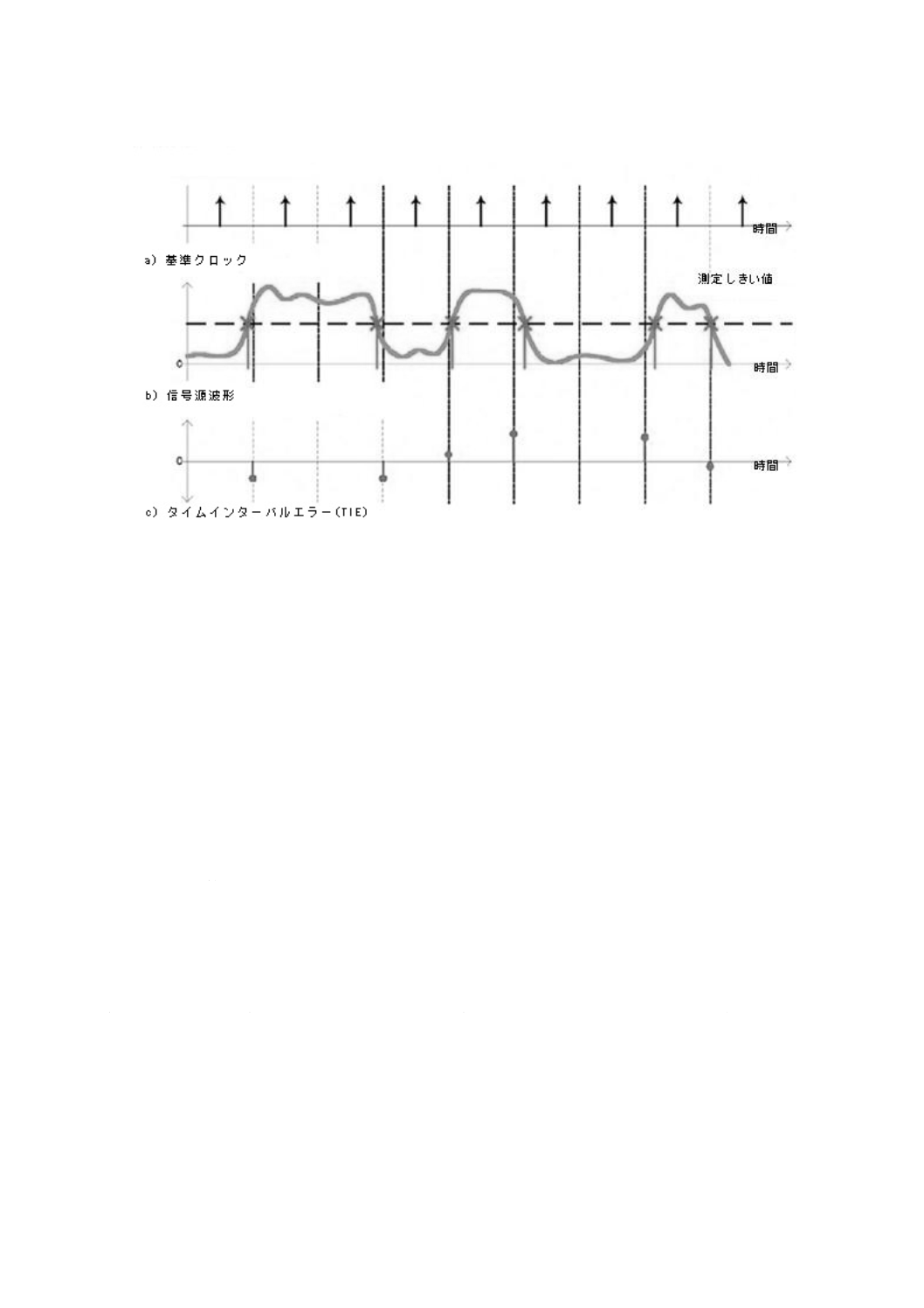

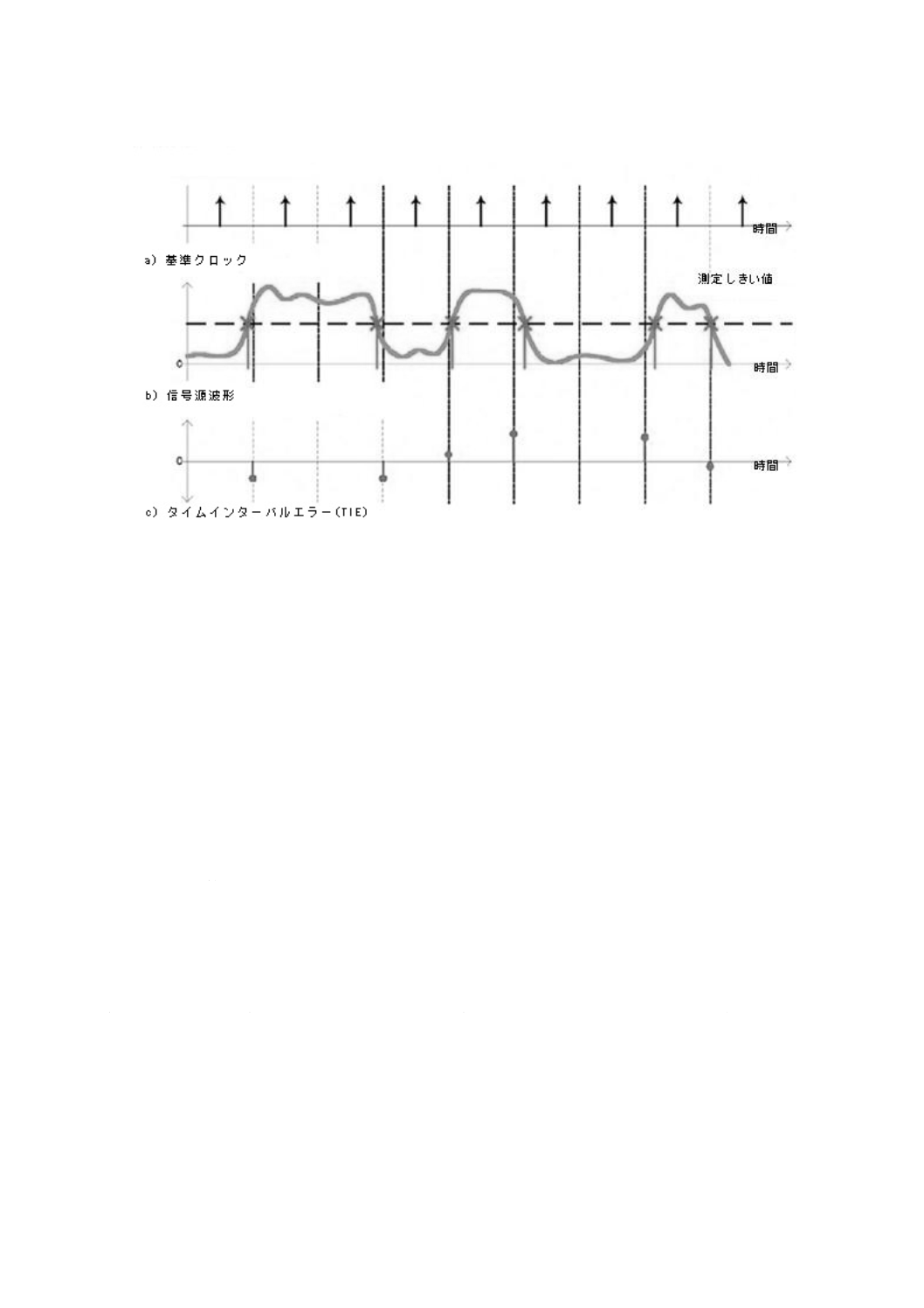

ッタ解析は,特定の基準時間に基づいて,シリアルデータ波形の電圧遷移を時間置換した変化量によって

行う。実質的に,測定処理は,タイムインターバルエラー(TIE)を解析する(図18参照)。TIEは,時間

に対する時間誤差の離散関数である。TIE測定に用いる基準時間(基準クロック)は,幾つもの異なる方

法で定義できる。一般的に,TIE測定に用いられる基準時間の一つとして,入手した波形記録に最も適合

した周波数及び位相をもつ一定周波方形波がある。基準クロック信号のような,第二の信号源の電圧遷移

を基準時間として用いる場合もある。

被試験機器

ジッタ

受信器

クロック

再生器

(オプション)

26

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図18−タイムインターバルエラーの測定

データパターンに相関のあるジッタを分離するために,ジッタのTIE関数を最初に計算し,各TIE値と,

信号源波形の論理的なビットシーケンスの特定のビットとを結びつけて,解析する。この解析は,信号源

波形から論理的なビットシーケンスを抽出し,その周期パターンのビット長を決めて行う。次に,元のTIE

関数を,サブサンプルのTIE関数群に分割する。ここで,各サブサンプルのTIE関数の値は,全てパター

ンの特定のビットに対応する。

これらの各サブサンプルのTIE関数を,高速フーリエ変換(FFT)を使って周波数領域に変換する。各

ジッタスペクトルの最初の値(DC成分)は,繰返しビットパターンの特定ビットに対するデータ依存性

ジッタ(DDJ)に等しいので,DDJはジッタから分離できる。

一旦全てのジッタ(TJ)スペクトルからDDJを取り除くと,残りのジッタスペクトルは,主にランダム

ジッタ(RJ)及び周期性ジッタ(PJ)から成る。RJからPJを分離するためには,まず,残ったRJ及び

PJスペクトルの全てのパワースペクトル密度(PSD)を計算する。次に,個々のRJ及びPJスペクトルの

全ての平均を計算し(以前に取得したスペクトル平均と同様に),APSD(平均PSD)を求める。この時点

で,PJを含んでいる可能性があるので,著しく大きな振幅をもつAPSDの周波数成分は全て除去される。

次に,APSDの残りの周波数成分を結合して,RJのRMS値を得る。

デュアルディラックジッタモデルに基づく確定ジッタ[DJ(d-d)]及び周期性ジッタ[PJ(d-d)]は,デュ

アルディラックジッタモデルを測定ヒストグラムにフィッティングすることによって決定する。デュアル

ディラックジッタモデルは,ガウシアン成分及び二峰性の成分に対して同時に解くなど,多くの方法を用

いて,確率密度関数(PDF)にフィッティングできる。一旦モデルが構成されれば,事象の必要とする確

率まで全ジッタの値を得ることができる。

12

ワンダの測定

12.1 使用する機器

27

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

測定に必要な機器を,次に示す。

− 基準クロック発生器

− デジタル信号発生器

− ワンダ受信器

12.2 基礎技術

12.2.1 機器の接続

12.2.1.0A 一般事項

評価する位相変動の周波数が低いために(3.21参照),ワンダ測定には特殊な測定構成を必要とする。ジ

ッタを測定するとき,必要な基準タイミング信号は,試験に用いる機器の中の位相同期ループ(PLL)に

よって,測定される信号の平均位相から得られる。このようなPLLでは,ワンダ測定の要求事項に適合し

ない。

したがって,ワンダ測定には,十分に安定な外部の基準クロック信号が常に必要である。

12.2.1.1 同期信号のワンダ測定

同期信号のワンダ測定のための測定構成を,図19に示す。

図19−同期信号のワンダ測定構成

測定に必要なタイミング信号を共通の基準クロックから得ることができる場合,この構成が適用でき,

被試験機器の入力端子及び出力端子を同じ場所で利用できる。そのため,この方法だけがループ測定でき

る。この設定では,基準クロックの位相変動は測定結果に影響しない。したがって,基準クロックの安定

性の要求事項はそれほど高くなく,携帯用の試験装置でも可能である。

12.2.1.2 非同期信号のワンダ測定

非同期信号のワンダ測定のための測定構成を,図20に示す。この構成は,被試験ネットワーク又は被試

験機器の入力端子及び出力端子の両方が同じ場所で利用できない場合(例えば,遠端測定)のワンダ測定

に適用できる。この設定では,測定に関係する二つのクロックの周波数及び位相ドリフトが,測定結果に

影響する。そのため,二つのクロックの安定性が,測定する量より一桁以上よくなければならない。外部

基準との同期が要求される携帯用の試験に用いる機器は,そのような基準クロックを備えていない場合が

ある。

基準タイミング

テスト

シーケンス

テスト

シーケンス

基準

クロック

発生器

ワンダ

受信器

デジタル

信号発生器

被試験

ネットワーク

又は

被試験機器

28

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図20−非同期信号のワンダ測定構成

12.2.2 機器設定

箇条3で定義した様々なワンダパラメータを計算して推定する場合,TIEの連続情報は実際には得られ

ないため,TIEはサンプルパラメータとして扱う。

TIEの最大のサンプリング時間τ0は,1/30秒とする。

ワンダは,等価的に10 Hzの低域通過フィルタを通して測定し,次の特性をもつものとする。低域通過

フィルタは一次特性で,−20 dB/10倍の遮断特性をもつ。フィルタの−3 dB周波数は,10 Hzとする。

12.2.3 測定手順

測定サンプルは,正常の動作条件で使用され,システムの利用者から観測できる入力及び出力を標準的

にもつ光ファイバ伝送システムの一構成要素でなければならない。被試験ネットワーク又は被試験機器と

しての測定機器のサンプルを,図19及び図20に示す。

13

ワンダTDEV耐力の測定

13.1 目的

この試験の目的は,機器に入力されたときにエラー性能の低下を引き起こすワンダTDEV振幅の耐力を

測定することである。ワンダTDEV耐力は,振幅と適用されたワンダTDEVマスクの積分時間との関数で

ある。

13.2 使用する機器

測定に必要な機器を,次に示す。

− 外部基準クロック源

− ワンダ発生器(TDEV)

− クロック発生器

− デジタル信号発生器

− デジタル信号受信器

ワンダ受信器(TDEV)は,オプション機器とする。

13.3 基礎技術

ワンダTDEV耐力測定のためのエラー発生の評価基準は,2エラー秒を超える累積総計を引き起こすワ

ンダTDEVマスクの最大振幅として定義する。ここでのエラー秒は,ワンダTDEV積分時間測定間隔の

12倍までの期間の合計とする。

13.4 機器の接続

テスト

シーケンス

基準

タイミング

テスト

シーケンス

基準

タイミング

基準

クロック1

被試験

ネットワーク

又は

被試験機器

デジタル

信号発生器

ワンダ

受信器

基準

クロック2

29

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

13.4.0A 一般事項

13.4.1及び13.4.2は,ITU-T Recommendation G.813に準拠したワンダTDEV耐力測定のための試験構成

を示す。

13.4.1 被試験機器の試験信号に対するワンダTDEV耐力測定

被試験機器の試験信号に対するワンダTDEV耐力測定の測定構成を,図21に示す。発生したワンダTDEV

の振幅を確かめるために,オプションのワンダ受信器(TDEV)を使用する。

図21−被試験機器の試験信号に対するワンダTDEV耐力測定の測定構成

13.4.2 被試験機器の基準タイミング信号に対するワンダTDEV耐力測定

被試験機器の基準タイミング信号に対するワンダTDEV耐力測定の測定構成を,図22に示す。発生し

たワンダTDEVの振幅を確かめるためには,オプションのワンダ受信器(TDEV)を使用する。

図22−被試験機器の基準タイミング信号に対するワンダTDEV耐力測定の測定構成

試験

シーケンス

基準タイミング

ワンダ

発生器

(TDEV)

クロック

発生器

被試験

機器

外部基準

クロック源

雑音源

デジタル

信号発生器

デジタル

信号受信器

ワンダ受信器

(TDEV)

(オプション)

試験

シーケンス

基準

タイミング

基準タイミング

ワンダ

発生器

(TDEV)

クロック

発生器

被試験

機器

外部基準

クロック源

ノイズ源

デジタル

信号発生器

デジタル

信号受信器

ワンダ受信器

(TDEV)

(オプション)

30

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

13.5 機器設定

この手法は,測定間隔に対するTDEVの積分時間を設定し,満足できるエラー発生の評価基準となる試

験信号のワンダTDEV振幅を決定する。この手法に必要な条件を,次に示す。

a) ワンダTDEV振幅を変化させているときは,エラーのない動作が途絶えるため,測定しない。

b) ワンダTDEV振幅を少しずつ増加させながら,TDEV積分時間の12倍継続して,エラー秒を測定す

る。

c) 累積で2エラー秒以下となる最大のワンダTDEVマスクを,決定する。

13.6 測定手順

測定手順は,次による。

a) 機器を,図21又は図22に示すように接続する。適度に連続して,エラーのない動作をすることを確

かめる。

b) ワンダTDEVの振幅を,0 nsに初期化設定する。

c) ワンダTDEV振幅を,個別規格に規定するTDEVマスクに設定する。

d) TDEV測定間隔の積分時間の12倍の間に起こるエラー秒数を記録する。測定前に,エラーのない状態

であることを確認する。

e) エラー発生基準を超えるまで,ワンダTDEV振幅を細かく増加させ,d) を繰り返す。

f)

表示されたワンダTDEVを記録し,ワンダTDEV耐力曲線を描く。

14

ワンダTDEV伝達の測定

14.1 使用する機器

測定に必要な機器を,次に示す。

− 外部基準クロック源

− ワンダ発生器(TDEV)

− クロック発生器

− デジタル信号発生器

− ワンダ受信器(TDEV)

14.2 機器の接続

14.2.0A 一般事項

14.2.1及び14.2.2は,ITU-T Recommendation G.813に準拠したワンダTDEV伝達測定のための測定構成

を示す。

14.2.1 被試験機器の試験信号に対するワンダTDEV伝達測定

被試験機器の試験信号に対するワンダTDEV伝達測定の測定構成を,図23に示す。

31

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

図23−被試験機器の試験信号に対するワンダTDEV伝達測定の測定構成

14.2.2 被試験機器の基準タイミング信号に対するワンダTDEV伝達測定

被試験機器の基準タイミング信号に対するワンダTDEV伝達測定の構成を,図24に示す。

図24−被試験機器の基準タイミング信号に対するワンダTDEV伝達測定の構成

14.3 機器設定

規定の積分時間範囲にわたって,適度なワンダ振幅を設定する。ワンダ振幅は,十分な測定精度を保証

するために十分大きくし,かつ,線形動作を保つように設定するのがよい。

14.4 測定手順

測定手順は,次による。

a) 被試験機器のワンダTDEV耐力測定は,TDEV測定間隔の積分時間の12倍よりも長く行う。

b) 機器を,図23又は図24に示すように,被試験機器をう(迂)回して接続する。適度に連続して,線

形動作及びエラーのない動作をすることを確かめる。

c) 特定の積分時間範囲よりも長く,特定のワンダTDEVマスクを設定する。

試験

シーケンス

基準タイミング

校正用

う(迂)回

ワンダ

発生器

(TDEV)

クロック

発生器

被試験

機器

外部基準

クロック源

雑音源

デジタル

信号発生器

ワンダ

受信器

(TDEV)

試験

シーケンス

基準

タイミング

タイミング

リファレンス

校正用

う(迂)回

ワンダ

発生器

(TDEV)

クロック

発生器

被試験

機器

外部基準

クロック源

ノイズ源

デジタル

信号発生器

ワンダ受信器

(TDEV)

32

C 61280-2-3:2013 (IEC 61280-2-3:2009)

2019年7月1日の法改正により名称が変わりました。まえがきを除き,本規格中の「日本工業規格」を「日本産業規格」に読み替えてください。

d) 必要とするTDEVマスクを加えた状態でワンダTDEVを測定し,測定したTDEVの結果と,試験に用

いる機器の基準トレースとして理想的な加算TDEVマスクであるリファレンスTDEVマスクとの間の

差分を記録する。

e) 被試験機器を,図23又は図24に示すように再接続する。適度に連続して,エラーのない動作をする

ことを確認する。

f)

d) と同じように,必要とするTDEVマスクを加算した状態で,ワンダTDEVを測定する。ワンダTDEV

の結果を,被試験機器のワンダTDEV伝達関数として記録する。

g) 被試験機器のワンダTDEV伝達関数の振幅を得るために,全体のワンダTDEV測定結果からリファレ

ンストレース[d)]を差し引く。

15

試験結果

15.1 必須情報

各試験に対して,次の情報を,報告書に記載する。

− 被試験機器の識別情報

− 実施した全試験名称

− 使用した試験方法の識別情報

− 使用した試験手順の識別情報

− 動作条件の記載

− 環境条件の記載

− 試験結果

− 試験日時

15.2 有益な情報

次の情報も,有益な情報であり,報告書に記載することが望ましい。

− 試験に用いた機器の識別情報

− 電気パッチコードの識別情報

− 光パッチコードの識別情報及び特性の詳細

− 測定の不確かさの記載

− 試験に用いた機器の校正の詳細

− 試験者の名前

参考文献

[1] P. Bylinski and D. G. W. Ingram: Digital transmission Systems 2nd Edition

[2] W. R. Bennet: Bell System Technical Journal 1958, 37

[3] C. J. Byrne, B. J. Karafin and D. B. Robinson Jr.: Systematic jitter in a chain of digital regenerators, Bell

System Technical Journal 1963, 42

[4] IEC/TR 61931,Fibre optic−Terminology