C 0508-7:2017 (IEC 61508-7:2010)

(1)

目 次

ページ

序文 ··································································································································· 1

1 適用範囲························································································································· 2

2 引用規格························································································································· 4

3 用語,定義及び略語 ·········································································································· 5

附属書A(参考)E/E/PE安全関連系のための技術及び手法の概要:ランダムハードウェア故障の管理 ·· 6

附属書B(参考)E/E/PE安全関連系のための技術及び手法の概要:決定論的原因故障の回避 ············· 23

附属書C(参考)ソフトウェア安全度を達成するための技術及び手法の概要 ··································· 51

附属書D(参考)既存ソフトウェアのソフトウェア安全度を判定するための確率的アプローチ ·········· 105

附属書E(参考)ASICの設計のための技術及び手法の概要 ························································ 109

附属書F(参考)ソフトウェアライフサイクル各フェーズの特性の定義 ········································ 123

附属書G(参考)安全関連オブジェクト指向ソフトウェアの開発に関する指針······························· 129

参考文献 ··························································································································· 131

C 0508-7:2017 (IEC 61508-7:2010)

(2)

まえがき

この規格は,工業標準化法第14条によって準用する第12条第1項の規定に基づき,一般社団法人日本

電気計測器工業会(JEMIMA)及び一般財団法人日本規格協会(JSA)から,工業標準原案を具して日本工

業規格を改正すべきとの申出があり,日本工業標準調査会の審議を経て,経済産業大臣が改正した日本工

業規格である。これによって,JIS C 0508-7:2000は改正され,この規格に置き換えられた。

この規格は,著作権法で保護対象となっている著作物である。

この規格の一部が,特許権,出願公開後の特許出願又は実用新案権に抵触する可能性があることに注意

を喚起する。経済産業大臣及び日本工業標準調査会は,このような特許権,出願公開後の特許出願及び実

用新案権に関わる確認について,責任はもたない。

JIS C 0508の規格群には,次に示す部編成がある。

JIS C 0508-1 第1部:一般要求事項

JIS C 0508-2 第2部:電気・電子・プログラマブル電子安全関連系に対する要求事項

JIS C 0508-3 第3部:ソフトウェア要求事項

JIS C 0508-4 第4部:用語の定義及び略語

JIS C 0508-5 第5部:安全度水準決定方法の事例

JIS C 0508-6 第6部:第2部及び第3部の適用指針

JIS C 0508-7 第7部:技術及び手法の概観

日本工業規格 JIS

C 0508-7:2017

(IEC 61508-7:2010)

電気・電子・プログラマブル電子安全関連系の

機能安全−第7部:技術及び手法の概観

Functional safety of electrical/electronic/programmable electronic

safety-related systems-Part 7: Overview of techniques and measures

序文

この規格は,2010年に第2版として発行されたIEC 61508-7を基に,技術的内容及び構成を変更するこ

となく作成した日本工業規格である。

なお,この規格で点線の下線を施してある参考事項は,対応国際規格にはない事項である。

電気及び/又は電子の要素から成るシステムは,その適用分野において,安全機能を果たすために長年

用いられてきた。一般に,プログラマブル電子系(以下,PE系という。)と呼ばれるコンピュータを用い

たシステムは,あらゆる適用分野で,安全以外の機能を達成するために用いられているが,次第に安全機

能の履行にも用いられるようになった。コンピュータシステムの技術が,効果的,かつ,安全に活用され

るためには,意思決定を行うための安全の考え方に関する十分な手引書が必須である。

JIS C 0508(IEC 61508)規格群(以下,この規格群という。)では,電気・電子・プログラマブル電子

(以下,E/E/PEという。)の要素から成るシステムが,安全機能を履行するための全ての安全ライフサイ

クル業務に対する包括的な扱い方について規定している。この統一された扱い方は,全ての電気的な安全

関連系にわたって,合理的かつ整合性がある技術指針を展開するためのものである。主な目的の一つは,

この規格群を基本とした適用分野の製品規格などの制定を容易にし,促進することである。

注記1 この規格群を基本とした適用分野の製品規格などの事例を,参考文献(JIS B 9961,JIS C 0511

及びIEC 61800-5-2)に示す。

多くの状況下では,安全性は,幾つかのシステムによって達成され,複数の技術(例 機械,液圧,空

気圧,E/E/PE技術)に依存している。したがって,いかなる安全対策においても,個々のシステムの要素

(例 センサ,制御機器,アクチュエータ)だけでなく,全システムを構成する全ての安全関連系を考慮

しなければならない。このため,この規格群は,一義的にはE/E/PE安全関連系を対象とするが,更にその

他の技術を基本とした安全関連系を対象とする安全の枠組みも提供する。

様々な適用分野において,E/E/PE安全関連系を使用した応用は,多岐にわたり,多様な潜在危険及びリ

スクが存在することによって生じる複雑さに対応するものとして認識されている。いかなる適用において

も,要求される安全(達成)手法は,その適用に関わる多数の要因に依存する。この規格群は,包括的で

あるため,今後の適用分野の製品規格などの制定版及び既存規格の改正版において,個々の手法の形成を

可能とする。

この規格群は,次の特徴をもつ。

− 安全機能を遂行するためにE/E/PE系を用いる場合の,最初の概念から,設計,実装,運用及び保全を

2

C 0508-7:2017 (IEC 61508-7:2010)

経て廃却に至る全E/E/PE系及びソフトウェアの安全ライフサイクルフェーズを考慮する。

− 急速に進歩する技術を念頭において作成された枠組みは,将来の展開に対応できる十分な耐力があり,

かつ,包括的である。

− E/E/PE安全関連系に関して,適用分野の製品規格などを開発することを可能とする。この規格群の枠

組み内で適用分野の製品規格などを開発することによって,適用分野内及び適用分野間の一貫性(例

基礎となる原理・原則,用語などの整合性)を高水準に導く。これは,安全上,かつ,経済上有益で

ある。

− E/E/PE安全関連系に対して要求される機能安全の達成に必要な安全要求仕様を開発する方法論を提

供する。

− 安全度に関わる要求事項の決定に際して,リスクを基本とした方法論を適用する。

− E/E/PE安全関連系によって実装された安全機能に対して,安全度の目標水準を特定するための安全度

水準を導入する。

注記2 この規格群は,いかなる安全機能についても安全度水準に対する要求事項を規定すること

はなく,また,安全度水準を決定する方法についても規定することはない。この規格群は,

むしろ,リスクに基づいた概念的枠組み及び技術の事例を提供するものである。

− E/E/PE安全関連系が実現する安全度水準に対応した目標機能失敗尺度を設定する。

− 単一のE/E/PE安全関連系が実現する安全機能に対して,目標機能失敗尺度の最小値を設定する。これ

らは,運用モードに応じて次による。

・ 低頻度作動要求モードの場合,作動要求時の危険側機能失敗時間平均確率(PFDavg)を10−5に設定

する。

・ 高頻度作動要求モード又は連続モードの場合,単位時間当たりの時間平均危険側故障頻度(PFH)

を10−9(1/h)に設定する。

注記3 単一のE/E/PE安全関連系とは,必ずしも単一チャネル構成を意味するものではない。

注記4 複雑でないシステムについては,目標安全度をより小さな値で安全関連系の設計をするこ

とが可能であるが,これらの限界値は,現時点で比較的複雑なシステム(例 プログラマ

ブル安全関連系)に対して達成できるものを表しているものとみなされている。

− 産業活動で得られた実際の経験に基づく専門的経験及び判断に基づいた決定論的原因フォールトの,

回避及び制御を設定する。決定論的原因故障の発生確率は一般的に数値化はできないが,安全機能に

関連した目標機能失敗尺度は,この規格に規定する要求事項を全て満たしている場合は,達成してい

るとみなしてもよい。

− 決定論的安全度が,特定の安全度水準の要求事項に適合する信頼に対応する要素を提供する,決定論

的対応能力を導入する。

− E/E/PE安全関連系に対して,機能安全を達成するために多岐にわたる原理,技術及び手法を適用する

が,“フェールセーフ”の概念は明示的には使用しない。ただし,“フェールセーフ”及び“固有(本

質)安全”の原理は,この規格の関連する要求事項に適合することを条件として適用してもよい。

1

適用範囲

1.1

この規格は,附属書A〜附属書Gによって,JIS C 0508-2及びJIS C 0508-3に関連する様々な安全

技術及び手法についての概観を示す。

注記1 これらの附属書は,それぞれ次の事項について記載している。

3

C 0508-7:2017 (IEC 61508-7:2010)

− 附属書A JIS C 0508-2に規定するE/E/PE安全関連系のための技術及び手法のうち,ラ

ンダムハードウェア故障を管理するための事項

− 附属書B JIS C 0508-2及びJIS C 0508-3に規定するE/E/PE安全関連系のための技術及

び手法のうち,決定論的原因故障を回避するための事項

− 附属書C JIS C 0508-3に規定するE/E/PE安全関連系のための技術及び手法のうち,ソ

フトウェア安全度を達成するための事項

− 附属書D JIS C 0508-3に規定するE/E/PE安全関連系のための技術及び手法のうち,既

存ソフトウェアのソフトウェア安全度を判定するための確率的アプローチ

− 附属書E JIS C 0508-2に規定するE/E/PE安全関連系のための技術及び手法のうち,

ASICの設計のための事項

− 附属書F JIS C 0508-3に規定するE/E/PE安全関連系のための技術及び手法における,

ソフトウェアライフサイクル各フェーズの特性の定義

− 附属書G JIS C 0508-3に規定するE/E/PE安全関連系のための技術及び手法における,

安全関連オブジェクト指向ソフトウェアの開発に関する指針

各細分箇条に記載する参考文献は,方法及びツールに関する基本的な参考文献又は例としてみなすこと

が望ましく,最新技術を表していない場合もある。

1.2

JIS C 0508-1,JIS C 0508-2,JIS C 0508-3及びJIS C 0508-4は,基本安全規格であるが,低複雑度

E/E/PE安全関連系(JIS C 0508-4の3.4.3参照)には適用しない。これらの規格は基本安全規格として,各

専門委員会がIEC Guide 104及びISO/IEC Guide 51に記載する原則に従った規格の作成において用いるこ

とを意図している。さらに,これらの規格は,独立した規格として用いることも意図している。ただし,

この規格の横断的安全機能は,IEC 60601の規格群を適用する医用機器には適用しない。

1.3

適用可能な場合,規格の作成において基本安全規格を活用することは,各専門委員会の責務である。

したがって,専門委員会が作成する規格に具体的に引用されているか,又は含まれていない場合は,これ

らの基本安全規格の要求事項,テスト方法若しくはテスト条件は適用しない。

1.4

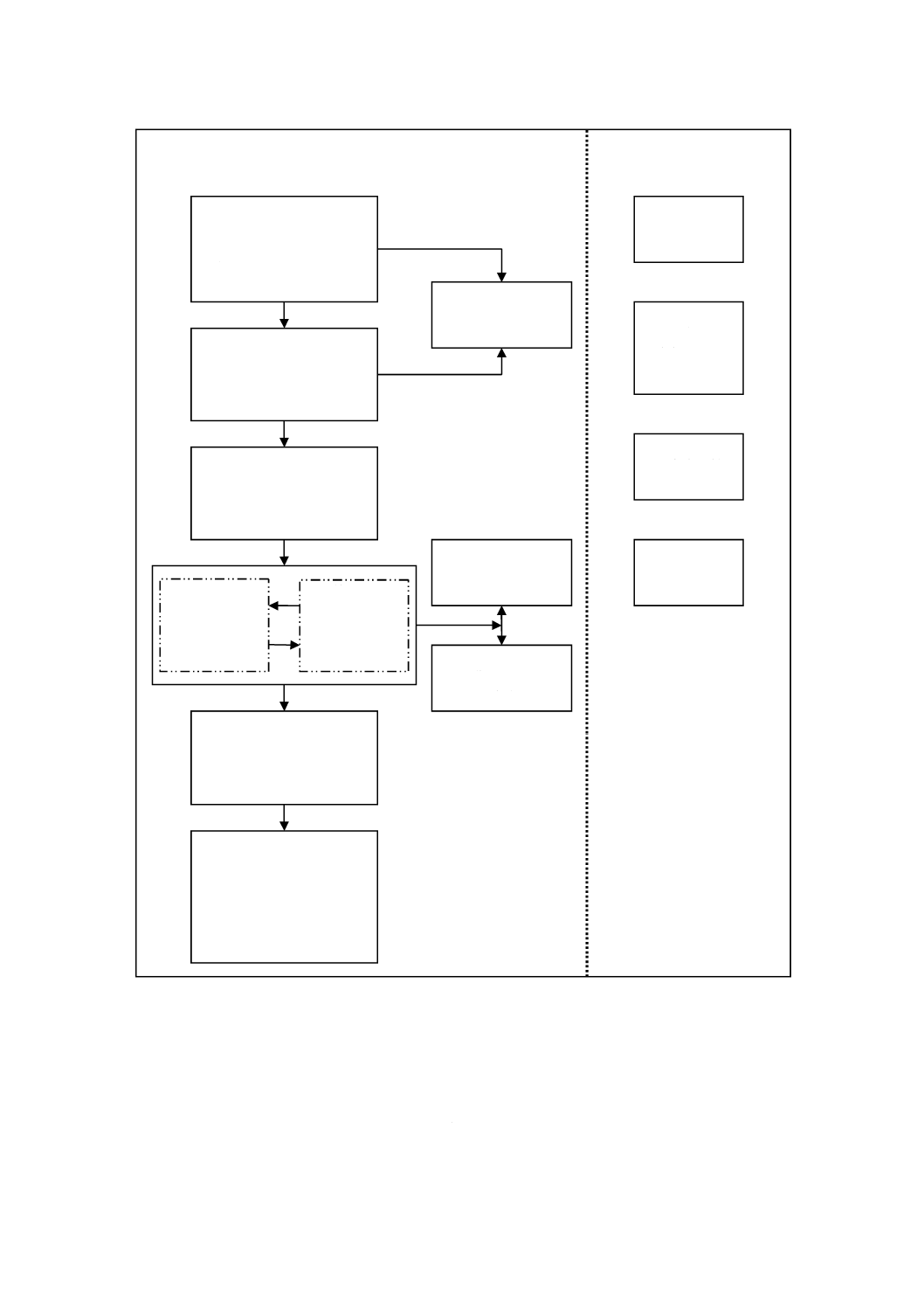

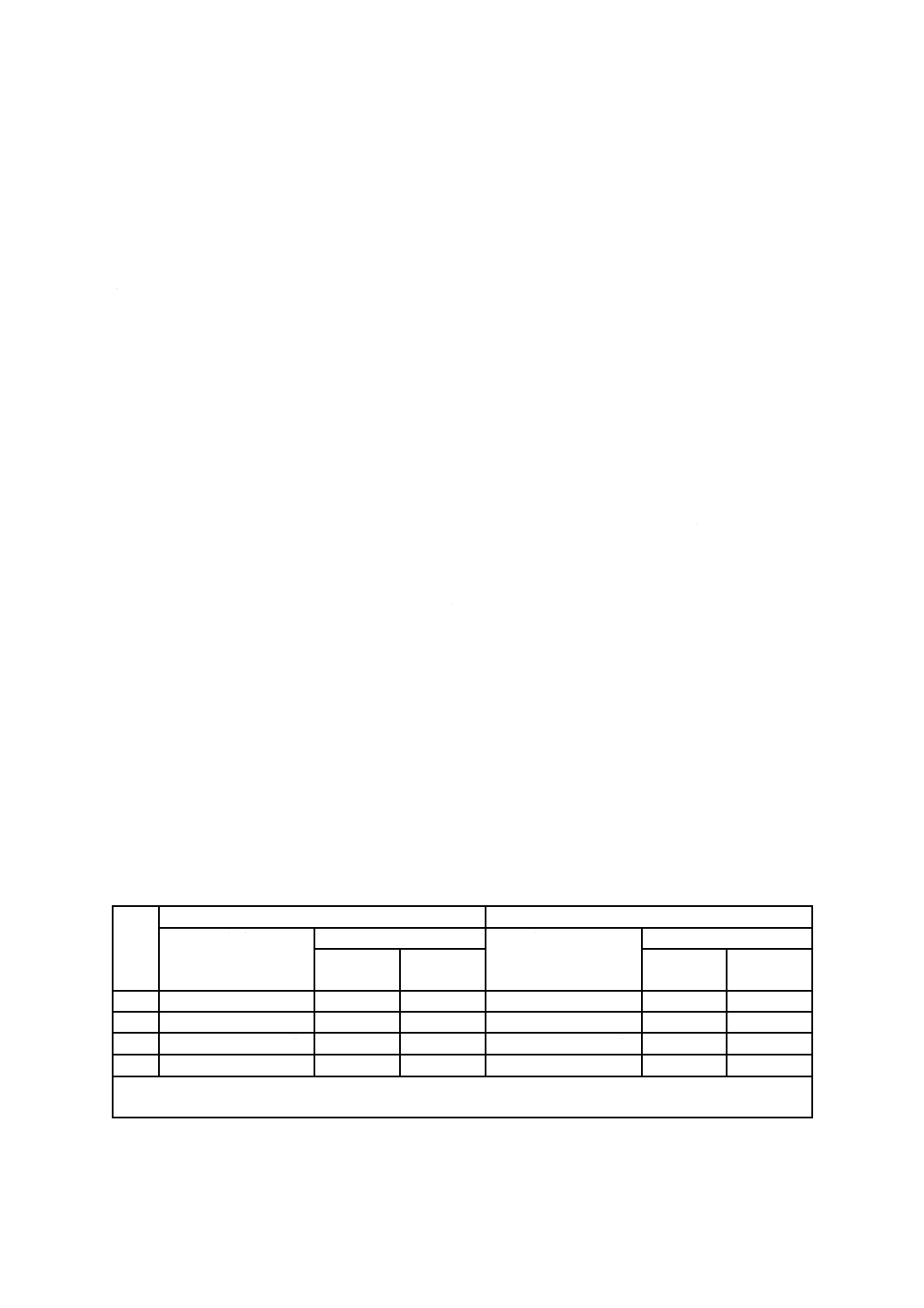

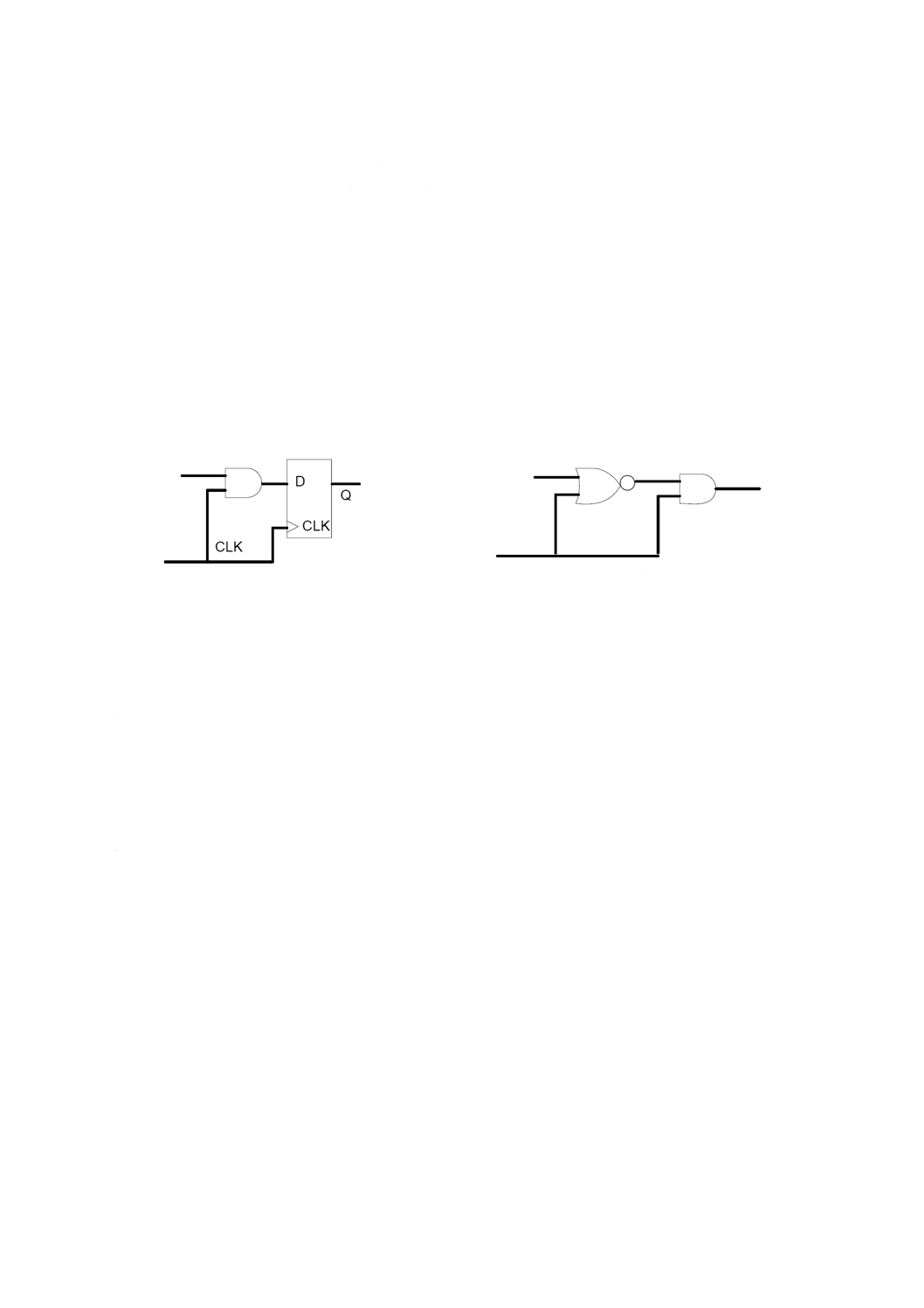

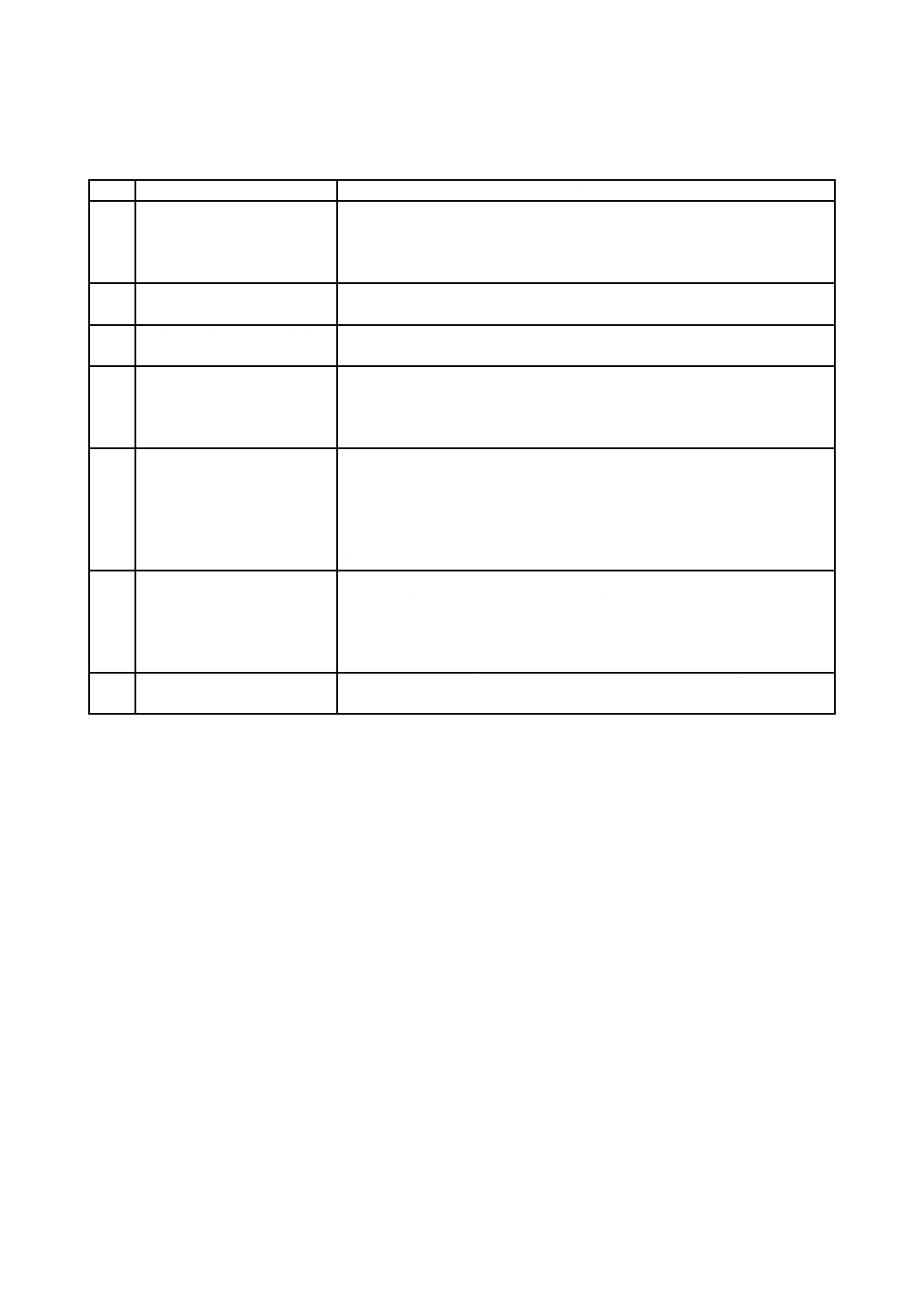

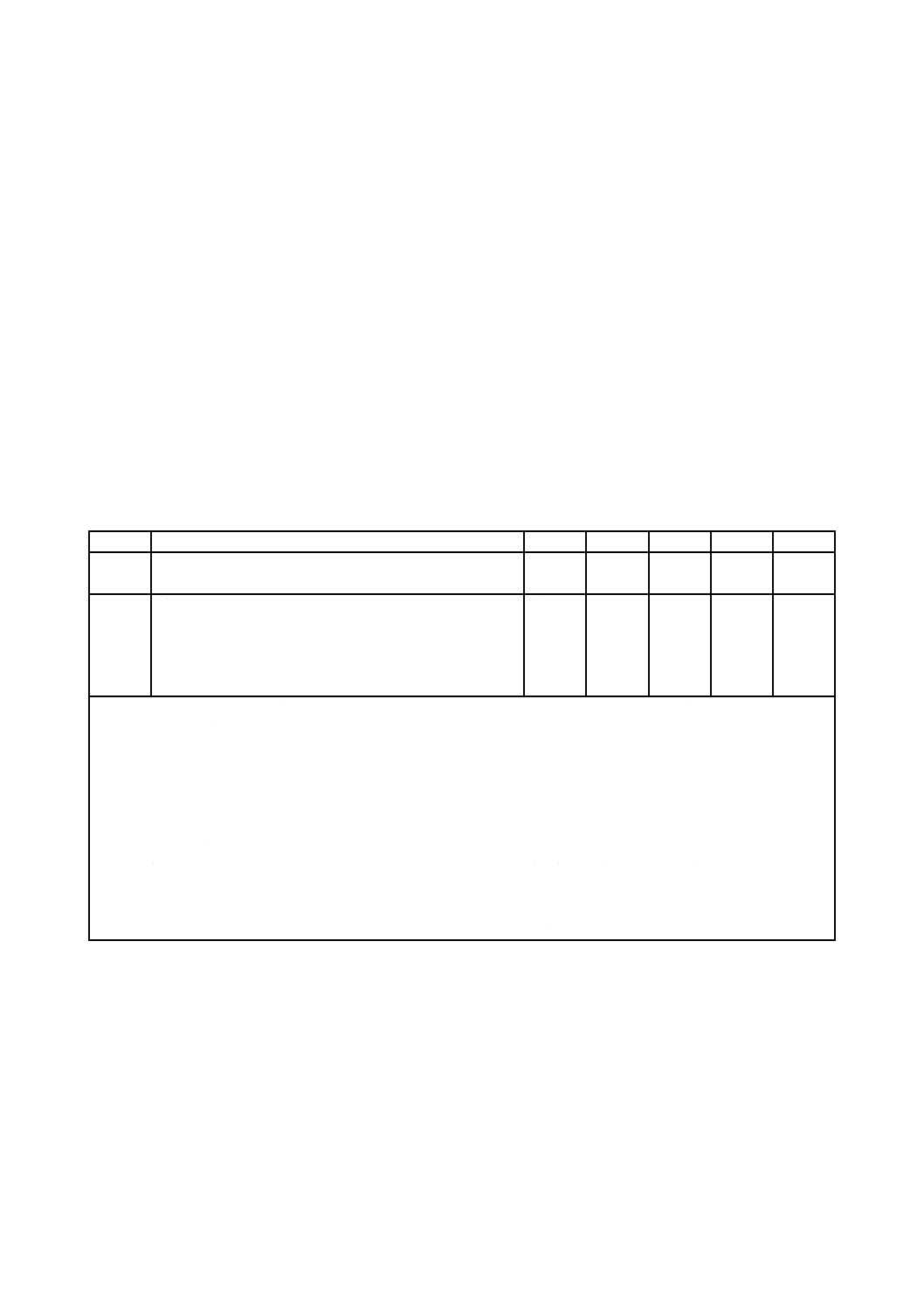

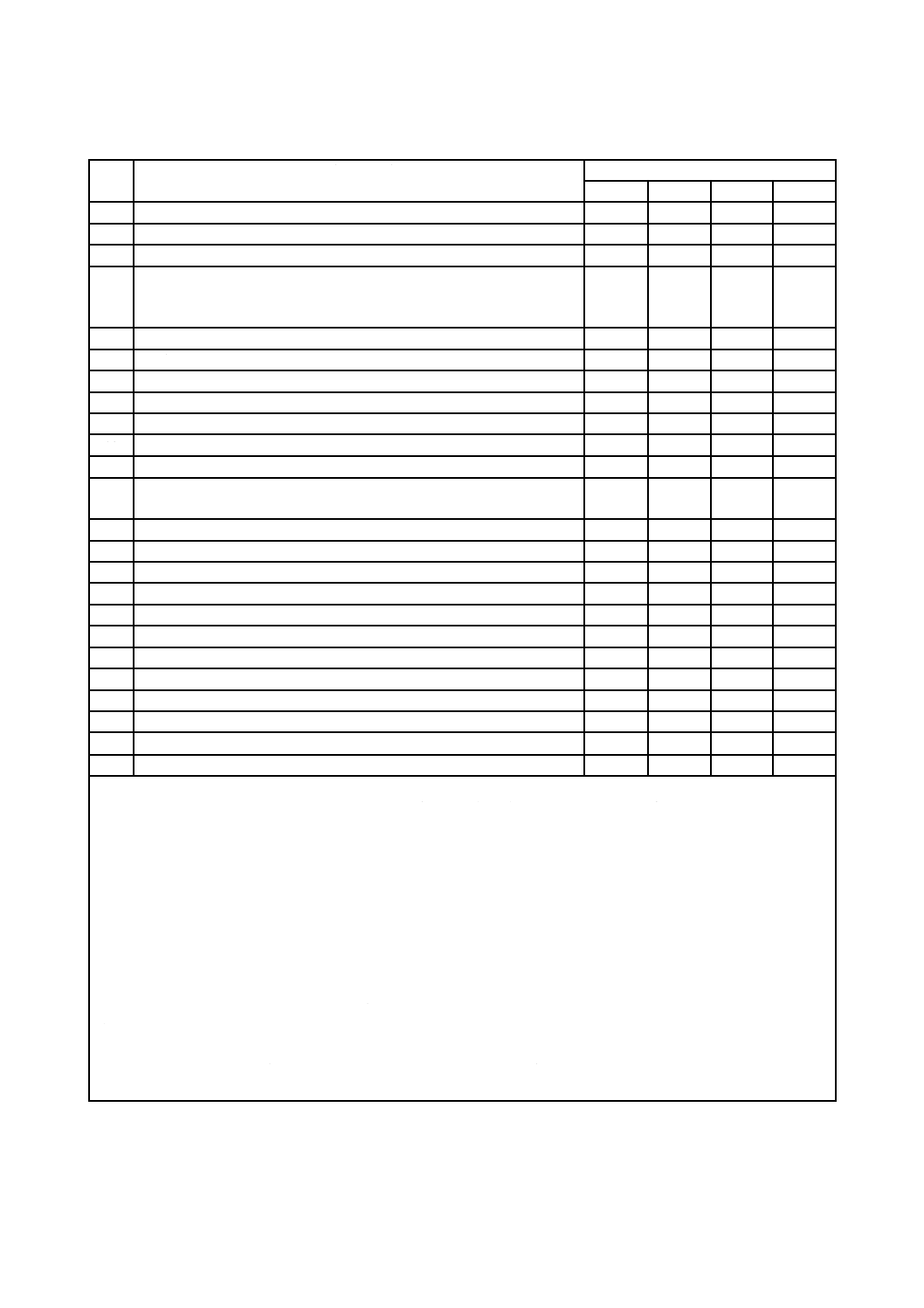

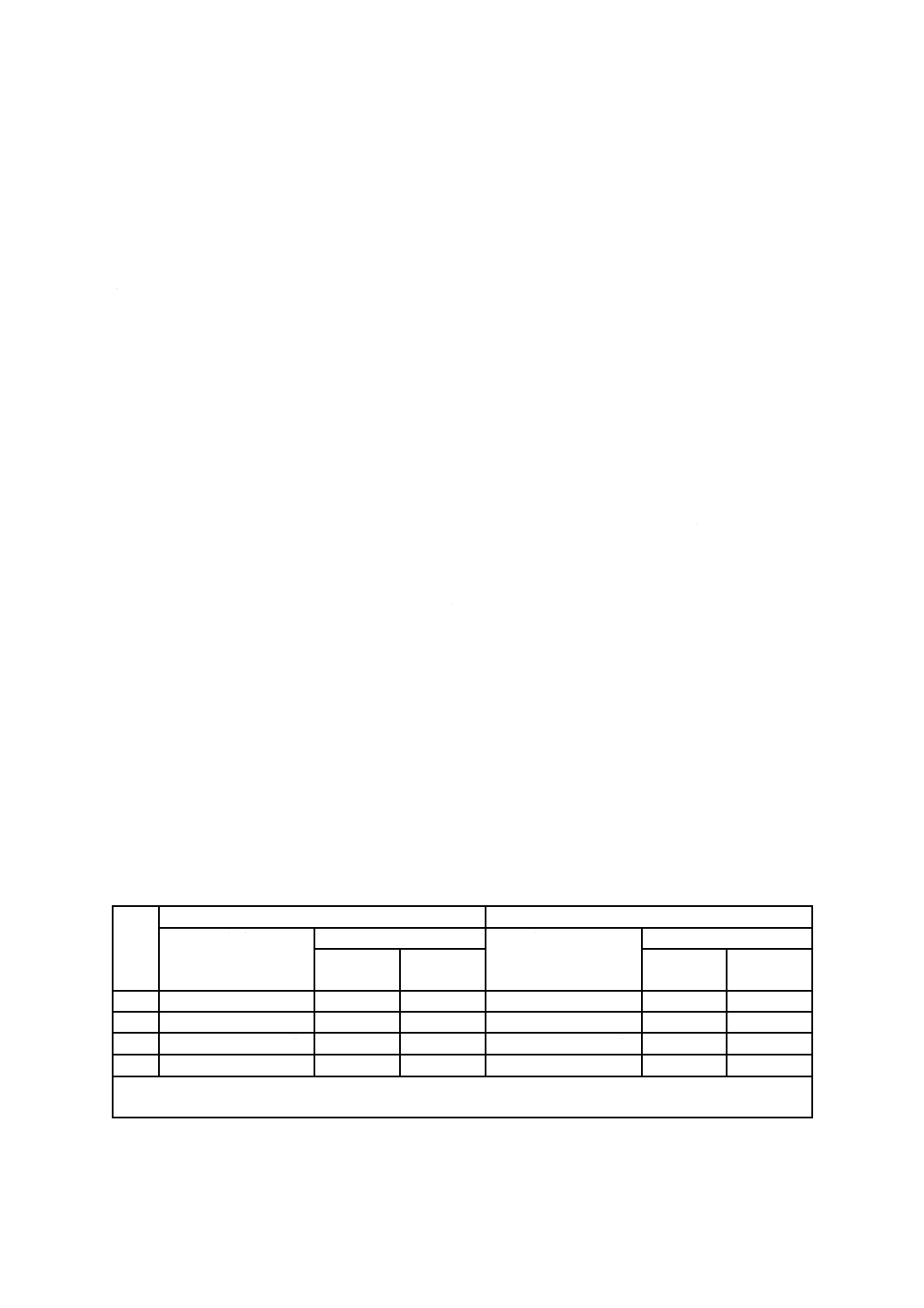

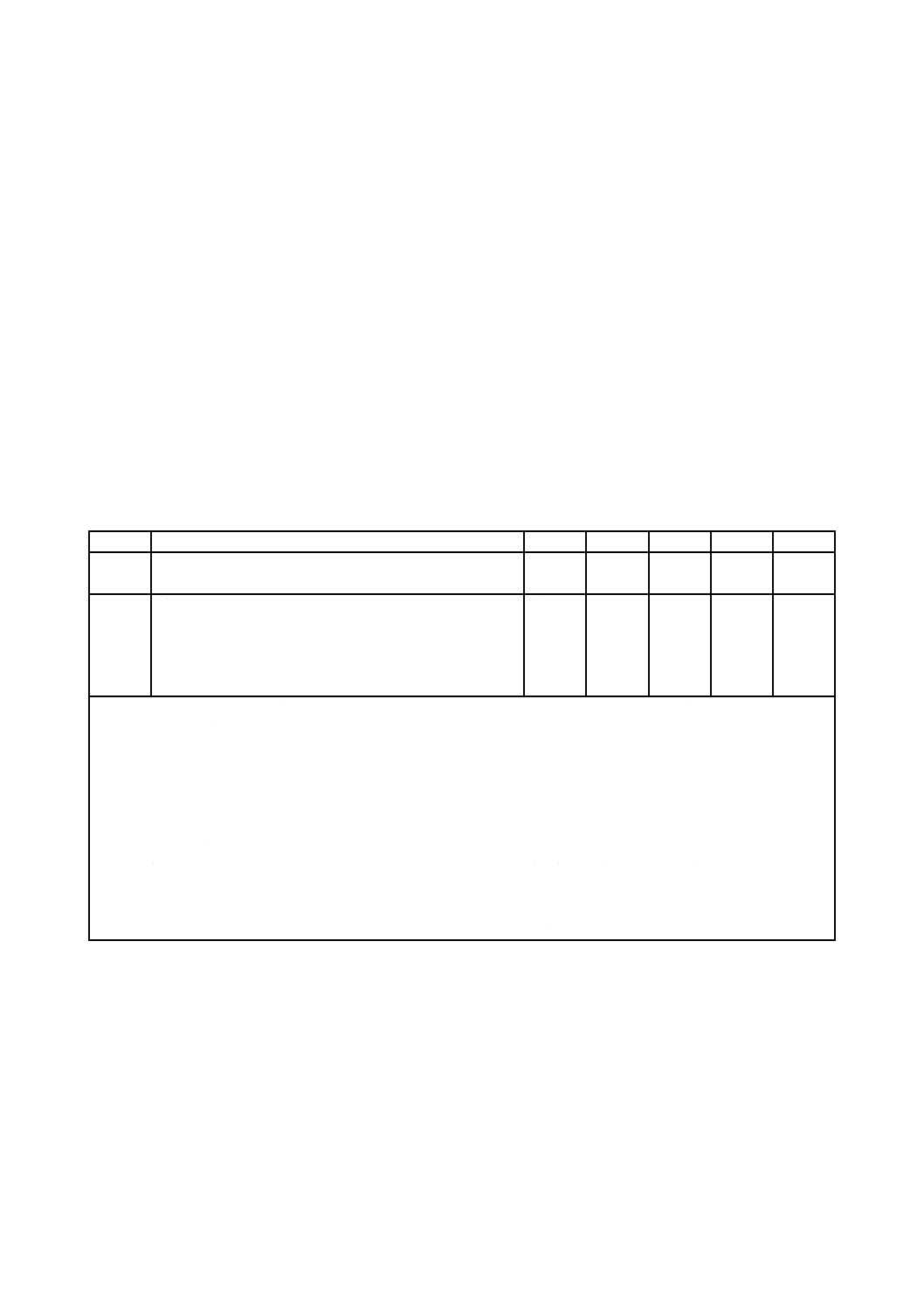

図1に,この規格群の第1部から第7部までの全体の枠組みフレームワークを示し,さらに,この

規格がE/E/PE安全関連系の機能安全の達成のために果たす役割を示す。

注記2 この規格の対応国際規格及びその対応の程度を表す記号を,次に示す。

IEC 61508-7:2010,Functional safety of electrical/electronic/programmable electronic safety-related

systems−Part 7: Overview of techniques and measures(IDT)

なお,対応の程度を表す記号“IDT”は,ISO/IEC Guide 21-1に基づき,“一致している”

ことを示す。

4

C 0508-7:2017 (IEC 61508-7:2010)

図1−この規格群の全枠組み

2

引用規格

次に掲げる規格は,この規格に引用されることによって,この規格の規定の一部を構成する。この引用

規格は,記載の年の版を適用し,その後の改正版(追補を含む。)は適用しない。

JIS C 0508-4:2012 電気・電子・プログラマブル電子安全関連系の機能安全−第4部:用語の定義及

び略語

技術的要求事項

その他の要求事項

第4部

用語の定義

及び略語

第5部

安全度水準の決定の

ための方法の例

第1部

全安全要求事項の作成

(概念,適用範囲の定義,

潜在危険及びリスク解析)

7.1〜7.5

第1部

文書化

箇条5及び

附属書A

第1部

機能安全の管理

箇条6

第1部

機能安全評価

箇条8

第1部

E/E/PE安全関連系に対する

安全要求仕様

7.10

第1部

E/E/PE安全関連系への

安全要求事項の割当て

7.6

第1部

E/E/PE安全関連系の設置,

引渡し及び安全妥当性確認

7.13〜7.14

第1部

E/E/PE安全関連系の運用,

保全及び修理,部分改修

及び改造,並びに使用終了

又は廃却

7.15〜7.17

第6部

第2部及び第3部の

適用の指針

第7部

技術及び手法

の概観

第2部

E/E/PE安全

関連系の実現

フェーズ

第3部

安全関連ソフト

ウェアの実現

フェーズ

5

C 0508-7:2017 (IEC 61508-7:2010)

注記 対応国際規格:IEC 61508-4:2010,Functional safety of electrical/electronic/programmable

electronic safety-related systems−Part 4: Definitions and abbreviations(IDT)

3

用語,定義及び略語

この規格で用いる主な用語,定義及び略語は,JIS C 0508-4による。

6

C 0508-7:2017 (IEC 61508-7:2010)

附属書A

(参考)

E/E/PE安全関連系のための技術及び手法の概要:

ランダムハードウェア故障の管理(JIS C 0508-2参照)

A.1 電気

全般:電気機械構成部品における故障を管理する。

A.1.1 オンライン監視による故障検出

注記 この技術及び手法は,JIS C 0508-2の表A.2(電気部品),表A.3(電子構成部品),表A.7[I/O

装置及びインタフェース(外部通信)]及び表A.13(センサ)〜表A.18(決定論的原因故障を

管理するための技法及び手段の有効性)で引用されている。

目的:被制御機器(EUC)の通常(オンライン)運転に応答するE/E/PE安全関連系の挙動を監視すること

で,故障を検出する。

説明:ある状況において,故障は,EUCの(例えば)時間的挙動に関する情報を用いて検出できる。例え

ば,E/E/PE安全関連系の一部であるスイッチが,通常,EUCによって作動する場合,そのスイッチ

が期待した時間に状態を変えないときは,故障を検出したことになる。通常,故障の場所を特定す

ることは不可能である。

A.1.2 リレー接点の監視

注記 この技術及び手法は,JIS C 0508-2の表A.2及び表A.14[操作端(アクチュエータ)]で引用さ

れている。

目的:リレー接点の故障(例えば,溶着)を検出する。

説明:強制接点(又は強制ガイド式接点)リレーは,その接点同士が強固に連結できるように設計されて

いる。1組のa接点とb接点とがある場合,a接点が溶着しているとき,リレーコイルへの電源供給

が停止してもb接点は閉じることができない。したがって,リレーコイルへの電源供給が停止した

ときのb接点の閉動作を監視することを,a接点が開動作したことの証明に用いてもよい。通常,b

接点を閉じることができない場合,a接点が故障したことを示す。したがって,a接点によって制御

される機械類における回路の監視は,安全な運転停止又は運転停止の継続を確実にするものである

ことが望ましい。

参考文献:

Zusammenstellung und Bewertung elektromechanischer Sicherheitsschaltungen für Verriegelungseinrichtungen.

F. Kreutzkampf, W. Hertel, Sicherheitstechnisches Informations- und Arbeitsblatt 330212, BIA-Handbuch.

17. Lfg. X/91, Erich Schmidt Verlag, Bielefeld.

http://www.bgia-handbuchdigital.de/330212

A.1.3 コンパレータ

注記 この技術及び手法は,JIS C 0508-2の表A.2,表A.3及び表A.4(処理単位)で引用されている。

目的:独立処理装置又はコンパレータの(非同時)故障をできるだけ早く検出する。

7

C 0508-7:2017 (IEC 61508-7:2010)

説明:独立処理装置の信号を,定期的又は連続的にハードウェアコンパレータによって比較する。コンパ

レータ自体は,外部的にテストしてもよいし,自己監視技術を用いてもよい。プロセッサの挙動に

関して検出した差が故障メッセージとなる。

A.1.4 多数決

注記 この技術及び手法は,JIS C 0508-2の表A.2,表A.3及び表A.4で引用されている。

目的:三つ以上のハードウェアチャネルの一つの故障を検出し,マスクする。

説明:多数決原理(2 out of 3,3 out of 3,又はm out of n)を用いた多数決回路を用いて故障を検出し,マ

スクする。多数決回路自体は,外部的にテストしてもよいし,自己監視技術を用いてもよい。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

A.1.5 アイドル電流原理(非励磁トリップ)

注記 この技術及び手法は,JIS C 0508-2の表A.16(環境上のストレス又は影響によって生じる決定

論的原因故障を管理するための技法及び手段)で引用されている。

目的:電源の遮断又は喪失があった場合に,安全機能を実行する。

説明:接点が開いても電流が流れない場合,安全機能を実行する。例えば,電動機の危険な動作を停止す

るためにブレーキを用いる場合,安全関連系の接点を閉じることによってブレーキを開き,安全関

連系の接点を開くことによってブレーキを閉じる。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

A.2 電子システム

全般:半導体素子の故障を管理する。

A.2.1 冗長化ハードウェアによるテスト

注記 この技術及び手法は,JIS C 0508-2の表A.3,表A.15(ハードウェア設計によって生じる決定

論的原因故障を管理するための技法及び手段),表A.16及び表A.18で引用されている。

目的:ハードウェア冗長性を用いて,すなわち,プロセス機能を実装するのに不要な追加のハードウェア

を用いて,故障を検出する。

説明:冗長化ハードウェアは,規定した安全機能を適切な頻度でテストするために用いることができる。

このアプローチは,通常,A.1.1又はA.2.2を実現するために必要である。

A.2.2 動的原理

注記 この技術及び手法は,JIS C 0508-2の表A.3で引用されている。

目的:動的信号処理によって静的故障を検出する。

説明:本来は静的である信号(内部的又は外部的に生成されるもの)を強制的に変化させると,構成部品

の静的故障を検出する助けとなる。この技術は,電気機械構成部品に関わることが多い。

8

C 0508-7:2017 (IEC 61508-7:2010)

参考文献:

Elektronik in der Sicherheitstechnik. H. Jürs, D. Reinert, Sicherheitstechnisches Informations- und Arbeitsblatt

330220, BIA-Handbuch, Erich-Schmidt Verlag, Bielefeld, 1993.

http://www.bgia-handbuchdigital.de/330220

A.2.3 標準テストアクセスポート及び境界走査アーキテクチャ

注記 この技術及び手法は,JIS C 0508-2の表A.3,表A.15及び表A.18で引用されている。

目的:ICの各ピンに起こることを管理及び観察する。

説明:境界走査(バウンダリスキャン)テストは,IC内部の回路テストポイントにどのようにアクセスす

るかという問題を解決することによって,ICのテストのしやすさを高めるIC設計技術である。コ

アロジック部及び入出力バッファから成る典型的な境界走査ICでは,そのコアロジック部と入出

力バッファとの間において,各ICピンに近接して,シフトレジスタステージが置かれる。各シフ

トレジスタステージは,境界走査セルに収容される。このセルは,ICの各入出力ピンに起こること

を,標準テストアクセスポートを経由して管理及び観察することができる。ICコアロジック部の内

部テストは,周囲の構成部品から受ける刺激からチップ上コアロジック部を隔離し,その後,内部

自己テストを実施することによって達成できる。これらのテストを,ICでの故障を検出するために

用いる。

参考文献:

IEEE 1149-1:2001,IEEE standard test access port and boundary-scan architecture, IEEE Computer Society,

2001, ISBN: 0-7381-2944-5

A.2.4 (不使用)

A.2.5 監視付き冗長化

注記 この技術及び手法は,JIS C 0508-2の表A.3で引用されている。

目的:幾つかの機能ユニットを備え,それぞれのユニットの故障を検出するために挙動を監視し,挙動の

不一致を検出した場合は,安全状態への移行を開始させることによって,故障を検出する。

説明:安全機能は,複数のハードウェアチャネルによって実行する。これらのチャネルの出力を監視し,

フォールトを検出した場合(すなわち,全てのチャネルからの出力信号が同一ではない場合),安

全状態を開始させる。

参考文献:

Elektronik in der Sicherheitstechnik. H. Jürs, D. Reinert, Sicherheitstechnisches Informations- und Arbeitsblatt

330220, BIA-Handbuch, Erich-Schmidt Verlag, Bielefeld, 1993.

http://www.bgia-handbuchdigital.de/330220

Dependability of Critical Computer Systems 1. F. J. Redmill, Elsevier Applied Science, 1988, ISBN

1-85166-203-0

A.2.6 自動チェック機能付き電気・電子構成部品

注記 この技術及び手法は,JIS C 0508-2の表A.3で引用されている。

目的:安全機能の周期的チェックによってフォールトを検出する。

9

C 0508-7:2017 (IEC 61508-7:2010)

説明:ハードウェアを,処理を開始する前にテストし,さらに,適切な間隔でテストを繰り返す。各テス

トが正常終了したときだけ,EUCは運転を継続する。

参考文献:

Elektronik in der Sicherheitstechnik. H. Jürs, D. Reinert, Sicherheitstechnisches Informations- und Arbeitsblatt

330220, BIA-Handbuch, Erich-Schmidt Verlag, Bielefeld, 1993.

http://www.bgia-handbuchdigital.de/330220

Dependability of Critical Computer Systems 1. F. J. Redmill, Elsevier Applied Science, 1988, ISBN

1-85166-203-0

A.2.7 アナログ信号監視

注記 この技術及び手法は,JIS C 0508-2の表A.3及び表A.13で引用されている。

目的:測定した信号に対する信頼性を高める。

説明:選択が許される限り,アナログ信号を,デジタルオン又はオフの状態に優先して用いる。例えば,

トリップ又は安全な状態は,通常,信号レベル許容差の監視を伴うアナログ信号レベルによって表

す。この技術は,連続性の監視を行い,また,伝送器に対する信頼性を高め,さらに,伝送器のセ

ンシング機能に必要なプルーフテスト頻度を減らす。外部のインタフェース,例えば,インパルス

ラインもテストする必要がある。

A.2.8 ディレーティング

注記 この技術及び手法は,JIS C 0508-2の7.4.2.13で引用されている。

目的:ハードウェア構成部品の信頼性を増す。

説明:ハードウェア構成部品は,システムの設計によって保証する,最大仕様定格を十分に下回る水準で

用いる。ディレーティングは,全ての通常動作条件の下で,各構成部品がこれらの耐用条件の上限

よりも十分に余裕のある状態で動作するための手法である。

A.3 演算処理装置

全般:演算処理装置における間違った結果を導く故障を認識する。

A.3.1 ソフトウェアによる自己テスト:パターンの数が限られている(単一チャネル)

注記 この技術及び手法は,JIS C 0508-2の表A.4で引用されている。

目的:演算処理装置の故障をできるだけ早く検出する。

説明:ハードウェアは,特別な安全要求事項を全く考慮に入れない標準技術を用いて製作されている。故

障検出は,全面的に,複数の補完的データパターン(例えば,55 hex及びAA hex)を用いて自己テ

ストを実行する追加のソフトウェア機能によって実現する。

A.3.2 ソフトウェアによる自己テスト:ウォーキングビット(単一チャネル)

注記 この技術及び手法は,JIS C 0508-2の表A.4で引用されている。

目的:演算処理装置の物理的記憶装置(例えば,レジスタ)及び命令デコーダの故障を,できるだけ早く

検出する。

説明:故障検出は,全面的に,物理的記憶装置(データ及びアドレスレジスタ)及び命令デコーダをテス

10

C 0508-7:2017 (IEC 61508-7:2010)

トするデータパターン(例えば,ウォーキングビットパターン)を用いて自己テストを実施する,

追加のソフトウェア機能によって実現する。ただし,診断カバー率は90 %にとどまる。

A.3.3 ハードウェアが対応する自己テスト(単一チャネル)

注記 この技術及び手法は,JIS C 0508-2の表A.4で引用されている。

目的:故障検出の速度を高め,範囲を広げる専用のハードウェアを用いて,演算処理装置の故障をできる

だけ早く検出する。

説明:追加の専用ハードウェア装置によって,故障を検出するための自己テスト機能を支援する。これ

は,例えば,あるビットパターンの出力をウォッチドッグ原理に従って周期的に監視するハードウ

ェア装置であってもよい。

A.3.4 符号化処理(単一チャネル)

注記 この技術及び手法は,JIS C 0508-2の表A.4で引用されている。

目的:演算処理装置の故障を,できるだけ早く検出する。

説明:演算処理装置は,特別な故障認識又は故障訂正回路技術を用いて設計することができる。これらの

技術は,今のところ,比較的単純な回路だけに適用されつつあるが,広範囲に用いられてはいない。

ただし,将来の展開の余地も排除しないことが望ましい。

参考文献:

Le processeur codé: un nouveau concept appliqué à la sécurité des systèmes de transports. Gabriel, Martin,

Wartski, Revue Générale des chemins de fer, No. 6, June 1990

Vital Coded Microprocessor Principles and Application for Various Transit Systems. P. Forin, IFAC Control

Computers Communications in Transportation, 79-84, 1989

A.3.5 ソフトウェアによる相互比較

注記 この技術及び手法は,JIS C 0508-2の表A.4で引用されている。

目的:動的ソフトウェア比較によって,演算処理装置の故障をできるだけ早く検出する。

説明:二つの演算処理装置によって,データ(結果,中間結果及びテストデータを含む。)を相互に交換

する。データの比較を,各装置内のソフトウェアを用いて実施し,相違が生じた場合は故障メッセ

ージを生成する。

A.4 不変メモリの範囲

全般:不変メモリ内の情報の書き変わりを検出する。

A.4.1 ワード保護された複数ビットによる冗長化(例えば,拡張ハミングコードを用いたROMの監視)

注記1 この技術及び手法は,JIS C 0508-2の表A.5(不変メモリの範囲)で引用されている。

注記2 A.5.6及びC.3.2も参照。

目的:16ビットワード中の全ての単一ビット故障,全ての2ビット故障,幾つかの3ビット故障及び幾つ

かの全ビット故障を検出する。

説明:メモリの各ワードは,4以上のハミング距離をもつ拡張ハミングコードを生成するために,数ビッ

トの冗長ビット分だけ拡張する。1ワードを読むごとに,冗長ビットのチェックをすることで,改

11

C 0508-7:2017 (IEC 61508-7:2010)

ざんが起こっているかどうか判定できる。相違が生じた場合,故障メッセージを生成する。データ

ワードとそのアドレスとの連結のための冗長ビットを計算することによって,アドレス故障を検出

するためにも用いることができる。

参考文献:

Prüfbare und korrigierbare Codes. W. W. Peterson, München, Oldenburg, 1967

Error detecting and error correcting codes. R. W. Hamming, The Bell System Technical Journal 29 (2), 147-160,

1950

A.4.2 修正チェックサム

注記 この技術及び手法は,JIS C 0508-2の表A.5で引用されている。

目的:全ての奇数ビット故障,すなわち,起こる可能性がある全てのビット故障の約50 %を検出する。

説明:チェックサムは,1ブロックメモリ内の全てのワードを用いる適切なアルゴリズムによって作成す

る。チェックサムは,追加の1ワードとしてROMに格納するか,又はチェックサムアルゴリズム

が前もって決めておいた値を確実に生成するようにするため,そのメモリブロックに追加の1ワー

ドを追加してもよい。その後のメモリテストにおいて,同じアルゴリズムを用いてチェックサムを

再び作成する。その結果を,格納した値又は決めておいた値と比較する。相違が生じた場合,故障

メッセージを生成する。

A.4.3 1ワード(8ビット)の署名

注記 この技術及び手法は,JIS C 0508-2の表A.5で引用されている。

目的:1ワード内の全ての1ビット故障及び全ての複数ビット故障,並びに起こる可能性がある全てのビ

ット故障の約99.6 %を検出する。

説明:メモリブロックの内容を,巡回冗長検査(CRC)アルゴリズムを用いて,(ハードウェア又はソフ

トウェアのどちらかによって)1メモリワードに圧縮する。典型的なCRCアルゴリズムでは,ブロ

ックの内容全体をバイトシリアル又はビットシリアルのデータフローとして処理し,そのデータフ

ローにおいて,生成多項式の発生器を用いて連続的な多項式の除算を行う。除算の余りは圧縮した

メモリ内容を表す“署名”であり,メモリに格納する。署名はその後のテストで再び計算する。こ

の署名と既に格納したものとを比較する。相違が生じた場合,故障メッセージを生成する。

A.4.4 ダブルワード(16ビット)の署名

注記 この技術及び手法は,JIS C 0508-2の表A.5で引用されている。

目的:1ワード内の全ての1ビット故障及び全ての複数ビット故障,並びに起こる可能性がある全てのビ

ット故障の約99.998 %を検出する。

説明:この手順では,CRCアルゴリズムを用いて署名を計算する。ただし,その結果の値の大きさは2ワ

ード以上とする。拡張した署名を,単一ワードの場合と同様に格納し,再計算する。これらの署名

を,比較する。格納した署名と再計算した署名との間に相違が生じた場合,故障メッセージを生成

する。

A.4.5 ブロック複製(例えば,ハードウェア又はソフトウェア比較による二重ROM)

注記 この技術及び手法は,JIS C 0508-2の表A.5で引用されている。

12

C 0508-7:2017 (IEC 61508-7:2010)

目的:全てのビット故障を検出する。

説明:アドレス空間を,二つのメモリ内に複写する。第1のメモリは,通常の方法で操作する。第2のメ

モリは,同じ情報を収納しておき,第1のものと並行してアクセスする。出力を比較し,相違が生

じた場合は,故障メッセージを生成する。ある種のビットエラーを検出するためには,二つのメモ

リのいずれかのデータを反転して格納し,読み取るときに再び反転させる必要がある。

A.5 可変メモリの範囲

全般:アドレス指定,書き込み,格納及び読取り中の故障を検出する。

注記 JIS C 0508-2の表A.1(ランダムハードウェア故障を定量化するときに想定する又は安全側故障

割合の導出で考慮するフォールト又は故障)では,ソフトエラーを動作中に検出するフォール

ト又は安全側故障割合の導出で考慮するフォールトとして記載している。ソフトエラーの原因

は,(1)パッケージを構成する原子核の崩壊によるアルファ粒子,(2)中性子,(3)外部EMI

雑音及び(4)内部クロストークである。外部EMI雑音は,この規格群の他の要求事項で取り

扱っている。

アルファ粒子及び中性子の影響は,運用時の安全保全手法によって抑制することが望ましい。

ハードエラーに対して有効な安全保全手法は,ソフトエラーに対しては有効でない場合がある。

例えば,ウォークパス(walk-path),ガルパット(galpat)などのRAMテストは有効ではない

が,パリティ及び誤り訂正符号(ECC)を用いるメモリセルの繰返し読取り監視技術は有効で

ある。

ソフトエラーは,電磁放射事象が低電圧駆動半導体メモリセル,レジスタ,ラッチ又はフリ

ップフロップのデータ状態を逆転又は反転させるため,十分な電荷障害を引き起こす場合に発

生する。このエラーは,回路自体がこの放射によって恒久的な損害を受けないので,“ソフト”

と呼ばれる。ソフトエラーは,単一ビットアップセット(SBU),又は単一事象アップセット

(SEU)及び複数ビットアップセット(MBU)に分類されている。

妨害された回路がメモリセル又はフリップフロップのような格納素子である場合,この状態

は,次の(意図した)書き込み操作のときまで格納する。新しいデータは,正確に格納する。

組合せ回路では,このノードを駆動する構成部品から絶えずエネルギーが流れているので,こ

の影響はどちらかといえばグリッチといえる。配線及び通信線を接続する場合,この影響もグ

リッチとなる場合がある。ただし,容量が大きいために,アルファ粒子及び中性子の影響は無

視できるとみなす。

ソフトエラーは,いずれかの種類の可変メモリ,すなわち,DRAM,SRAM,マイクロプロ

セッサのレジスターバンク,キャッシュ,パイプライン,ADC,DMA,MMU,割り込みコン

トローラ,複雑なタイマなどのコンフィグレーションレジスタに関係することがある。アルフ

ァ粒子及び中性子粒子に対する感受性は,コア電圧及び形状の両方との関係によって決まる。

コア電圧が2.5 V,特に1.8 V未満の小形形状の場合,さらに評価を行い,より効果的な保護手

段をとる必要があろう。

ソフトエラー率は,(内蔵)メモリの場合,700 Fit/MBit〜1 200 Fit/MBitの範囲内にあると報

告されている[次のa)〜i) の文献及び資料を参照]。ただし,この数値は,デバイスを実装し

たシリコンプロセスからのデータと比較するための基準値である。最近まで,SBUが有力と考

えられてきたが,最新の予測[次のa) 参照]では,65 nm以下のシリコンプロセスの技術では

13

C 0508-7:2017 (IEC 61508-7:2010)

MBUの全体的ソフトエラー率(SER)が増えていると報告されている。

次の文献及び資料は,ソフトエラーについて詳述している。

a) Altitude SEE Test European Platform (ASTEP) and First Results in CMOS 130 nm SRAM. J-L.

Autran, P. Roche, C. Sudre et al. Nuclear Science, IEEE Transactions on Volume 54, Issue 4, Aug.

2007 Page(s): 1002-1009

b) Radiation-Induced Soft Errors in Advanced Semiconductor Technologies, Robert C. Baumann,

Fellow, IEEE, IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 5,

NO. 3, SEPTEMBER 2005

c) Soft errors' impact on system reliability, Ritesh Mastipuram and Edwin C Wee, Cypress

Semiconductor, 2004

d) Trends And Challenges In VLSI Circuit Reliability, C. Costantinescu, Intel, 2003, IEEE Computer

Society

e) Basic mechanisms and modeling of single-event upset in digital microelectronics, P. E. Dodd and L.

W. Massengill, IEEE Trans. Nucl. Sci., vol. 50, no. 3, pp. 583-602, Jun. 2003.

f)

Destructive single-event effects in semiconductor devices and ICs, F. W. Sexton, IEEE Trans. Nucl.

Sci., vol. 50, no. 3, pp. 603-621, Jun. 2003.

g) Coming Challenges in Microarchitecture and Architecture, Ronen, Mendelson, Proceedings of the

IEEE, Volume 89, Issue 3, Mar 2001 Page(s): 325-340

h) Scaling and Technology Issues for Soft Error Rates, A Johnston, 4th Annual Research Conference

on Reliability Stanford University, October 2000

i)

International Technology Roadmap for Semiconductors (ITRS), several papers.

A.5.1 RAMテストの“チェッカーボード”又は“マーチ”

注記 この技術及び手法は,JIS C 0508-2の表A.6(可変メモリの範囲)で引用されている。

目的:主に静的ビット故障を検出する。

説明:0及び1のチェッカーボードパターンを,ビット指向メモリのセルに書き込む。その後,セルを,

一対ごとに,内容が同一で正しいことを確実にするために検査する。このような一対の最初のセル

のアドレスは可変であり,その対の2番目のセルのアドレスは,最初のアドレスをビット規模で反

転して形成する。最初の実行においては,メモリのアドレス範囲は可変アドレスから上位アドレス

に向かって実行し,2番目の実行においては,下位アドレスに向かって実行する。両方の実行は,

その後,最初の割当てを反転して繰り返す。相違が生じた場合は,故障メッセージを生成する。

RAMテスト“マーチ”においては,ビット指向メモリのセルは,一つの一様なビットストリーム

によって初期化する。最初の実行において,セルを昇順に検査する。各セルを内容が正しいかチェ

ックし,その内容を反転する。最初の実行において作成したバックグラウンドは,2番目の一連の

テストにおいて降順に,同じ方法で検査する。両方の最初の実行は,最初の割当てを反転して,3

番目又は4番目の実行において繰り返す。相違が生じた場合は,故障メッセージを生成する。

A.5.2 RAMテストの“ウォークパス”

注記 この技術及び手法は,JIS C 0508-2の表A.6で引用されている。

目的:静的及び動的なビット故障,並びにメモリセル間のクロストークを検出する。

14

C 0508-7:2017 (IEC 61508-7:2010)

説明:テスト対象のメモリ範囲を,一つの一様なビットストリームによって初期化する。その後1番目の

セルを反転し,残りのメモリ領域を,バックグラウンドが正しいことを確実にするために検査する。

その後,1番目のセルを,元の値に戻すために再反転し,次のセルに対して全手順を繰り返す。バ

ックグラウンドの最初の割当てを反転して,“さまよえるビットモデル”の2回目の実行を行う。

相違が生じた場合は,故障メッセージを生成する。

A.5.3 RAMテストの“ガルパット”又は“透過ガルパット”

注記 この技術及び手法は,JIS C 0508-2の表A.6で引用されている。

目的:静的ビット故障及び高い比率の動的結合を検出する。

説明:RAMテスト“ガルパット”においては,最初に,選択したメモリ範囲を一様に(すなわち,全て0

又は全て1に)初期化する。その後,テストする最初のメモリセルを反転し,残りの全てのセルを,

これらの内容が正しいことを確実にするために検査する。残りのセルの一つへの各読取アクセス後

に,反転したセルもチェックする。この手順を,選択したメモリ範囲内の各セルに対して繰り返す。

2回目の実行は,初期化の逆によって実施する。相違が生じた場合は,故障メッセージを生成する。

“透過ガルパット”のテストは,上記の手順を変化させたものである。すなわち,選択したメモ

リ範囲内の全てのセルを初期化しないで,現在の内容を変化させず,複数の組になったセルの内容

を比較するために署名を用いる。選択した範囲内のテスト対象の最初のセルを選択し,その範囲内

の残りの全てのセルの署名S1を計算し,格納する。その後,その被験セルを反転し,残りの全て

のセルの署名S2を再計算する(残りのセルの一つへの各読取アクセス後に,反転したセルもチェ

ックする。)。S2とS1とを比較し,相違が生じた場合は,故障メッセージを生成する。被験セルを,

元の内容を再確立するために再反転し,残りの全てのセルの署名S3を再計算し,S1と比較する。

相違が生じた場合は,故障メッセージを生成する。選択範囲内の全てのメモリセルを,同様にテス

トする。

A.5.4 RAMテストの“アブラハム”

注記 この技術及び手法は,JIS C 0508-2の表A.6で引用されている。

目的:メモリセル間の縮退故障及び結合故障の全てを検出する。

説明:検出できるフォールトの比率は,RAMテストの“ガルパット”のものを超える。全メモリテスト

を実施するために要求される操作数は,メモリ中のセル数をnとする場合,約30 nである。メモリ

を分割し,各部分を別々の時間区分においてテストすることによって,実行サイクルからのメモリ

アクセスからはテストが“透明”になるようにすることができる。

参考文献:

Efficient Algorithms for Testing Semiconductor Random-Access Memories. R. Nair, S. M. Thatte, J. A.

Abraham, IEEE Trans. Comput. C-27(6), 572-576, 1978

A.5.5 1ビット冗長性(例えば,パリティビットによるRAM監視)

注記 この技術及び手法は,JIS C 0508-2の表A.6で引用されている。

目的:テストするメモリ範囲内で起こる可能性がある全てのビット故障の50 %を検出する。

説明:メモリの各ワードを1ビット(パリティビット)で拡張し,各ワードは,そのビットを追加するこ

とで,論理1を偶数個又は奇数個もつワードとする。データワードのパリティは,読み取るごとに

15

C 0508-7:2017 (IEC 61508-7:2010)

チェックする。1の個数が違っていることを発見した場合,故障メッセージを生成する。偶数パリ

ティ又は奇数パリティの選択は,ゼロワード(0しかない)及びワンワード(1しかない)のどち

らかが故障の発生時に,より好ましくないものである場合は,そのより好ましくない方のワードが

有効コードとはならないように選択することが望ましい。パリティをデータワードとそのアドレス

との連結のために計算する場合,パリティは,アドレス指定故障を検出するために用いることもで

きる。

A.5.6 拡張ハミングコードによるRAM監視,又はエラー検出訂正コード(EDC)によるデータ故障の検

出

注記1 この技術及び手法は,JIS C 0508-2の表A.6で引用されている。

注記2 A.4.1及びC.3.2も参照。

目的:全ての奇数ビット故障,全ての2ビット故障,幾つかの3ビット故障及び幾つかの複数ビット故障

を検出する。

説明:ハミング距離を4以上とする拡張ハミングコードを作成するために,メモリへの各アクセスを数ビ

ットの冗長ビットだけ拡張する。データを読み取るごとに,冗長ビットをチェックすることで,改

ざんが起こったかどうかを判定することができる。相違が生じた場合は,故障メッセージを生成す

る。冗長ビットをデータとそのアドレスとの連結のために計算する場合,この手順をアドレス指定

故障を検出するために用いることもできる。

参考文献:

Prüfbare und korrigierbare Codes. W. W. Peterson, München, Oldenburg, 1967

Error detecting and error correcting codes. R. W. Hamming, The Bell System Technical Journal 29 (2), 147-160,

1950

A.5.7 ハードウェア又はソフトウェア比較及びリードライトテストが実施されるダブルRAM

注記 この技術及び手法は,JIS C 0508-2の表A.6で引用されている。

目的:全てのビット故障を検出する。

説明:アドレス空間を,二つのメモリ内に複写する。第1のメモリは,通常の方法で操作する。第2のメ

モリは,同じ情報を収納しておき,第1のものと並行してアクセスする。出力を比較し,相違が生

じた場合は,故障メッセージを生成する。ある種のビットエラーを検出するためには,二つのメモ

リのいずれかのデータを反転して格納し,読み取るときに再び反転する必要がある。

A.6 I/O装置及びインタフェース(外部通信)

全般:入出力装置(デジタル,アナログ,シリアル又はパラレル)の故障を検出し,処理への許容できな

い出力を防止する。

A.6.1 テストパターン

注記 この技術及び手法は,JIS C 0508-2の表A.7,表A.13及び表A.14で引用されている。

目的:静的故障(縮退故障)及びクロストークを検出する。

説明:これは,入出力装置のデータフローから独立した周期的テストである。このテストでは,観測値を

対応する期待値と比較するために,定義したテストパターンを用いる。テストパターン情報,テス

16

C 0508-7:2017 (IEC 61508-7:2010)

トパターン受信及びテストパターン評価は,全て,それぞれ独立させる必要がある。EUCが,テス

トパターンから許容できない影響を受けることは望ましくない。

A.6.2 コードの保護

注記 この技術及び手法は,JIS C 0508-2の表A.7,表A.15,表A.16及び表A.18で引用されている。

目的:入出力データフローのランダムハードウェア故障及び決定論的原因故障を検出する。

説明:この手順は,決定論的原因故障及びランダムハードウェア故障の両方から入出力情報を保護する。

コード保護では,情報冗長性及び/又は時間冗長性に基づき,入出力装置のデータフロー従属故障

の検出を行う。典型的なものとしては,冗長情報を入力及び/又は出力データに重ね合わせる。こ

れによって,入出力回路の正しい動作を監視する手段を得る。多くの技術が可能であり,例えば,

搬送波信号をセンサの出力信号に重ね合わせてもよい。その後,ロジック装置によって,搬送波が

あるかどうかを確認してもよいし,ロジック装置と最終アクチュエータとの間を通過する信号の妥

当性を監視できるように,出力チャネルに冗長コードビットを追加してもよい。

A.6.3 マルチチャネル パラレルアウトプット

注記 この技術及び手法は,JIS C 0508-2の表A.7で引用されている。

目的:ランダムハードウェア故障(縮退故障),外部からの影響によって発生する故障,タイミング故障,

アドレス指定故障,ドリフト故障及び一時故障を検出する。

説明:これは,ランダムハードウェア故障を検出するための,独立出力をもつデータフロー依存のマルチ

チャネル パラレル出力である。故障検出は,外部のコンパレータを介して実施する。故障が起こ

った場合,EUCはその電源を直接,遮断する。この手法は,診断テスト間隔内でデータフローが変

化した場合だけに有効である。

A.6.4 監視付きアウトプット

注記 この技術及び手法は,JIS C 0508-2の表A.7で引用されている。

目的:個別故障,外部からの影響によって発生する故障,タイミング故障,アドレス指定故障,ドリフト

故障(アナログ信号用)及び一時故障を検出する。

説明:これは,定義された許容範囲(時間及び値)との適合性を確実にするための,独立した入力値に対

する,出力値のデータフロー依存の比較である。検出した故障は,必ずしも,欠陥を有する出力に

関わるとは限らない。この手法は,診断テスト間隔内でデータフローが変化した場合だけに有効で

ある。

A.6.5 インプット比較又は多数決

注記 この技術及び手法は,JIS C 0508-2の表A.7及び表A.13で引用されている。

目的:個別故障,外部からの影響によって発生する故障,タイミング故障,アドレス指定故障,ドリフト

故障(アナログ信号用)及び一時故障を検出する。

説明:これは,定義された許容範囲(時間及び値)との適合性を確実にするための,独立した入力値のデ

ータフロー依存の比較である。“1oo2,2oo3又はこれ以上の冗長化”を用いる。この手法は,診断

テスト間隔内でデータフローが変化した場合だけに有効である。

17

C 0508-7:2017 (IEC 61508-7:2010)

A.7 データパス(内部通信)

全般:情報伝送における欠陥によって発生する故障を検出する。

A.7.1 1ビット追加によるハードウェアの冗長化

注記 この技術及び手法は,JIS C 0508-2の表A.8[データパス(内部通信)]で引用されている。

目的:全ての奇数ビット故障,すなわちデータストリームにおいて起こる可能性がある全てのビット故障

の約50 %を検出する。

説明:バスを1ライン(ビット)だけ拡張し,この追加のライン(ビット)は,パリティチェックによっ

て故障を検出するために用いる。

A.7.2 複数ビット追加によるハードウェアの冗長化

注記 この技術及び手法は,JIS C 0508-2の表A.8で引用されている。

目的:バス及びシリアル伝送リンクによる通信中の故障を検出する。

説明:バスを二つ以上のライン(ビット)だけ拡張し,これらの追加のライン(ビット)を,ハミングコ

ード技術によって故障を検出するために用いる。

A.7.3 二重化によるハードウェアの冗長化

注記 この技術及び手法は,JIS C 0508-2の表A.8で引用されている。

目的:二つのバスの信号を比較することによって,通信中の故障を検出する。

説明:バスを二重にし,追加のライン(ビット)を故障を検出するために用いる。

A.7.4 テストパターンを用いる検査

注記 この技術及び手法は,JIS C 0508-2の表A.8で引用されている。

目的:静的故障(縮退故障)及びクロストークを検出する。

説明:これは,データ経路のデータフロー非従属周期的テストである。このテストでは,観測値を対応す

る期待値と比較するために,テストパターンを定義して用いる。

テストパターン情報,テストパターン受信及びテストパターン評価は,全て,それぞれ独立させ

る必要がある。EUCが,テストパターンから許容できない影響を受けることは望ましくない。

A.7.5 伝送の冗長化

注記 この技術及び手法は,JIS C 0508-2の表A.8で引用されている。

目的:バス通信における一時故障を検出する。

説明:情報を数回,順次伝送する。繰返しは,一時故障に対してだけに有効である。

A.7.6 情報の冗長化

注記 この技術及び手法は,JIS C 0508-2の表A.8で引用されている。

目的:バス通信における故障を検出する。

説明:データをブロック単位で,ブロックごとに計算したチェックサムとともに送信する。その後,受信

側は,受信したデータのチェックサムを再計算し,その結果を受信したチェックサムと比較する。

18

C 0508-7:2017 (IEC 61508-7:2010)

A.8 電源

全般:電源の欠陥によって発生する故障を検出又は許容する。

A.8.1 安全遮断又は二次電源への切換えによる過電圧保護

注記 この技術及び手法は,JIS C 0508-2の表A.9(電源)で引用されている。

目的:安全関連系を過電圧から保護する。

説明:パワーダウン処理による全ての出力の安全状態への切換え,又は二次電源(予備電源)への切換え

が十分間に合うように過電圧を検出する。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

A.8.2 安全遮断又は二次電源への切換えによる電圧制御(二次制御)

注記 この技術及び手法は,JIS C 0508-2の表A.9で引用されている。

目的:二次電圧を監視し,その電圧が規定範囲内でない場合,安全状態への移行を開始する。

説明:二次電圧を監視し,その電圧が規定範囲内でない場合,パワーダウンを開始するか,又は二次電源

への切換えを行う。

A.8.3 安全遮断又は二次電源への切換えによる電源断

注記 この技術及び手法は,JIS C 0508-2の表A.9で引用されている。

目的:全ての安全重要情報を記憶して,電源を遮断する。

説明:内部状態を(必要ならば)不揮発性メモリで保存することができ,さらに,次のいずれかの事項が,

十分間に合うように早く,過電圧又は不足電圧を検出する。

− 全ての出力を電源断のための通常手順によって,安全状態への設定が可能になる。

− 全ての出力を電源断のための通常手順によって,安全状態への切換えが可能になる。

− 二次電源へ切り換わる。

A.9 時間的及び論理的プログラムシーケンス監視

注記 この技術及び手法は,JIS C 0508-2の表A.15,表A.16及び表A.18で引用されている。

全般:欠陥を有するプログラムシーケンスを検出する。プログラムの個々の要素(例えば,ソフトウェア

モジュール,サブプログラム又はコマンド)が不正なシーケンス若しくは不正な時間で処理を実行

した場合,又はプロセッサのクロックが正しくない場合,欠陥を有するプログラムシーケンスが存

在する。

A.9.1 時間窓なしの個別の時間基準によるウォッチドッグ

注記 この技術及び手法は,JIS C 0508-2の表A.10[プログラムシーケンス(ウォッチドッグ)]及び

表A.11(クロック)で引用されている。

目的:プログラムシーケンスの振舞い及び確からしさを監視する。

説明:コンピュータの挙動及びプログラムシーケンスの確からしさを監視するために,個別の時間間隔を

もつ外部タイミング要素(例えば,ウォッチドッグタイマ)を周期的にリセットする。プログラム

19

C 0508-7:2017 (IEC 61508-7:2010)

中にリセットの実行点を正しく置くことが重要である。ウォッチドッグタイマのリセットの実行は,

特定の1か所ではなく,最大実行間隔を指定する。

A.9.2 時間窓がある個別の時間基準によるウォッチドッグ

注記 この技術及び手法は,JIS C 0508-2の表A.10及び表A.11で引用されている。

目的:プログラムシーケンスの振舞い及び確からしさを監視する。

説明:コンピュータの挙動及びプログラムシーケンスの確からしさを監視するために,個別の時間間隔を

もつ外部タイミング要素(例えば,ウォッチドッグタイマ)を周期的にリセットする。プログラム

中にリセットの実行点を正しく置くことが重要である。ウォッチドッグタイマには下限及び上限を

設定する。プログラムシーケンスの時間が期待値よりも長いか又は短い場合,緊急制御動作を行う。

A.9.3 プログラムシーケンスの論理監視

注記 この技術及び手法は,JIS C 0508-2の表A.10及び表A.11で引用されている。

目的:プログラムの個々の部分の振舞い及び正しいシーケンスを監視する。

説明:プログラムの個々の部分の振舞い及び正しいシーケンスを,ソフトウェア(カウント手順,キー手

順)又は外部の監視装置を用いて監視する。プログラム中に確認点を正確に置くことが重要である。

A.9.4 プログラムシーケンスの時間的監視と論理的監視との組合せ

注記 この技術及び手法は,JIS C 0508-2の表A.10及び表A.11で引用されている。

目的:プログラムの個々の部分の振舞い及び正しいシーケンスを監視する。

説明:プログラムのシーケンスを正しく実行している場合だけ,プログラムシーケンスを監視する時間的

監視装置(例えば,ウォッチドッグタイマ)をリセットする。

A.9.5 オンラインチェックによる時間的監視

注記 この技術及び手法は,JIS C 0508-2の表A.10及び表A.11で引用されている。

目的:時間的監視機能のフォールトを検出する。

説明:時間的監視機能を始動時にチェックし,時間的監視機能が正しく働く場合だけ始動が可能となる。

例えば,(時間的監視として使う)熱センサを,始動時に加熱した抵抗器によってチェックするこ

とができる。

A.10 換気及び加熱

注記 この技術及び手法は,JIS C 0508-2の表A.16及び表A.18で引用されている。

全般:安全関連系の場合,換気又は加熱の制御及び/又は監視。

A.10.1 温度センサ

目的:システムが仕様範囲外で運転を開始する前に,温度の上限又は下限の超過を検出する。

説明:温度センサが,E/E/PE安全関連系の最重要点における温度を監視する。温度が指定範囲から外れる

前に,緊急制御動作を行う。

20

C 0508-7:2017 (IEC 61508-7:2010)

A.10.2 ファン制御

目的:ファンの正しくない動作を検出する。

説明:ファンが正しく動作しているか監視する。ファンが正常に動作していない場合は,保全手段(根本

的手段,又は緊急制御動作)をとる。

A.10.3 温度ヒューズを介しての安全遮断の起動

目的:システムが温度仕様範囲外で動作する前に安全関連系を停止する。

説明:安全関連系を停止させるために,温度ヒューズを用いる。PE系の場合,この停止は,緊急制御動作

に必要な全ての情報を格納するパワーダウン処理によって開始する。

A.10.4 温度センサからの逸脱メッセージ及び条件付きアラーム

目的:安全関連系が温度仕様範囲外で動作していることを示す。

説明:温度を監視し,温度が指定範囲外の場合,アラームを出力する。

A.10.5 強制空冷の接続及び状態表示

目的:強制空冷によって過熱を防止する。

説明:温度を監視し,温度が指定の限界値よりも高くなったとき強制空冷を開始する。使用者には,その

状態を通知する。

A.11 通信及び大容量記憶装置

全般:外部情報源と大容量記憶装置との通信中の故障を管理する。

A.11.1 通信線からの電力線の分離

注記 この技術及び手法は,JIS C 0508-2の表A.16で引用されている。

目的:大電流による通信線へのクロストークの誘導を最小限に抑える。

説明:電力線を,通信線から分離する。通信線上に電圧スパイクを誘導する可能性がある電界は,距離の

増加とともに減少する。

A.11.2 複数ラインの空間的分離

注記 この技術及び手法は,JIS C 0508-2の表A.16で引用されている。

目的:複数ラインの大きな電流による相互クロストークの誘導を最小限に抑える。

説明:二重化信号を伝送するラインは互いに分離する。複数ライン上に電圧スパイクを誘導する可能性が

ある電界は,距離の増加とともに減少する。この手法によって,共通原因故障も減少する。

A.11.3 電磁イミュニティの増大

注記1 この技術及び手法は,JIS C 0508-2の表A.16及び表A.18で引用されている。

目的:安全関連系への電磁干渉を最小限に抑える。

説明:次のいずれかに対して安全関連系の電磁イミュニティを増強するために,遮蔽,フィルタなどの設

計技術を用いる。

− 電力線又は信号ラインから,放射又は伝導する可能性がある電磁妨害

21

C 0508-7:2017 (IEC 61508-7:2010)

− 静電放電の結果生じる可能性がある電磁妨害

注記2 安全関連系に対するイミュニティの要求事項,及び工業用途の安全関連系機能(機能安

全)を運用するように意図された機器に対するイミュニティの要求事項は,IEC

61326-3-1及びIEC 61326-3-2を参照。

参考文献:

IEC/TR 61000-5-2:1997,Electromagnetic compatibility (EMC)−Part 5: Installation and mitigation guidelines

−Section 2: Earthing and cabling

Principles and Techniques of Electromagnetic Compatibility, Second Edition, C. Christopoulos, CRC Press,

2007, ISBN-10: 0849370353, ISBN-13: 978-0849370359

Noise Reduction Techniques in Electronic Systems. H. W. Ott, John Wiley Interscience, 2nd Edition, 1988

EMC for Product Designers. T. Williams, Newnes, 2007, ISBN 0750681705

Grounding and Shielding Techniques in Instrumentation, 3rd edition, R. Morrison. Wiley-Interscience, New

York, 1986, ISBN-10: 0471838055, ISBN-13: 978-0471838050

A.11.4 相反信号伝送

注記 この技術及び手法は,JIS C 0508-2の表A.7及び表A.16で引用されている。

目的:複数信号伝送ラインにおける同一誘導電圧を検出する。

説明:全ての二重化情報を,相反信号(例えば,論理1及び0)とともに伝送する。共通原因故障(例え

ば,電磁放射による)は,相反信号の比較器によって検出できる。

参考文献:

Elektronik in der Sicherheitstechnik. H. Jürs, D. Reinert, Sicherheitstechnisches Informations- und Arbeitsblatt

330220, BIA-Handbuch. 20. Lfg. V/93, Erich Schmidt Verlag, Bielefeld.

http://www.bgia-handbuchdigital.de/330220

A.12 センサ

全般:安全関連系のセンサの故障を管理する。

A.12.1 基準センサ

注記 この技術及び手法は,JIS C 0508-2の表A.13で引用されている。

目的:センサの正しくない動作を検出する。

説明:プロセスセンサの動作を監視するために独立基準センサを用いる。プロセスセンサの故障を検出す

るために,基準センサによって全ての入力信号を適切な時間間隔でチェックする。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

A.12.2 正作動スイッチ

注記 この技術及び手法は,JIS C 0508-2の表A.13で引用されている。

目的:スイッチカムと接点との間の直接的機械的接続によって,接点を開く。

説明:正作動スイッチは,スイッチカムと接点との間の直接的機械的接続によって,その通常閉の接点を

22

C 0508-7:2017 (IEC 61508-7:2010)

開く。これは,スイッチカムが動作位置にあるときは,常に,スイッチ接点が確実に開いているこ

とを確実にする。

参考文献:

Verriegelung beweglicher Schutzeinrichtungen. F. Kreutzkampf, K. Becker, Sicherheitstechnisches

Informations- und Arbeitsblatt 330210, BIA-Handbuch. 1. Lfg. IX/85, Erich Schmidt Verlag, Bielefeld

A.13 操作端(アクチュエータ)

全般:安全関連系の操作端の故障を管理する。

A.13.1 監視

注記 この技術及び手法は,JIS C 0508-2の表A.14で引用されている。

目的:アクチュエータの正しくない動作を検出する。

説明:アクチュエータの動作を監視する[例えば,リレーの正作動接点による監視(A.1.2参照)]。監視で

導入した冗長性は,緊急制御動作を開始させるために用いてもよい。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

Zusammenstellung und Bewertung elektromechanischer Sicherheitsschaltungen für Verriegelungseinrichtungen.

F. Kreutzkampf, W. Hertel, Sicherheitstechnisches Informations- und Arbeitsblatt 330212, BIA-Handbuch.

17. Lfg. X/91, Erich Schmidt Verlag, Bielefeld

A.13.2 複数のアクチュエータの相互監視

注記 この技術及び手法は,JIS C 0508-2の表A.14で引用されている。

目的:結果を比較することによって,アクチュエータのフォールトを検出する。

説明:複数のアクチュエータをそれぞれ,異なるハードウェアチャネルによって監視する。不一致が生じ

た場合,緊急制御動作を行う。

A.14 物理的環境に対する手法

注記 この技術及び手法は,JIS C 0508-2の表A.16及び表A.18で引用されている。

目的:故障の原因となる物理的環境(水,ほこり及び腐食性物質)の影響を防止する。

説明:装置のきょう(筐)体を,予期される環境に耐えるように設計する。

参考文献:

JIS C 0920 電気機械器具の外郭による保護等級(IPコード)

23

C 0508-7:2017 (IEC 61508-7:2010)

附属書B

(参考)

E/E/PE安全関連系のための技術及び手法の概要:

決定論的原因故障の回避(JIS C 0508-2及びJIS C 0508-3参照)

注記 この附属書の多くの技術はソフトウェアにも適用できるが,同一内容を附属書Cでは繰り返さ

ない。

B.1

一般的な手法及び技術

B.1.1 プロジェクトマネジメント

注記 この技術及び手法は,JIS C 0508-2の表B.1(E/E/PE系設計要求仕様中の過失を回避するため

の技法及び手段)〜表B.6(決定論的原因故障を回避するための技法及び手段の有効性)で引

用されている。

目的:安全関連系を開発及びテストするための組織モデル,並びに規則及び手法を採用することによっ

て,故障を回避する。

説明:最も重要で最善の手法は,次の事項である。

− 組織モデルの作成,特に品質保証の手引に記載されている品質保証に関するもの

− 相互プロジェクト及びプロジェクト固有の指針における,安全関連系の作成及び妥当性確認の

ための規則及び手法の確立

幾つかの重要な基本原理を,次に記載する。

− 設計組織の定義

・ 組織単位の業務及び責任

・ 品質保証部門の権限

・ 開発からの品質保証(内部検査)の独立

− シーケンス計画(活動モデル)の定義

・ 内部検査及びこれらのスケジューリングを含め,プロジェクトの運用中に関わる全ての活動

の決定

・ プロジェクトの更新

− 内部検査のための標準化したシーケンスの定義

・ 検査(検査理論)の計画,運用及び確認

・ サブ製品のためのリリースの仕組み

・ 繰返し検査による安全維持

− 構成管理

・ 版の管理及び確認

・ 部分改修の影響の検出

・ 部分改修後の整合性検査

− 品質保証手法の定量的評価の導入

・ 要求事項の獲得

・ 故障の統計

24

C 0508-7:2017 (IEC 61508-7:2010)

− コンピュータ支援の汎用方法,ツール及び要員訓練の導入

参考文献:

JIS Q 9001 品質マネジメントシステム−要求事項

注記 対応国際規格:ISO 9001:2008,Quality management systems−Requirements

JIS X 0145(規格群) 情報技術−プロセスアセスメント

注記 対応国際規格:ISO/IEC 15504 (all parts),Information technology−Process assessment

CMMI: Guidelines for Process Integration and Product Improvement, 2nd Edition. M.B. Chrissis, M. Konrad, S.

Shrum, Addison-Wesley Professional, 2006, ISBN-10: 0-3212-7967-0, ISBN-13: 978-0-3212-7967-5

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

Dependability of Critical Computer Systems 1. F. J. Redmill, Elsevier Applied Science, 1988, ISBN

1-85166-203-0

B.1.2 文書化

注記1 この技術及び手法は,JIS C 0508-2の表B.1〜表B.6で引用されている。

注記2 JIS C 0508-1の箇条5(文書化)及び附属書A(文書の構成事例)も参照。

目的:開発中の各手順を文書化することによって,故障を回避し,システム安全の評価を容易にする。

説明:運用容量及び安全性,並びに開発において全ての当事者が行った注意事項は,評価時に実証する必

要がある。開発時の注意事項を示すため,及びあらゆる時点における安全性の証拠の適合確認を保

証するため,特別重要事項を文書化する。

重要な共通手法は,指針及びコンピュータ支援の導入である。次に例を示す。

− 次の事項を満たす指針

・ グループ分け計画を規定する。

・ 内容のチェックリストを求める。

・ 文書の書式を決める。

− コンピュータ支援及び組織化されたプロジェクトライブラリの助けを借りた文書化の管理

個々の手法は,次による。

− 文書化における次のそれぞれの事項の分離

・ 要求事項

・ システム(使用者による文書化)

・ 開発(内部検査を含む。)

− 安全ライフサイクルに従った開発文書化のグループ分け

− 文書を編集する際にその基礎とすることができる,標準化した文書化モジュールの定義

− 文書化の構成部分の明瞭な識別

− 公式な改訂版の更新

− 次に示す,明確で理解しやすい説明手段の選択

・ 決定のための形式的な表記法

・ 意図の紹介,正当化及び表現のための自然言語

・ 例を示すための図形表現

・ 図形要素の意味の定義

25

C 0508-7:2017 (IEC 61508-7:2010)

・ 専門語の語彙集

参考文献:

IEC 61506:1997,Industrial-process measurement and control−Documentation of application software

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.1.3 E/E/PE系安全機能の安全以外の機能からの分離

注記 この技術及び手法は,JIS C 0508-2の表B.1及び表B.6で引用されている。

目的:システムの非安全関連部分が安全関連部分への好ましくない方法で影響を与えることを防止する。

説明:安全関連系と非安全関連系との分離が可能かどうかを,仕様内において決めることが望ましい。こ

れら二つの部分のインタフェースについて,明確な仕様を記述することが望ましい。明確に分離す

ることによって,安全関連系のテストのための労力を軽減することになる。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.1.4 多様性のあるハードウェア

注記 この技術及び手法は,JIS C 0508-2の表A.15,表A.16及び表A.18で引用されている。

目的:故障の割合及び種類が異なる種々の構成部品を用いて,EUCの運転中の決定論的原因故障を検出す

る。

説明:安全関連系の種々のチャネルには,異なる種類の構成部品を用いる。こうすることによって,共通

原因故障(例えば,過電圧,電磁妨害)の確率が下がり,そのような故障を検出する確率が上がる。

要求される機能を実行するための別の手段,例えば,別の物理的原理がある場合,同じ問題を解

くための他の方法を得ることができる。多様性には,幾つかの方法がある。機能多様性は,同じ結

果を達成するために異なるアプローチを用いる。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.2

E/E/PE系設計要求仕様

全般:可能な限り,完全で,間違い及び矛盾がなく,かつ簡単に検証できる仕様を作成する。

B.2.1 構造化仕様

注記 この技術及び手法は,JIS C 0508-2の表B.1及び表B.6で引用されている。

目的:部分的要求事項の階層構造を作成することによって,複雑さを軽減する。要求事項間のインタフェ

ース故障を回避する。

説明:この技術は,機能仕様を部分的要求事項に組み替えて,部分的要求事項間にできるだけ単純で目に

見える関係が存在するようにする。この解析は,小さく明白な部分的要求事項が区別されるように

なるまで継続的に詳細化する。最終詳細化の結果は,完全な要求事項の仕様の枠組みを定める部分

的要求事項の階層構造である。この方法は,部分的要求事項のインタフェースに重点を置くもので

26

C 0508-7:2017 (IEC 61508-7:2010)

あり,インタフェース故障を回避するために特に効果的である。

参考文献:

ESA PSS 05-02, Guide to the user requirements definition phase, Issue 1, Revision 1, ESA Board for Software

Standardisation and Control (BSSC), ESA, Paris, March 1995,

ftp://ftp.estec.esa.nl/pub/wm/wme/bssc/PSS0502.pdf

Structured Analysis and System Specification. T. De Marco, Yourdon Press, Englewood Cliffs, 1979, ISBN-10:

0138543801, ISBN-13: 978-0138543808

B.2.2 形式手法

注記1 具体的な形式手法の詳細は,C.2.4を参照。

注記2 この技術及び手法は,JIS C 0508-2の表B.1,表B.2(E/E/PE系の設計及び開発中のフォール

トの誘引を回避するための技法及び手段)及び表B.6で引用されている。

目的:形式手法によって,数学的推論の原則を,技術システムの仕様化及び実装に適用し,仕様化又は実

装の完璧さ,一貫性及び正確さを向上させる。

説明:形式手法は,仕様化及び/又は実装のフェーズで,システム説明書を作成する手段を提供する。こ

れらの形式的な説明書は,システム機能及び/又はシステム構造の数学的モデルである。

したがって,基礎システムの理解を深めるような明確なシステム説明書を作成できる(例えば,

オートマトンの全ての状態を,その初期状態,入力及びオートマトンの遷移方程式で記述する。)。

適切な形式手法の選択は,システム,その開発プロセス及び数学的モデルを使用できる範囲につ

いて完全な理解を要する,困難な作業である(注記3,注記4及び注記5参照)。

注記3 モデル(特性)の重要な定理は,シミュレーション,すなわち,選択されたシステム動

作の観察を超える信頼性を与えるシステムについての保証となる。

注記4 形式手法の不利な点として,次の点が考えられる。

− 抽象度の固定

− 所与の段階で関わりのある全ての機能性を把握することの限界

− 実装技術者がモデルを理解することの困難さ

− モデルを開発,解析及びシステムのライフサイクル全体にわたり保全するための,

非常な努力

− モデルの構築及び解析を支援するための効率的ツール入手の可能性

− モデルの開発及び解析の能力をもつスタッフの有無

注記5 形式手法コミュニティは,フォールトに対するシステム堅ろう(牢)性を強調しないで

システムの目標機能をモデル化することに明らかに注視している場合がある。したがっ

て,システム堅ろう(牢)性を含む個別の形式手法を選択する必要がある。

参考文献:

Formal Specification: Techniques and Applications. N.Nissanke, Springer-Verlag Telos, 1999, ISBN-10:

1852330023

B.2.3 準形式手法

注記1 JIS C 0508-3の表B.7(準形式手法)は,他の準形式ソフトウェア関連技術によって,この附

属書を拡張しており,この表の“参照先”は,次の項目を示している。

27

C 0508-7:2017 (IEC 61508-7:2010)

− 論理及び機能ブロック図:JIS B 3503参照

− シーケンス図:JIS B 3503参照

− データフロー図:C.2.2参照

− 有限状態機械及び状態遷移図:B.2.3.2参照

− タイムペトリネット:B.2.3.3参照

− エンティティ関連属性データモデル:B.2.4.4参照

− メッセージシーケンスチャート:C.2.14参照

− 判定表又は真理値表:C.6.1参照

目的:一部の間違い,脱落及び誤った挙動が検出できるように,仕様の部分を明確にかつ一貫性をもって

表現する。

注記2 この技術及び手法は,JIS C 0508-2の表B.1,表B.2及び表B.6並びにJIS C 0508-3の表A.1

(ソフトウェア安全要求仕様),表A.2(ソフトウェア設計及び開発−ソフトウェアアーキテ

クチャ設計),表A.4(ソフトウェア設計及び開発−詳細設計),表B.7(準形式手法),表C.1

(決定論的安全度に関する特性−ソフトウェア安全要求仕様),表C.2(決定論的安全度に関

する特性−ソフトウェア設計及び開発−ソフトウェアアーキテクチャ設計),表C.4(決定論

的安全度に関する特性−ソフトウェア設計及び開発−詳細設計)及び表C.17(詳細特性−準

形式手法)で引用されている。

参考文献:

JIS B 3503:2012 プログラマブルコントローラ−プログラム言語

B.2.3.1 一般事項

目的:設計が仕様に適合していることを証明する。

説明:準形式手法は,システムの開発におけるある段階,すなわち,仕様作成,設計又はコーディングに

おいて,システムの説明書を開発する手法を提供する。説明書は,場合によっては,機械によって

解析することができるか,又はシステムの挙動の様々な面を表示するためにアニメーション化する

ことができる。アニメーションは,システムが真の要求事項及び規定の要求事項を満たしているこ

との確信を高めることができる。

B.2.3.2及びB.2.3.3において,二つの準形式手法を説明する。

B.2.3.2 有限状態機械,及び状態遷移図

注記 この技術及び手法は,JIS C 0508-3の表B.5(モデリング),表B.7,表C.15(詳細特性−モデ

リング)及び表C.17(詳細特性−準形式手法)で引用されている。

目的:システムの制御構造をモデル化する,適合確認する,規定する又は実装する。

説明:多くのシステムは,システムの状態,入力,及び動作によって説明することができる。したがって,

システムは,状態“S1”にあるとき,入力“I”を受けると,動作“A”を行い,状態“S2”に移動

する。全ての状態において全ての入力によるシステムの動作を説明することで,システムを完全に

説明することができる。この結果から得られるシステムのモデルは,有限状態機械(又は,有限状

態オートマトン)と呼ばれる。これは,システムが一つの状態から別の状態へどのように移動する

かを示す,いわゆる状態遷移図として,又は次元が状態及び入力であって,指定状態にあるときに

入力を受信したことによって起こる動作及び新状態をマトリックスセルが収容する,マトリックス

28

C 0508-7:2017 (IEC 61508-7:2010)

として描かれる場合がある。

システムが複雑であるか,又は自然構造をもっている場合,これは層状有限状態機械に反映する

ことができる。状態図は,ネスト化された状態(対象状態が,平行して展開でき,また,一部の点

では単一状態に再結合する可能性のある二つ以上のサブステートに分かれる。)が可能な状態遷移図

の一種である。これは,状態遷移表記の表現力を高めるものであるが,安全関連系では望ましくな

い余分な複雑さが加わる可能性がある。状態図は,形式(数学的)仕様をもつ。状態遷移図は,シ

ステム全体又はシステム内の一部の対象又は要素に適用できる。

有限状態機械として表現できる仕様又は設計は,次の事項について確認することができる。

− 完全性(システム又は対象は,それぞれの状態における,全ての入力の一つ一つに対して,一

つの動作及び新状態をもつ必要がある。)

− 一貫性(全ての状態及び入力の組合せに対して,唯一の状態遷移が可能である。)

− 到達性(一連の入力によって,ある状態からもう一方の状態へと変えることが可能か可能でな

いか。)

− 無限ループ又は行き止まり状態がないこと

これらは,重大なシステムの重要な特性である。これらのチェックを支援するツールは容易に開

発することができ,有限状態オートマトンに基づく各種モデル(形式言語,ペトリネット,マルコ

フ図など)が利用できる。有限状態機械の実装を適合確認する,又は有限状態機械のモデルをアニ

メーション化するために,テストケースを自動的に生成するアルゴリズムも存在する。状態遷移図

及び状態図は,図の作画及びチェックを可能とし,記述した状態機械を実装するコードを生成する

ためのツールによって,広い範囲で用いられている。

これらは,故障確率計算にも使用できる。B.6及びC.6を参照。

参考文献:

Introduction to Automata Theory, Languages, and Computation (3rd Edition). J. Hopcroft, R. Motwani, J.

Ullman, Addison-Wesley Longman Publishing Co, 2006, ISBN: 0321462254

Securisation des architectures informatiques. Jean-Louis Boulanger, Hermès−Lavoisier, 2009, ISBN:

978-2-7462-1991-5

B.2.3.3 タイムペトリネット

注記 この技術及び手法は,JIS C 0508-3の表B.5,表B.7,表C.15及び表C.17で引用されている。

目的:システム挙動の関連面をモデル化し,解析及び再設計を通じて安全性及び運転時の要求事項を評価

し,可能な限り改善する。

説明:ペトリネットは,有限状態オートマトンの特殊な事例である。ペトリネットは,同時並行性を示

し,非同期挙動をもつ複数のシステムにおける情報及び制御のフローを表すのに適したグラフ理論

モデル群に属する。

ペトリネットは,場所及び遷移のネットワークである。場所は“マークを付けられる”ことも,

“マークを付けられない”こともある。遷移は,これに対する入力場所の全てにマークが付けられ

ているとき,“可能”となる。可能となった場合,遷移が発生することが許容される(必ずしも発生

しなくてよい。)。遷移が発生した場合,遷移に対する入力場所のマークが消され,それに代わって,

遷移からの各出力場所にマークが付けられる。

潜在危険は,モデルにおける個々の状態(マーキング)として表すことができる。ペトリネット

29

C 0508-7:2017 (IEC 61508-7:2010)

モデルは,システムのタイミング特性に合わせて拡張することができる。“古典的”なペトリネット

は制御フロー面に集中しているが,データフローをモデルに組み込むために幾つかの拡張が提案さ

れている。

これらは,故障確率計算をするために,モンテカルロシミュレーションの実施に当たって,非常

に効率的な支援もする。B.6.6.8参照。

参考文献:

Timed Petri Nets: Theory and Application. Jiacun Wang, Springer, 1998, ISBN 0792382706

Securisation des architectures informatiques. Jean-Louis Boulanger, Hermès−Lavoisier, 2009, ISBN:

978-2-7462-1991-5

B.2.4 コンピュータ支援仕様作成ツール

注記 この技術及び手法は,JIS C 0508-2の表B.1及び表B.6並びにJIS C 0508-3の表A.1,表A.2,

表C.1及び表C.2で引用されている。

B.2.4.1 一般事項

目的:曖昧さ及び完全性の自動検出を容易にするために,形式仕様作成技術を用いる。

説明:この技術は,一貫性及び完全性を評価するために自動的に検査することができる,データベースの

形で仕様を作成する。仕様作成ツールは,使用者に対して規定されたシステムの様々な面をアニメ

ーション化することができる。一般に,この技術は,仕様の作成だけでなく,プロジェクトライフ

サイクルの設計及び他のフェーズの支援もする。仕様作成ツールは,B.2.4.2及びB.2.4.3に従って

分類できる。

B.2.4.2 特定の方法のためとして限定されないツール

目的:関連する部分とのつながり及び入力指示を与えることによって,使用者が優れた仕様を書く手助け

をする。

説明:仕様作成ツールは,使用者の定型業務の一部を引き継ぎ,プロジェクト管理を支援する。特別な仕

様作成方法論を強要するものではない。方法に関して比較的独立しているため,使用者は大幅な自

由が許されるが,仕様を作成する際に必要な専門化された支援に欠ける。このため,システムとの

融和がかなり難しい。

B.2.4.3 階層的解析を伴うモデル指向手順

目的:仕様の不完全さ,曖昧さ及び矛盾を避ける。例えば,動作の説明と様々な水準の抽象化におけるデ

ータとの間の一貫性を確実にすることによって,使用者が優れた仕様を書く手助けをする。

説明:この方法は,様々な水準の抽象化(精度)において,希望するシステム(構造化解析)を機能的に

表現する。このようなモデルは,数多く存在する。有限オートマトンは,離散又はデジタル系の展

開を記述するために広く利用されているモデルの一種である。微分方程式は概念的には似ているが,

連続又はアナログ系を対象としている。様々な水準における解析は,動作及びデータの両方に作用

する。曖昧さ及び完全性の評価は,階層水準間においても,同一水準の二つの機能ユニット(モジ

ュール)間においても可能である(例えば,システムモデルの状態は,初期状態,入力及びオート

マトンの遷移方程式で記述される。)

30

C 0508-7:2017 (IEC 61508-7:2010)

注記 モデルに基づく記述の問題点は,抽象化の水準,所定の段階で関わりのある全ての機能性を把

握する限界,実務者がモデルを理解することの難しさ(構文読取りから理解に至る。),モデル

を開発,解析及びシステムのライフサイクル全体にわたる保全のための大変な努力,モデル構

築及び解析を支援する効率的ツール入手の可能性(こうしたツールの開発は,大変な努力を要

する仕事である。),並びにモデルの開発及び解析能力をもつスタッフの投入の可能性といえる。

参考文献:

System requirements analysis. Jeffrey O. Grady, Academic Press, 2006, ISBN 012088514X, 9780120885145

B.2.4.4 エンティティ関連属性データモデル

目的:システム内のエンティティ及びこれらの間の関係に焦点を当てることによって,使用者が優れた仕

様を書く手助けをする。

説明:希望のシステムは,オブジェクト及びこれらの関係の集合として説明できる。ツールを用いること

で,システムによってどの関係が解釈されるかの決定が可能となる。一般に,これらの関係を用い

ることによって,オブジェクトの階層構造,データフロー,データ間の関係,及びどのデータが製

造工程に従属するかを記述することができる。古典的な手順は,工程管理分野まで拡張されている。

検査能力及び使用者支援は,図示された関係の種類に依存する。一方,可能な表現方法が非常にた

くさんあるため,この技術の利用は複雑となる。

参考文献:

Software Requirements: Practical Techniques for Gathering and Managing Requirements Throughout the

Product Development Cycle. Karl Eugene Wiegers, Microsoft Press, 2003, ISBN 0735618798,

9780735618794

B.2.4.5 誘因及び応答

目的:刺激・反応関係を明確にすることによって,使用者が優れた仕様を書く手助けをする。

説明:システムのオブジェクト間の関係を“誘因”及び“応答”という表記法で規定する。オブジェクト,

関係,特性及び構造を表す言語要素を含む,単純で容易に拡張できる言語を用いる。

B.2.5 チェックリスト

注記 この技術及び手法は,JIS C 0508-2の表B.1,表B.2及び表B.6並びにJIS C 0508-3の表A.10

(機能安全評価),表B.8(静的解析),表C.10(決定論的安全度に関する特性−機能安全評価)

及び表C.18(決定論的安全度に関する特性−静的解析)で引用されている。

目的:詳細な要求事項を定めることなしに包括的なカバー率を確保するため,安全ライフサイクルフェー

ズによってシステムの全ての重要な側面に対して注意を向け,及び重要な評価を管理する。

説明:チェックリストは,それを実施する人が回答する1組の質問である。これらの質問の多くは,一般

的性質のものであり,アセッサは,これらの質問を,評価の対象となる個々のシステムに最も適し

ているものと解釈する必要がある。チェックリストは,全般的に全てのE/E/PE系安全及びソフトウ

ェア安全のライフサイクルフェーズに用いることができ,特に,機能安全評価を支援するツールと

して有用である。

妥当性確認を受けるシステムの広範囲のばらつきに対処するために,ほとんどのチェックリスト

は,多くの形式のシステムに適用できる質問を含んでいる。したがって,用いるチェックリストは,

31

C 0508-7:2017 (IEC 61508-7:2010)

取り扱うシステムに関係がなく,無視することが望ましい質問を含むこともある。同様に,具体的

に取り扱うシステムに対して,特に当てはまる質問を,標準的なチェックリストに補足する必要が

ある場合もある。

いずれの場合にも,チェックリストの使用は,その大半が,チェックリストを選択して適用する

技術者の専門的技術及び判断によって決まることは明らかである。したがって,選択したチェック

リストに関して,技術者による決定,及び追加又は必要以上の質問は,完全に文書化し,正当化す

ることが望ましい。目的は,チェックリストの適用を見直すことができること,及び異なる基準を

用いない限り同一結果が得られることを確実にすることである。

チェックリストを完成する上で,できる限り簡潔にすることが目標となる。広範囲にわたって正

当化が必要な場合は,追加の文書類を引用することによって,これを達成することが望ましい。各

質問に対する結果を文書化するために,合格,不合格及び未決,又はこれらに似た限られた応答の

一群を用いることが望ましい。この簡潔さは,チェックリスト評価の結果についての全般的結論に

到達するための手順を大幅に単純化する。

参考文献:

IEC 60880:2006,Nuclear power plants−Instrumentation and control systems important to safety−Software

aspects for computer-based systems performing category A functions

The Art of Software Testing, Second Edition. G. Myers et al., Wiley & Sons, New York, 2004, ISBN

0471469122, 9780471469124

Software Quality Assurance: From Theory to Implementation. Daniel Galin, Pearson Education, 2004, ISBN

0201709457, 9780201709452

JIS C 0452(規格群) 電気及び関連分野−工業用システム,設備及び装置,並びに工業製品−構造化

原理及び参照指定

注記 対応国際規格:IEC 61346 (all parts),Industrial systems, installations and equipment and industrial

products−Structuring principles and reference designations

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

Risk Assessment and Risk Management for the Chemical Process Industry. H.R. Greenberg, J.J. Cramer, John

Wiley and Sons, 1991, ISBN 0471288829, 9780471288824

B.2.6 仕様の検査

注記 この技術及び手法は,JIS C 0508-2の表B.1及び表B.6で引用されている。

目的:仕様の不完全さ及び矛盾を避ける。

説明:検査は,仕様の様々な品質を独立したチームによって評価する一般的技術である。検査チームは作

成者に質問を出し,作成者はこれらの質問に対して,満足のいくように回答する必要がある。調査

は,仕様の作成に関わらなかったチーム(可能な場合)が実施することが望ましい。要求する独立

性は,システムに要求する安全度水準によって決める。独立した検査者は,更に別の仕様を参照す

ることなく,システムの動作機能を議論の余地がない形に再構成することができる能力をもってい

ることが望ましい。さらに,検査者は動作及び組織的な手法の関連安全性及び技術面の全てをカバ

ーしていることを確認する必要がある。この手順は,これ自体が,実践上で非常に有効であること

が証明されている。

32

C 0508-7:2017 (IEC 61508-7:2010)

参考文献:

IEC 61160:2005,Design review

The Art of Software Testing, Second Edition. G. Myers et al., Wiley & Sons, New York, 2004, ISBN

0471469122, 9780471469124

Software Quality Assurance: From Theory to Implementation. D. Galin, Pearson Education, 2004, ISBN

0201709457, 9780201709452

B.3

E/E/PE系の設計及び開発

全般:仕様に従って安全関連系の安定した設計を行う。

B.3.1 指針及び規格の適合

注記 この技術及び手法は,JIS C 0508-2の表B.2で引用されている。

目的:適用分野規格(この規格では規定していない。)に適合させる。

説明:安全関連系の設計では,指針に準拠することが望ましい。これらの指針は,第一に,事実上,故障

がない安全関連系を導くものであり,第二に,これ以降の安全妥当性確認を容易にするものである

ことが望ましい。指針は,汎用的に妥当でも,あるプロジェクトに固有のものでも,又は単一フェ

ーズに固有のものでもよい。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.3.2 構造化設計

注記 この技術及び手法は,JIS C 0508-2の表B.2及び表B.6で引用されている。

目的:部分的要求事項の階層構造を作成することによって,複雑さを軽減する。要求事項間のインタフェ

ース故障を回避する。適合確認を単純化する。

説明:ハードウェアを設計する場合には,具体的な基準又は方法を用いることが望ましい。例えば,次の

事項を要求する場合がある。

− 階層的に構造化した回路設計

− 製造後にテスト済みの回路部品の使用

同様に,ソフトウェアを設計するときに構造化チャートを用いることによって,ソフトウェアモ

ジュールの明確な構造を作り出すことができる。この構造は,モジュール間の互いの関わり方,モ

ジュール間でやりとりする正確なデータ及びモジュール間に存在する詳細制御を示す。

参考文献:

JIS C 0452(規格群) 電気及び関連分野−工業用システム,設備及び装置,並びに工業製品−構造化

原理及び参照指定

注記 対応国際規格:IEC 61346 (all parts),Industrial systems, installations and equipment and industrial

products−Structuring principles and reference designations

Software Engineering for Real-time Systems. J. E. Cooling, Pearson Education, 2003, ISBN 0201596202,

9780201596205

Software Design. D. Budgen, Pearson Education, 2003, ISBN 0201722194, 9780201722192

33

C 0508-7:2017 (IEC 61508-7:2010)

An Overview of JSD, J. R. Cameron, IEEE Trans SE-12 No. 2, February 1986

Structured Development for Real-Time Systems (3 Volumes). P. T. Yourdon, P. T. Yourdon Press, 1985

Structured Development for Real-Time Systems (3 Volumes). P. T. Ward, S. J. Mellor, Yourdon Press, 1985

Applications and Extensions of SADT. D. T. Ross, Computer, 25-34, April 1985

Essential Systems Analysys. St. M. McMenamin, F. Palmer, Yourdon Inc, 1984

Structured Analysis (SA): A language for communicating ideas. D. T. Ross, Software Eng, Vol. SE-3 (1), 16-34

B.3.3 十分な実績のある構成部品の使用

注記 この技術及び手法は,JIS C 0508-2の表B.2及び表B.6で引用されている。

目的:固有の特性をもつ構成部品を用いることによって,多数の初回フォールト及び未検出フォールトの

リスクを低減する。

説明:十分な実績のある構成部品の選定は,要素の信頼性に応じた安全性を考慮して(例えば,高い安全

要求事項に適合する,運用することによってテストした物理的装置の使用,又は安全なメモリだけ

への安全関連プログラムの格納),製造業者が実施する。メモリの安全性は,不正なアクセス及び

環境の影響(電磁両立性,放射など)並びに故障発生時の要素の応答を考慮したものである。

参考文献:

IEC 61163-1:2006,Reliability stress screening−Part 1: Repairable assemblies manufactured in lots

B.3.4 モジュール化

注記 この技術及び手法は,JIS C 0508-2の表B.2及び表B.6で引用されている。

目的:サブシステム間のインタフェースに関わる複雑さを軽減し,故障を回避する。

説明:全てのサブシステムは,設計の全ての水準において明瞭に定義し,かつ,サイズを制限する(少数

の機能とする。)。サブシステム間のインタフェースは,可能な限り単純なものとし,横断的側面(す

なわち,共有データ,情報の交換)は最小限に抑える。個々のサブシステムの複雑さも制限する。

参考文献:

The Art of Software Testing, Second Edition. G. Myers et al., Wiley & Sons, New York, 2004, ISBN

0471469122, 9780471469124

Software Engineering for Real-time Systems. J. E. Cooling, Pearson Education, 2003, ISBN 0201596202,

9780201596205

Software Reliability−Principles and Practices. G. J. Myers, Wiley-Interscience, New York, 1976, ISBN-10:

0471627658, ISBN-13: 978-0471627654

B.3.5 コンピュータ支援設計ツール

注記 この技術及び手法は,JIS C 0508-2の表B.2及び表B.6並びにJIS C 0508-3の表A.4及び表C.4

で引用されている。

目的:設計手順を,より系統的に実施する。既に利用可能でテスト済みの適切な自動構造要素を含む。

説明:コンピュータ支援設計ツール(CAD)は,これが利用できて,システムの複雑さによって正当化で

きる場合は,ハードウェア及びソフトウェアの両方の設計時に用いることが望ましい。これらのツ

ールの正当性は,特定のテスト,広範囲にわたる良好な使用実績,又は設計中の個々の安全関連系

に対するツールの出力に関する独立した適合確認によって実証することが望ましい。

34

C 0508-7:2017 (IEC 61508-7:2010)

支援ツールは,その統合度に合わせて選択することが望ましい。この意味で,ツールは,一方の

ツールからの出力が,その次のツールへの自動入力に適したコンテンツ及びフォーマットをもち,

これによって中間結果の再加工時にヒューマンエラーを持ち込む可能性を最小限に抑えるように協

働する場合,統合されているといえる。

参考文献:

Overview of Technology Computer-Aided Design Tools and Applications in Technology Development,

Manufacturing and Design. W. Fichtner, Journal of Computational and Theoretical Nanoscience, Volume 5,

Number 6, June 2008, pp. 1089-1105 (17)

The Electromagnetic Data Exchange: Much more than a Common Data Format. P.E. Frandsen et al. In

Proceeding of the 2nd European Conference on Antennas and Propagation. The Institution of Engineering

and Technology (IET), 2007, ISBN 978-0-86341-842-6

Software engineering: Update. Ian Sommerville, Addison-Wesley Longman, Amsterdam; 8th ed., 2006, ISBN

0321313798, 9780321313799

Software Engineering. Ian Sommerville, Pearson Studium, 8. Auflage, 2007, ISBN 3827372577,

9783827372574

B.3.6 シミュレーション

注記 この技術及び手法は,JIS C 0508-2の表B.2,表B.5(E/E/PE系の安全妥当性確認中のフォール

トを回避するための技法及び手段)及び表B.6で引用されている。

目的:電気回路及び電子回路について,構成部品の機能的性能及び設計の正しさの両方を,系統的かつ完

全な検査を実施する。

説明:安全関連系回路の機能を,ソフトウェア挙動モデルを介して,コンピュータ上でシミュレーション

する。回路の各構成部品は,これ自体のシミュレーションされた挙動をもっており,これらを接続

した回路の応答は,各構成部品の限界データを確認することによって検査する。

B.3.7 検査(レビュー及び解析)

注記 この技術及び手法は,JIS C 0508-2の表B.2及び表B.6で引用されている。

目的:仕様と実装との間の不一致を明らかにする。

説明:安全関連系に規定した機能を調査及び評価し,安全関連系が仕様の要求事項に適合していることを

確実にする。製品の実装及び使用に関する疑わしい点がある場合は,これらを解決するように文書

化する。ウォークスルーとは逆に,検査の実施においては,作成者は受動的であり,検査者は能動

的である。

参考文献:

IEC 61160:2005,Design review

Software engineering: Update. Ian Sommerville, Addison-Wesley Longman, Amsterdam; 8th ed., 2006, ISBN

0321313798, 9780321313799

Software Engineering. Ian Sommerville, Pearson Studium, 8. Auflage, 2007, ISBN 3827372577,

9783827372574

The Art of Software Testing, Second Edition. G. Myers et al., Wiley & Sons, New York, 2004, ISBN

0471469122, 9780471469124

35

C 0508-7:2017 (IEC 61508-7:2010)

ANSI/IEE 1028:1997,IEEE Standard for software reviews

Dependability of Critical Computer Systems 3. P. G. Bishop et al., Elsevier Applied Science, 1990, ISBN

1-85166-544-7

B.3.8 ウォークスルー

注記 この技術及び手法は,JIS C 0508-2の表B.2及び表B.6で引用されている。

目的:仕様と実装との間の不一致を明らかにする。

説明:安全関連系の草案で規定した機能を調査し,評価して,安全関連系がこの仕様の要求事項に適合し

ていることを確実にする。製品の実現及び使用に関する疑わしい点及び潜在的弱点がある場合は,

これらを解決するように文書化する。検査とは逆に,ウォークスルーにおいては,作成者は能動的

であり,検査者は受動的である。

参考文献:

Software engineering: Update. Ian Sommerville, Addison-Wesley Longman, Amsterdam; 8th ed., 2006, ISBN

0321313798, 9780321313799

Software Engineering. Ian Sommerville, Pearson Studium, 8. Auflage, 2007, ISBN 3827372577,

9783827372574

ANSI/IEEE 1028:1997,IEEE Standard for software reviews

Dependability of Critical Computer Systems 3. P. G. Bishop et al., Elsevier Applied Science, 1990, ISBN

1-85166-544-7

Methodisches Testen von Programmen. G. J. Myers, Oldenbourg Verlag, München, Wien, 1987

B.4

E/E/PE系の運用及び保全手順

全般:安全関連系の運用及び保全中の故障を回避する手助けとなる手順を開発する。

B.4.1 運用及び保全指示書

注記 この技術及び手法は,JIS C 0508-2の表B.4(E/E/PE系の運用及び保全手順の実施中のフォー

ルト及び故障を回避するための技法及び手段)で引用されている。

目的:安全関連系の運用及び保全中の間違いを避ける。

説明:使用指示書は,安全関連系の使用方法及び保全方法に関する必須情報を記載する。特別な場合,こ

れらの指示書には,安全関連系の据付方法全般についての例も含める。全ての指示は,容易に理解

できるようにする必要がある。複雑な手順及び依存関係を説明するためには,図表を用いることが

望ましい。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.4.2 使いやすさ

注記 この技術及び手法は,JIS C 0508-2の表B.4で引用されている。

目的:安全関連系の運用中の複雑さを軽減する。

説明:安全関連系の正しい運用は,ある程度は人間の操作によって決まる。安全関連系の開発者は,該当

36

C 0508-7:2017 (IEC 61508-7:2010)

するシステム設計及び作業場の設計を考慮することによって,次の事項を確実にする必要がある。

− 人間の操作の必要性を,絶対的最小限に制限する。

− 必要な操作はできる限り単純にする。

− オペレータの誤りから生じる危害の可能性を最小限に抑える。

− 操作装置及び指示装置は,人間工学的要求事項に従って設計する。

− 操作装置は単純で,十分なラベル表示によって,直感的に使用できるものとする。

− オペレータが,極端な状況においても,過度な緊張を強いられることがない。

− 被訓練使用者の知識水準及び動機付け状態に応じて,操作手順及び操作装置についての訓練を

行う。

B.4.3 保全のしやすさ

注記 この技術及び手法は,JIS C 0508-2の表B.4で引用されている。

目的:安全関連系の保全手順を単純化し,有効な診断及び修理に必要な手法を設計する。

説明:予防保全及び修理は,多くの場合,困難な環境下で,期限に押されながら実施される。したがって,

安全関連系の開発者は,次の事項を確実にすることが望ましい。

− 安全関連保全処置は極力必要ではないようにし,理想的には,全く必要でないようにする。

− 不可避の修理のために,十分で,有効な,取り扱いやすい診断ツールを含め,ツールは全ての

必要なインタフェースを含むことが望ましい。

− 別の診断ツールを開発するか,又は入手が必要になった場合,これらを適時に入手できること

が望ましい。

B.4.4 運用の可能性の制限

注記 この技術及び手法は,JIS C 0508-2の表B.4及び表B.6で引用されている。

目的:通常使用者による運用可能性を減少させる。

説明:このアプローチは,次の事項によって,運用可能性を減少させる。

− 運用を特別な運転モード内に制限する,例えば,キースイッチによる。

− 運転要素の数を制限する。

− 一般的に可能な運転モードの数を制限する。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.4.5 熟練運転員だけによる運用

注記 この技術及び手法は,JIS C 0508-2の表B.4及び表B.6で引用されている。

目的:誤用によって発生する運転時の故障を回避する。

説明:安全関連系の運転員は,安全関連系の複雑さ及び安全度水準に適した水準まで訓練する。訓練に

は,製造工程の背景の学習及び安全関連系とEUCとの間の関係を知ることが含まれる。

参考文献:

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

37

C 0508-7:2017 (IEC 61508-7:2010)

B.4.6 運転員の間違いに対する保護

注記 この技術及び手法は,JIS C 0508-2の表B.4及び表B.6で引用されている。

目的:運転員の全ての種類の間違いからシステムを保護する。

説明:誤入力(値,時間など)を,確からしさのチェック又はEUCの監視によって検出する。これらの

装置を設計に組み込むためには,入力の種類を考え,どのような入力を許容するかを,非常に早い

段階で定める必要がある。

B.4.7 (不使用)

B.4.8 改変からの保護

注記 この技術及び手法は,JIS C 0508-2の表A.17(決定論的運用フォールトを管理するための技法

及び手段)及び表A.18で引用されている。

目的:安全関連系を,技術的手段によるハードウェアの改変ができないように保護する。

説明:改変又は改ざんを,例えば,センサ信号についての確からしさのチェック,技術的処理による検出

及び自動的始動テストによって,自動的に検出する。改変を検出した場合,緊急制御動作を行う。

B.4.9 インプットの確認応答

注記 この技術及び手法は,JIS C 0508-2の表A.17及び表A.18で引用されている。

目的:運転中の誤りを,EUCを作動させる前に運転員自身によって検出する。

説明:安全関連系経由のEUCへの入力を,運転員が誤操作を検出して訂正できるように,EUCに送る前

に運転員に送り通知する。システム設計では,異常な,非誘発性の人的動作と同様に,人間の反応

の速度上限又は下限及び方向を考慮することが望ましい。このことによって,例えば,運転員が予

期するよりも速くキーを押し,そのため,システムが2回のキーストロークを1回のキーストロー

クと読み違えたり,システム(ディスプレイ)の最初のキー操作に対する反応が遅すぎて,キーを

2回押してしまったりすることを避ける。重要データの入力の場合,同一キーストロークは,続け

て2回以上のときは有効でないものとすることが望ましい。すなわち,“enter”又は“yes”キーを

何回も押すことによって,システムの危険な動作に至らないようにする必要がある。

運転員が判断することができず,システムを待機させておくこともできない場合のために,多選

択肢をもつ質問(はい,いいえなど)を備えたタイムアウト手順を含むことが望ましい。

安全関連PE系を再起動できるようにする場合は,ソフトウェア及びハードウェアの両方におい

て,再起動を留意して設計しないと,システムを損傷させやすい。

B.5

E/E/PE系の統合

全般:統合フェーズ中の故障を回避し,このフェーズ及び以前のフェーズ中に起こった故障を明らかにす

る。

B.5.1 機能テスト

注記 この技術及び手法は,JIS C 0508-2の表B.3(E/E/PE系の統合中のフォールトを回避するため

の技法及び手段)及び表B.5並びにJIS C 0508-3の表A.5(ソフトウェア設計及び開発−ソフ

トウェアモジュールテスト及び統合),表A.6[プログラマブル電子装置統合(ハードウェア及

38

C 0508-7:2017 (IEC 61508-7:2010)

びソフトウェア)],表A.7(ソフトウェアのシステム安全妥当性確認),表C.5(決定論的安全

度に関する特性−ソフトウェア設計及び開発−ソフトウェアモジュールテスト及び統合),表

C.6[決定論的安全度に関する特性−プログラマブル電子装置の統合(ハードウェア及びソフト

ウェア)]及び表C.7(決定論的安全度に関する特性−システム安全妥当性確認のソフトウェア)

で引用されている。

目的:仕様作成及び設計フェーズ中の故障を明らかにする。実装中及びソフトウェアとハードウェアとの

統合中の故障を回避する。

説明:機能テスト中,システムの規定の特性を達成しているかどうかを確認するために,レビューを実施

する。システムには,通常,期待する動作を十分に特徴付ける入力データを与える。出力を観察し,

出力の応答を,仕様で規定したものと比較する。仕様からの逸脱及び仕様の不完全さの表れを文書

化する。

マルチチャネルアーキテクチャ用として設計した電子構成部品の機能テストには,通常,前もっ

て妥当性確認した対になる構成部品と一緒に製造時にテストした構成部品を含める。さらに,隠さ

れたままになってしまう共通モードフォールトを明らかにするために,構成部品は同じバッチの他

のパートナーとなる構成部品と組み合わせて,製造時にテストすることを推奨する。

さらに,システムの作業容量は,十分とする必要がある。C.5.20を参照する。

参考文献:

Software Testing and Quality Assurance. K. Naik, P. Tripathy, Wiley Interscience, 2008, Print, ISBN:

9780471789116 Online ISBN: 9780470382844

The Art of Software Testing, Second Edition. G. Myers et al., Wiley & Sons, New York, 2004, ISBN

0471469122, 9780471469124

Practical Software Testing: A Process-oriented Approach. I. Burnstein, Springer, 2003, ISBN 0387951318,

9780387951317

Dependability of Critical Computer Systems 3. P. G. Bishop et al., Elsevier Applied Science, 1990, ISBN

1-85166-544-7

B.5.2 ブラックボックステスト

注記 この技術及び手法は,JIS C 0508-2の表B.3,表B.5及び表B.6並びにJIS C 0508-3の表A.5,

表A.6,表A.7,表C.5,表C.6及び表C.7で引用されている。

目的:実際の機能条件の下で動的挙動をチェックする。機能的仕様に適合しないような故障を明らかに

し,有用性及び堅固さを評価する。

説明:システム又はプログラムの機能を,確立した判断基準に従って仕様から系統的に導き出した規定の

テストデータを用いて,規定の環境で実行する。これによって,システムの挙動が明らかになり,

仕様との比較が可能になる。テストを導くに当たって,システムの内部構造についての知識は全く

必要ない。目的は,機能ユニットが,仕様で要求している全ての機能を正しく実施するかどうかを

判定することである。等価クラスを形成する技術は,ブラックボックステストデータのための判定

基準の一例である。入力データ領域は,仕様の助けを借りて,特定の入力値範囲(等価クラス)に

小分割する。その後,テストケースを,次の全ての事項から形成する。

a) 許容範囲からのデータ

b) 非許容範囲からのデータ

39

C 0508-7:2017 (IEC 61508-7:2010)

c) 範囲限界からのデータ

d) 極値

e) a)〜d)の組合せ

様々なテスト活動(モジュールテスト,モジュール統合テスト及びシステムテスト)におけるテ

ストケースを選択するためには,他の判定基準も有効としてもよい。例えば,妥当性確認の枠組み

内のシステムテストの判定基準として,“極端な運用条件”に依拠してもよい。

参考文献:

Software Testing and Quality Assurance. K. Naik, P. Tripathy, Wiley Interscience, 2008, Print, ISBN:

9780471789116 Online ISBN: 9780470382844

Essentials of Software Engineering. Frank F. Tsui, Orlando Karam. Jones & Bartlett, 2006, ISBN 076373537X,

9780763735371

The Art of Software Testing, Second Edition. G. Myers et al., Wiley & Sons, New York, 2004, ISBN

0471469122, 9780471469124

Systematic Software Testing. Rick D. Craig, Stefan P. Jaskiel. Artech House, 2002, ISBN 1580535089,

9781580535083

B.5.3 統計的テスト

注記 この技術及び手法は,JIS C 0508-2の表B.3,表B.5及び表B.6で引用されている。

目的:安全関連系の動的挙動をチェックし,その有用性及び堅固さを評価する。

説明:このアプローチでは,実際の運転上の入力の期待される統計的分布,すなわち,運転プロフィール

に従って選択した入力データを用いて,システム又はプログラムをテストする。

参考文献:

A discussion of statistical testing on a safety-related application. S Kuball, J H R May, Proc. IMechE Vol. 221

Part O: J. Risk and Reliability, Institution of Mechanical Engineers, 2007

Practical Reliability Engineering. P. O'Connor, D. Newton, R. Bromley, John Wiley and Sons, 2002, ISBN

0470844639, 9780470844632

Dependability of Critical Computer Systems 3. P. G. Bishop et al., Elsevier Applied Science, 1990, ISBN

1-85166-544-7

Dependability of Critical Computer Systems 1. F. J. Redmill, Elsevier Applied Science, 1988, ISBN

1-85166-203-0

B.5.4 フィールドの実績

注記1 この技術及び手法は,JIS C 0508-2の表B.3,表B.5及び表B.6で引用されている。

注記2 同様な手法はC.2.10,確率的アプローチは附属書Dを参照。ただし,両方ともソフトウェア

面に関するものである。

目的:別のアプリケーションによるフィールドの実績を,E/E/PE系統合時及び/又はE/E/PE系安全妥当

性確認時のフォールトを回避するための手法の一つとして用いる。

説明:多数の異なるアプリケーションにおいて,十分な期間にわたって,全く故障が起こらないか,又は

重要でないフォールトしか起こらないことが実績によって示されていて,本質的な変更をしていな

い構成部品又はサブシステムを用いる。特に,多数の実行可能な機能をもつ複雑な構成部品(例え

40

C 0508-7:2017 (IEC 61508-7:2010)

ば,オペレーティングシステム,集積回路)の場合,開発者は,どの機能がフィールドの実績によ

って実際にテストされているかに注意する必要がある。例えば,フォールト検出のための自己テス

トの通常手順を考慮する。運用期間中にハードウェアの故障が全く起こらない場合は,通常手順は,

そのフォールト検出機能を一度も実行しなかったことになるため,その手順は(実際に)試された

ということにはならない。

フィールドの実績を適用するためには,次の要求事項を満たす必要がある。

− 変更されていない仕様

− 10システムの異なるアプリケーションでの運用実績

− 105時間の運用実績及び1年間以上の使用履歴

注記3 適用分野規格では,これと異なる数値を規定していることがある。

フィールドの実績は,ベンダー及び/又は運用会社の文書類によって実証される。この文書類は,

少なくとも,次の内容を含む必要がある。

− ハードウェアのバージョン管理も含め,システム及びその構成部品の正しい呼び方

− 使用者及び適用時間

− 運用時間

− 証明のために調達されたシステム及びアプリケーションの選定手順

− フォールト検出及びフォールト登録並びにフォールト除去の手順

参考文献:

JIS C 5750-3-2:2008 ディペンダビリティ管理−第3-2部:適用の指針−フィールドからのディペンダ

ビリティデータの収集

注記 対応国際規格:IEC 60300-3-2:2004,Dependability management−Part 3-2: Application guide−

Collection of dependability data from the field

Guidelines for Safe Automation of Chemical Processes. CCPS, AIChE, New York, 1993, ISBN-10:

0-8169-0554-1, ISBN-13: 978-0-8169-0554-6

B.6

E/E/PE系の安全妥当性確認

全般:E/E/PE安全関連系が,E/E/PE系の安全要求仕様及びE/E/PE系設計要求仕様に適合していることを

証明する。

B.6.1 環境条件の下での機能テスト

注記 この技術及び手法は,JIS C 0508-2の表B.5で引用されている。

目的:安全関連系が,典型的な環境による影響に対して保護されているかどうかを評価する。

説明:システムを様々な環境条件(例えば,JIS C 60068の規格群又はIEC 61000の規格群の規格に従う。)

に置き,安全機能の信頼性(及び上記規格との両立性)について評価する。

参考文献:

JIS C 60068-1 環境試験方法−電気・電子−通則及び指針

注記 対応国際規格:IEC 60068-1:1988,Environmental testing−Part 1: General and guidance及び

Amendment 1 (1992)

IEC 61000-4-1:2006,Electromagnetic compatibility (EMC)−Part 4-1: Testing and measurement techniques−

Overview of IEC 61000-4 series

41

C 0508-7:2017 (IEC 61508-7:2010)

Dependability of Critical Computer Systems 3. P. G. Bishop et al., Elsevier Applied Science, 1990, ISBN

1-85166-544-7

B.6.2 サージイミュニティのテスト

注記 この技術及び手法は,JIS C 0508-2の表B.5及び表B.6で引用されている。

目的:安全関連系のピークサージ受容力をチェックする。

説明:システムに典型的なアプリケーションプログラムをロードし,全ての周辺線路(デジタルインタフ

ェース,アナログインタフェース,シリアルインタフェース,バス接続,電源など)に,標準ノイ

ズ信号を与える。定量的に示すために,サージ限界に注意深く近づけることが大切である。機能が

失敗した場合は,選択したクラスのノイズに適合していないということになる。

参考文献:

JIS C 61000-4-5:2009 電磁両立性−第4-5部:試験及び測定技術−サージイミュニティ試験

注記 対応国際規格:IEC 61000-4-5:2005,Electromagnetic compatibility (EMC)−Part 4-5: Testing and

measurement techniques−Surge immunity test

C37.90.1-2002,IEEE Standard for Surge Withstand Capability (SWC) Tests for Relays and Relay Systems

Associated with Electric Power Apparatus

B.6.3 (不使用)

B.6.4 静的解析

注記 この技術及び手法は,JIS C 0508-2の表B.5及び表B.6並びにJIS C 0508-3の表A.9(ソフトウ

ェア適合確認),表B.8,表C.9(決定論的安全度に関する特性−ソフトウェア適合確認)及び

表C.18で引用されている。

目的:テスト対象のシステムにおいて,故障に至る可能性がある決定論的原因フォールトを,運用の初期

又は何年にもわたる運用の後のいずれかにおいて,回避する。

説明:この系統的で,コンピュータ支援が可能なアプローチでは,問題とする要求事項(例えば,構造指

針,システム仕様及び機器データシート)に関し,確実に完全性及び一貫性があって,曖昧さがな

いようにするために,プロトタイプシステムの具体的な静特性を検査する。静的解析には,再現性

がある。静的解析は,十分に定義された完成段階に到達したプロトタイプに適用する。ハードウェ

ア及びソフトウェアに関する静的解析には,次の事例がある。

− データフローの一貫性解析(例えば,データオブジェクトが,あらゆる場所において同じ値と

して解釈されるかどうかのテスト)

− 制御フロー解析(例えば,経路の決定,アクセス不能コードの決定)

− インタフェース解析(例えば,様々なソフトウェアモジュール間の変数伝送の調査)

− 変数の作成,参照,削除など,疑わしいシーケンスを検出するデータフロー解析

− テストが個々の指針(例えば,沿面距離及び空間距離,組立距離,物理的装置の配置,機械的

な影響を受けやすい物理的装置,導入実績がある物理的装置だけの使用)に従っている。

参考文献:

Static Analysis and Software Assurance. D. Wagner, Lecture Notes in Computer Science, Volume 2126/2001,

Springer, 2001, ISBN 978-3-540-42314-0

42

C 0508-7:2017 (IEC 61508-7:2010)

An Industrial Perspective on Static Analysis. B A Wichmann, A A Canning, D L Clutterbuck, L A Winsborrow,

N J Ward and D W R Marsh. Software Engineering Journal., 69-75, March 1995

Dependability of Critical Computer Systems 3. P. G. Bishop et al,. Elsevier Applied Science, 1990, ISBN

1-85166-544-7

B.6.5 動的解析及びテスト

注記 この技術及び手法は,JIS C 0508-2の表B.5及び表B.6並びにJIS C 0508-3の表A.5,表A.9,

表B.2(動的解析及び動的テスト),表C.5,表C.9及び表C.12(詳細特性−動的解析及びテス

ト)で引用されている。

目的:完成度の進んだ状態におけるプロトタイプの動的挙動を検査することによって,仕様機能の失敗を

検出する。

説明:安全関連系の動的解析は,意図した運用環境の典型的な入力データを,運用可能な状態に近い安全

関連系プロトタイプに用いることによって実施する。安全関連系において観察した挙動が,要求す

る挙動に適合する場合,解析は満足できるものといえる。安全関連系に故障がある場合,修正して,

その後,新しい運用バージョンを再解析する必要がある。

参考文献:

The Concept of Dynamic Analysis. T. Ball, ESEC/FSE ʼ99, Lecture Notes in Computer Science, Springer, 1999,

ISBN 978-3-540-66538-0

Dependability of Critical Computer Systems 3. P. G. Bishop et al,. Elsevier Applied Science, 1990, ISBN

1-85166-544-7

B.6.6 故障解析

注記 この技術及び手法は,JIS C 0508-2の表B.5及び表B.6で引用されている。

B.6.6.1 故障モード及び影響解析(FMEA)

目的:システムの構成部品の考えられる全ての故障源を系統的に調査し,システムの挙動及び安全性に対

するこれらの故障の影響を求めることによって,システム設計を解析する。

説明:解析は,通常,技術者が集まって行う。システムの各構成部品を順次解析して,その構成部品につ

いての一連の故障モード,これらの原因及び影響(局所的及びシステム全体の水準),検出手順並

びに推奨事項を定める。推奨事項に従って行動する場合,推奨事項を,実施する是正処置として文

書化する。

参考文献:

JIS C 5750-4-3:2011 ディペンダビリティ マネジメント−第4-3部:システム信頼性のための解析技

法−故障モード・影響解析(FMEA)の手順

注記 対応国際規格:IEC 60812:2006,Analysis techniques for system reliability−Procedure for failure

mode and effects analysis (FMEA)

Risk Assessment and Risk Management for the Chemical Process Industry. H.R. Greenberg, J.J. Cramer, John

Wiley and Sons, 1991, ISBN 0471288829, 9780471288824

Reliability Technology. A. E. Green, A. J. Bourne, Wiley-Interscience, 1972, ISBN 0471324809

43

C 0508-7:2017 (IEC 61508-7:2010)

B.6.6.2 原因結果図(因果解析)

注記 この技術及び手法は,JIS C 0508-3の表B.3(機能テスト及びブラックボックステスト),表B.4

(故障分析),表C.13(詳細特性−機能及びブラックボックステスト)及び表C.14(詳細特性

−故障分析)で引用されている。

目的:基本事象の組合せの結果としてシステム内で発展する可能性がある事象のシーケンスを,コンパク

トな図式の形で解析しモデル化する。

説明:この技術は,フォールトの木解析と事象の木解析との組合せとしてみなすことができる。重要(起

因)事象から始めて,何らかの動作の成功及び失敗を記述するYES/NOゲートを用いて,因果グラ

フを前方向にトレースしていく。これによって,事故又は克服した状況のいずれかに導く事象シー

ケンスを構築することができる。次に,各故障について因果グラフ(すなわち,フォールトの木)

を作成する。さらに,事故的状況から出発して,後方向に戻り,この事故を最上位事象とするグロ

ーバルフォールトの木を作成する。前方向では,事象から起こる可能性がある結果が求められる。

グラフは,頂点からの幾つかの支線に沿う,伝ぱ(播)のための条件を記述する頂点記号を含むこ

とができる。さらに,時間遅延も含むことができる。これらの条件は,フォールトの木を用いて説

明することもできる。図式を更に簡潔なものにするために,伝ぱ(播)の線を論理記号と組み合わ

せることができる。因果図で使用のための一連の標準記号を定義する。これらの図式は,フォール

トの木を作成するために,及びある重要な結果が起こる確率を計算するために用いることができる。

事象の木を作成するためにも用いることができる。

参考文献:

IEC 62502,Analysis techniques for dependability−Event tree analysis (ETA)

The Cause Consequence Diagram Method as a Basis for Quantitative Accident Analysis. B. S. Nielsen, Danish

Atomic Energy Commission, Riso-M-1374, 1971

B.6.6.3 事象の木解析(ETA)

注記 この技術及び手法は,JIS C 0508-3の表B.4及び表C.14で引用されている。

目的:起因事象後にシステム内で進展する可能性がある事象のシーケンスを,図式の形でモデル化し,こ

れによって,重大な結果がどのように起こるかを示す。事象の木を何もないところから構築するこ

とは難しく,因果図を用いると役に立つ。

説明:図式の頂点において,起因事象の後に続く事象の進展に関わるシーケンス条件を書く。解析の到達

目標である起因事象の下から線を描き始め,シーケンスの最初の条件まで描く。そこで,図式は“は

い”及び“いいえ”の枝に分岐し,将来の事象が,条件によってどのように決まるかを記述する。

これらの枝のそれぞれについて,同様の方法で次の条件に続ける。ただし,全ての条件が,全ての

枝に関係があるとは限らない。一つの枝はシーケンスの終端まで継続し,このように構成した木の

各枝には,起こる可能性がある結果を表す。シーケンス内の条件が独立している場合,事象の木は,

シーケンス内の条件の確率及び条件数を基に,様々な結果の確率を計算するために用いることがで

きる。条件が100 %独立していることはめったにないので,こうした計算は慎重に検討し,熟練し

た解析者が実施する必要がある。

参考文献:

IEC 62502,Analysis techniques for dependability−Event tree analysis (ETA)

Risk Assessment and Risk Management for the Chemical Process Industry. H.R. Greenberg, J.J. Cramer, John

44

C 0508-7:2017 (IEC 61508-7:2010)

Wiley and Sons, 1991, ISBN 0471288829, 9780471288824

B.6.6.4 故障モード影響及び致命度解析(FMECA)

注記 この技術及び手法は,JIS C 0508-3の表A.10,表B.4,表C.10及び表C.14で引用されている。

目的:どの構成部品が設計又は運転中に特別な注意及び適切な管理手段を必要とするかを決めるために,

単一故障が傷害,損傷又はシステム劣化に結び付く可能性がある構成部品の致命度のランク付けを

する。

説明:この手法はFMEAに類似するものであるが,致命度を示すための欄は一つ又は複数あり,多くの方

法でランク付けすることができる。最も労力を必要とする手法は,米国自動車技術者協会(SAE)

の規格,ARP 926に記載されている。この手順において,構成部品の致命度数は,クリティカルモ

ードにおける各100万回の運転中に予期される,特定の種類の故障の数によって示される。致命度

数は,九つのパラメータの関数であり,これらのパラメータの大半は,測定する必要がある。致命

度を求めるための非常に簡単な手法は,構成部品故障の確率に,発生する可能性がある損害を乗じ

る方法であり,この手法は,単純なリスク要因評価に似ている。

参考文献:

JIS C 5750-4-3:2011 ディペンダビリティ マネジメント−第4-3部:システム信頼性のための解析技

法−故障モード・影響解析(FMEA)の手順

注記 対応国際規格:IEC 60812:2006,Analysis techniques for system reliability−Procedure for failure

mode and effects analysis (FMEA)

Software criticality analysis of COTS/SOUP. P. Bishop, T. Clement, S. Guerra. In Reliability Engineering &

System Safety, Volume 81, Issue 3, September 2003, Elsevier Ltd., 2003

Software FMEA techniques. P.L.Goddard. In Proc Annual 2000 Reliability and Maintainability Symposium,

IEEE, 2000, ISBN: 0-7803-5848-1

B.6.6.5 フォールトの木解析(FTA)

注記 この技術及び手法は,JIS C 0508-3の表B.4及び表C.14で引用されている。

目的:潜在危険若しくは重大な結果に至る事象,又はこれらの事象の組合せを解析する手助けをし,最上

位事象の確率計算をする。

説明:潜在危険又は重大な結果の直接的な原因となる可能性がある事象(“最上位事象”)から始め,その

原因を特定するために解析を実施する。この解析は,論理演算子(and,orなど)を用いて,数ス

テップを経て行う。中間原因についても同様に解析を進め,基本事象に戻って解析を停止する。

この手法は,図表を使うもので,フォールトの木を描くために標準化されている記号を用いる。

解析の終了時,フォールトの木は,基本事象(一般に,構成部品の故障)を最上位事象(全体シス

テムの故障)にリンクさせる論理的機能を表す。この技術は,主として,ハードウェアシステムの

解析のためのものであるが,このアプローチをソフトウェア故障解析に適用する試みもなされてい

る。この技術は,定性的には故障解析のために(故障シナリオの同定:ミニマル カットセット又は

プライム インプリカント),半定量的に(確率によるランキングシナリオによって)及び定量的に

は,最上位事象の確率計算をするために,用いることができる(C.6参照)。

参考文献:

JIS C 5750-4-4:2011 ディペンダビリティ マネジメント−第4-4部:システム信頼性のための解析技

45

C 0508-7:2017 (IEC 61508-7:2010)

法−故障の木解析(FTA)

注記 対応国際規格:IEC 61025:2006,Fault tree analysis (FTA)

From safety analysis to software requirements. K.M. Hansen, A.P. Ravn, A.P, V Stavridou. IEEE Trans Software

Engineering, Volume 24, Issue 7, Jul 1998

B.6.6.6 マルコフモデル

注記 ハードウェア安全度を解析するために,信頼性ブロック図に対してこの技術を用いる場合は,

IEC 61508-6のB.1を参照。

目的:状態遷移図によってシステムの挙動をモデル化し,確率論的システムパラメータ(例えば,非信頼

性,非可用性,MTTF,MUT,MDTなど)を評価する。

説明:これは,直接,図表で表した有限状態オートマトン(B.2.3.2参照)である。ノード(円)は状態を

表し,ノード間のエッジ(矢印)は状態間で発生した遷移(故障,修理など)を表す。エッジは,

対応する故障率又は修理率で重み付けする。一様マルコフ過程の基本特性は,未来が現在によって

だけ左右されることである。状態Nからこれに続く状態N+1に左右されるが,これ以前の状態N-1

からは独立している。このことは,モデルの全ての確率論的法則が指数関数的であることを暗示し

ている。

故障事象,故障状態及び故障率は,システムの精細な記述ができるような方法で詳述できる。例

えば,検出又は未検出故障,より大きな故障の発現などである。プルーフテストの間隔は,一つの

フェーズの終了時(例えば,プルーフテスト直前)の状態の確率を用いて,次のフェーズの初期状

態(例えば,プルーフテスト完了後の各種状態の確率)を計算できる,いわゆるマルチフェーズマ

ルコフ過程を用いて適切にモデル化してもよい。

マルコフ技術は,構成部品の故障及び修理によって,冗長性の水準が時間とともに変動する多重

システムのモデル化に適している。その他の古典的手法(例えば,FMEA,FTAなど)は,対応す

る確率を計算するための単純な組合せ公式がないので,システムのライフサイクル全体にわたる故

障の影響をモデル化するために,そのまま適用することができない。

最も単純な事例では,システムの確率を記述する形式を文献で簡単に見つけるか,又は手作業で

計算することができ,より複雑な事例を処理するための簡易化手法(すなわち,状態数を減らす方

法)も幾つかある。

いずれの場合も,数学的に,一様マルコフ図は,一定係数をもつ線形微分方程式の単純かつ共通

集合にすぎない。このことは長い間解析され,強力なアルゴリズムが開発されており,これらの式

を処理するために利用されている。したがって,モデルのサイズが増えた場合,各種コンピュータ

ソフトウェアパッケージに実装されている上記アルゴリズムを用いると,効率がよくなる。

図のサイズは,構成部品の個数に合わせて指数関数的に増加する。これは,いわゆる組合せ的爆

発である。したがって,この技術は,小さなシステムの場合に限り,近似化せずに利用できる。

非指数関数的法則を取り扱う場合(半マルコフモデル),モンテカルロシミュレーション(B.6.6.8

参照)を用いることが望ましい。

参考文献:

IEC 61165:2006,Application of Markov techniques

The Theory of Stochastic Processes. R. E. Cox and H. D. Miller, Methuen and Co. Ltd., London, UK, 1963

Finite MARKOV Chains. J. G. Kemeny and J. L. Snell. D. Van Nostrand Company Inc, Princeton, 1959

46

C 0508-7:2017 (IEC 61508-7:2010)

The Theory and Practice of Reliable System Design. D. P. Siewiorek and R. S. Swarz, Digital Press, 1982

Sécurisation des architectures informatiques. Jean-Louis Boulanger, Hermès−Lavoisier, 2009, ISBN:

978-2-7462-1991-5

B.6.6.7 信頼性ブロック図(RBD)

注記1 この技術及び手法は,IEC 61508-6の附属書Bで用いられている。

注記2 C.6.4も参照。

目的:システム又は業務の運用に成功するために,発生しなければならない事象と満足されなければなら

ない条件との組合せを,図式的な形でモデル化する。これは解析手法というよりは,表現手法であ

る。

説明:解析の目標を,ブロック,ライン及び論理的接合部からなる成果経路として表す。成果経路は,図

式の一方の側から出発し,ブロック及び接合部を経由して,図式の反対側まで続く。ブロックは条

件又は事象であり,経路は,条件が真である場合又は事象が発生した場合,ブロックを通過する。

経路が接合部に達し,接合部のロジックを満たした場合,先を続ける。頂点に達した場合,全ての

引出線に沿って進んでもよい。図式を1本以上の成果経路が通過している場合,解析目標は適切に

動作している。

RBDは,モデル化されたシステムの構造的表現である。これは,一種の電気回路といえる。つま

り,電流が入力から出力に流れる経路が見つかることは,モデル化されたシステムが適切に動作し

ていることを示しており,回路が遮断された場合は,モデル化されたシステムが故障したことを示

す。このことから,モデル化されたシステムの故障を引き起こす各故障(すなわち,RBDが“遮断”

されている場所)の組合せを表す,最小限の遮断セット(ミニマル カットセット)という概念が生

まれる。

数学的には,RBDはフォールトの木に似ている。これは,(故障しているか又は動作しているか

の)個別の構成部品の状態を,(故障しているか又は動作しているかの)システム全体に連結する論

理的機能を表す。したがって,計算は,フォールトの木について説明したものに類似している。

参考文献:

IEC 61078:2006,Analysis techniques for dependability−Reliability block diagram and boolean methods

Sécurisation des architectures informatiques. Jean-Louis Boulanger, Hermès−Lavoisier, 2009, ISBN:

978-2-7462-1991-5

B.6.6.8 モンテカルロシミュレーション

注記 この技術及び手法は,IEC 61508-6の附属書Bで用いられている。

目的:解析手法が実用可能でない場合に,乱数を発生させて実世界現象をシミュレーションする。

説明:モンテカルロシミュレーションは,次の2種類の問題点を解決するために用いる。

− 確率論的。乱数を確率論的現象の発生に利用する。

− 決定論的。数学的に,等価の確率論的問題(例えば,積分計算)に転換する。

モンテカルロシミュレーションの原理は,乱数を用いて,検討対象のシステムの挙動上の機能的

及び非機能的モデルをアニメーション化することにある。こうした挙動モデルは,状態遷移モデル

(マルコフ図,ペトリネット,形式言語など)によって与えられる。モンテカルロシミュレーショ

ンは,統計的結果を導き出すための大きな統計的サンプルを生成するために実行する。